HW #5 Solution

Note: Different implementations of 3&4 are possible.

1.

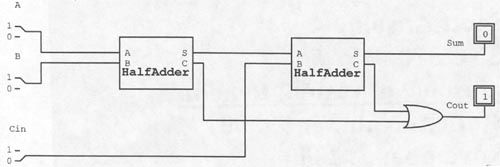

Part a) Half Adder

Part b) Full Adder using Half Adder Blocks

Part c) Full Adder Gate Design

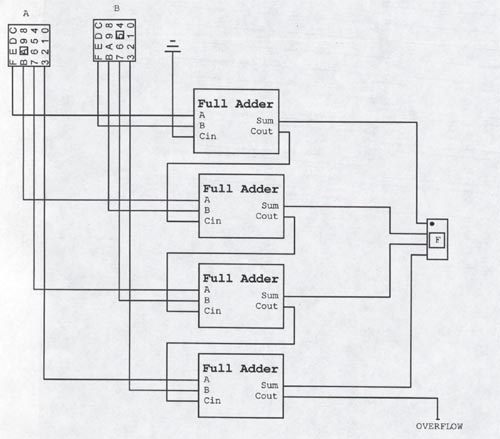

2.

4 bit adder using Full adder blocks from #1.

When you add 1111 and 0000, then

change 0000->0001 it causes a carry to be

propagated through all of the full adders, causing the delay of each

sum bit to be progressively delayed proportional to the number of adders the

carry must pass through. When 1010 is added to 0000 and 0000-> 0101 the

output will stabilize more quickly as the carry bit is not changing and

therefore the propagation of the carry is not detected.

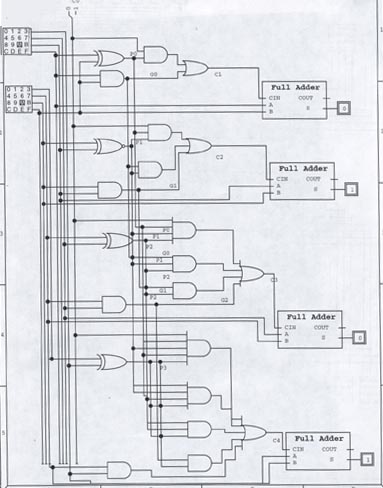

3.

4 bit Carry Lookahead Adder

Gate comparision w/ #2.

Lookahead Adder - 58 gates

Ripple Carry Adder - 36 gates

Gate Delays (worst case)

Lookahead Adder - 4 gates

Ripple Carry Adder - 8 gates

Note however, that as the number of bits added grows, the ripple

carry adder's delay will grow as well, while

the delay of the lookahead adder will remain constant.

4.

8 bit unsigned Carry Select Adder