Homework 6 Solutions

1.

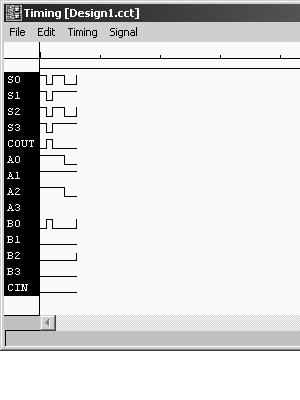

module Add(A0, A1, A2, A3, B0, B1, B2, B3, CIN, S0, S1, S2, S3, COUT);

input A0;

input A1;

input A2;

input A3;

input B0;

input B1;

input B2;

input B3;

input CIN;

output S0;

output S1;

output S2;

output S3;

output COUT;

reg [4:0]A;

reg [4:0]B;

reg [4:0]Add;

assign A = {1'b0, A3, A2, A1, A0};

assign B = {1'b0, B3, B2, B1, B0};

assign Add = A + B + CIN;

assign COUT = Add[4];

assign S3 = Add[3];

assign S2 = Add[2];

assign S1 = Add[1];

assign S0 = Add[0];

endmodule

2.

Katz, 6.10 (b): The output of the J-K flip-flop changes with the positive edge of the clock as described below. The waveform goes high at the first clock pulse and remains there till the beginning of the fourth clock pulse when it goes down low and remains low for the rest of the clock pulses shown in the figure.

Katz, 6.10 (c): The output of the J-K flip-flop changes with the negative edge of the clock as described below. The waveform goes high at the end of the third clock pulse and goes low again at the end of the end of the fourth clock pulse. It goes high again at the end of the 6 th clock pulse which is the last clock pulse shown in the figure.

3.

(a) False, because the inputs on a level sensitive latch are sampled only when the clock is high.

(b) False, because the propagation time for edge-triggered flip-flops is much longer than the hold time.

(c) True, because latches continuously sample inputs while the clock is high, whereas flip-flops sample either at the rise or fall of the clock.

(d) False, because the master-slave flip-flop's outputs change after the falling edge.

(e) False, because a master-slave flip-flop has 9 gates while D flip-flop has only 6 gates.

4.

5. Register Sub-Circuit Internals

Created by: Krishna Gummadi