Homework 7 Solution

1.

module GrayCodeCounter(CLK, EN, RESET, Q2, Q1, Q0);

input CLK, EN, RESET;

output Q2, Q1, Q0;

reg Q2, Q1, Q0;

req [2:0]state;

'define s0 3'b000

'define s1 3'b001

'define s2 3'b010

'define s3 3'b011

'define s4 3'b100

'define s5 3'b101

'define s6 3'b110

'define s7 3'b111

assign Q0 = state[0];

assign Q1 = state[1];

assign Q2 = state[2];

always @(posedge CLK) begin

if(RESET)

state = 's0;

else if(EN)

case(state)

's0: state = 's1;

's1: state = 's2;

's2: state = 's3;

's3: state = 's4;

's4: state = 's5;

's5: state = 's6;

's6: state = 's7;

's7: state = 's0;

endcase

end

endmodule

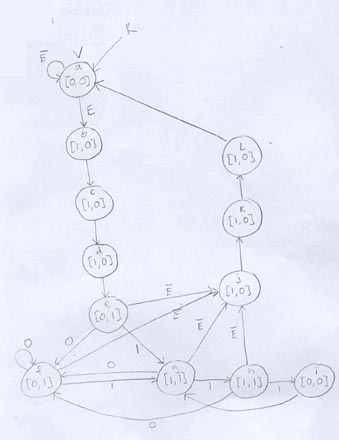

2.

3a.

3b. Verilog Code - 3bsol.txt

3c.