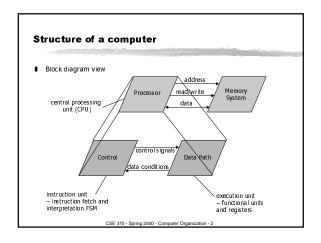

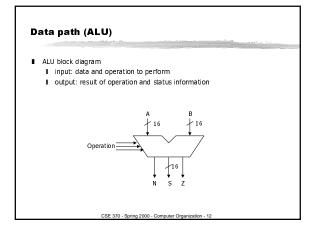

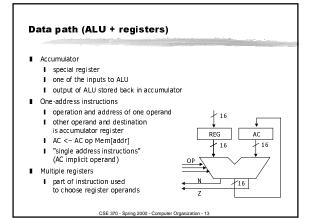

## Computer organization Computer design – an application of digital logic design procedures Computer = processing unit + memory system Processing unit = control + datapath Control = finite state machine inputs = machine instruction, datapath conditions outputs = register transfer control signals, ALU operation codes instruction interpretation = instruction fetch, decode, execute Datapath = functional units + registers functional units = ALU, multipliers, dividers, etc. registers = program counter, shifters, storage registers

CSE 370 - Spring 2000 - Computer Organization - 1

## Instruction sequencing

- Example an instruction to add the contents of two registers (Rx and Ry) and place result in a third register (Rz)

- $\blacksquare \quad \text{Step 1: get the ADD instruction from memory into an instruction register}$

- Step 2: decode instruction

- instruction in IR has the code of an ADD instruction

- $\hbox{\bf I} \quad \hbox{register indices used to generate output enables for registers Rx and Ry}$

- ${\rm I\hspace{-.07cm}I}$  register index used to generate load signal for register Rz

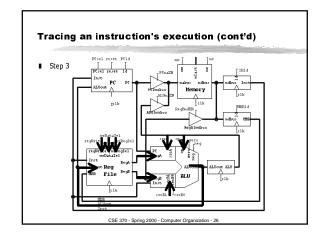

- Step 3: execute instruction

- enable Rx and Ry output and direct to ALU

- I setup ALU to perform ADD operation

- I direct result to Rz so that it can be loaded into register

CSE 370 - Spring 2000 - Computer Organization - 7

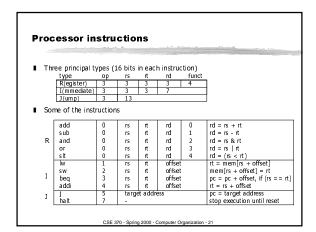

## Instruction types

- Data manipulation

- add, subtract

- I increment, decrement

- I multiply

- ${\rm I\hspace{-.1em}I} \hspace{.1em} {\rm shift, \, rotate}$

- I immediate operands

- Data staging

- I load/store data to/from memory

- register-to-register move

- - I conditional/unconditional branches in program flow

- I subroutine call and return

CSE 370 - Spring 2000 - Computer Organization - 8

## Elements of the control unit (aka instruction unit)

- Standard FSM elements

- state register

- output logic (datapath/control signalling)

- I Moore or synchronous Mealy machine to avoid loops unbroken by FF

- Plus additional "control" registers

- I instruction register (IR)

- program counter (PC)

- Inputs/outputs

- I outputs control elements of data path

- I inputs from data path used to alter flow of program (test if zero)

CSE 370 - Spring 2000 - Computer Organization - 9

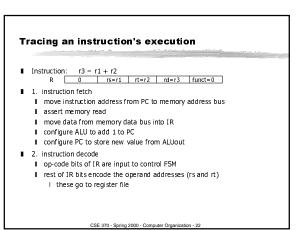

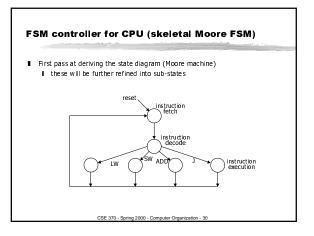

## Instruction execution ■ Control state diagram (for each diagram) I reset ■ fetch instruction I decode Initialize Machine ■ execute ■ Instructions partitioned into three classes ■ branch ■ load/store ■ register-to-register ■ Different sequence through diagram for each instruction type

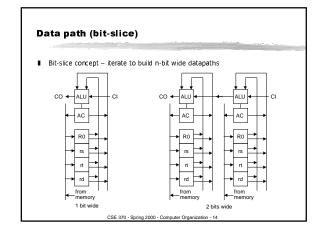

## Data path (heirarchy) ■ Arithmetic circuits constructed in hierarchical and iterative fashion I each bit in datapath is functionally identical ■ 4-bit, 8-bit, 16-bit, 32-bit datapaths FA Cout CSE 370 - Sp

## Instruction path

- Program counter

- l keeps track of program execution

- I address of next instruction to read from memory

- may have auto-increment feature or use ALU

- Instruction register

- I current instruction

- includes ALU operation and address of operand

- I also holds target of jump instruction

- I immediate operands

- Relationship to data path

- PC may be incremented through ALU

- contents of IR may also be required as input to ALU

CSE 370 - Spring 2000 - Computer Organization - 15

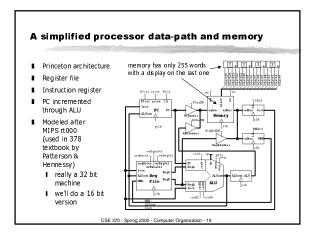

## Data path (memory interface)

- Memory

- I separate data and instruction memory (Harvard architecture)

- I two address busses, two data busses

- I single combined memory (Princeton architecture)

- I single address bus, single data bus

- Separate memory

- ALU output goes to data memory input

- ${\rm I\hspace{-.1em}I\hspace{-.1em}register\;input\;from\;data\;memory\;output}$

- I data memory address from instruction register

- ${\rm I\hspace{-.1em}I} \hspace{.1em} \text{instruction register from instruction memory output}$

- I instruction memory address from program counter

- Single memory

- address from PC or IR

- I memory output to instruction and data registers

- I memory input from ALU output

CSE 370 - Spring 2000 - Computer Organization - 1

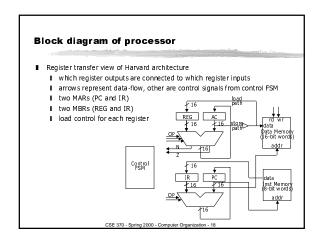

# Block diagram of processor I Register transfer view of Princeton architecture I which register outputs are connected to which register inputs I arrows represent data-flow, other are control signals from control FSM I MAR may be a simple multiplexer rather than separate register I MBR is split in two (REG and IR) I load control for each register Option Action Control (action words) I load control for each register Option Action Control (action words) I load control for each register Option Action Control (action words) I load control for each register Option Control (action words)

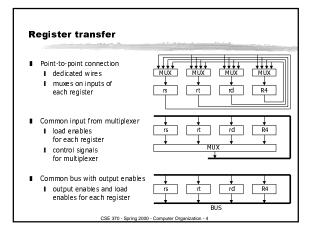

## Register-transfer-level description

- I transfer data between registers by asserting appropriate control signals

- Register transfer notation work from register to register

- I instruction fetch: mabus ← PC;

- move PC to memory address bus (PCmaEN, ALUmaEN)

- mauus ← PC; move PC to memory address bus (PC maen, ALUmlaen)

memory read; assert memory read signal (mr, Reg@mdEn)

IR ← memory; load IR from memory data bus (IRId)

send PC into A linput, 1 into B liput, add

(srCA, srcB0, scrB1, op)

PC ← ALUout load result of incrementing in ALU into PC (PCId, PCsel)

- I instruction decode:

- IR to controller values of A and B read from register file (rs, rt)

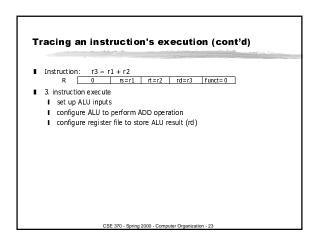

- I instruction execution:

- nr:

send regA into A input, regB into B input, add

(srcA, srcB0, scrB1, op)

store result of add into destination register

(regWrite, wrDataSel, wrRegSel)  $op \leftarrow add$

## Register-transfer-level description (cont'd)

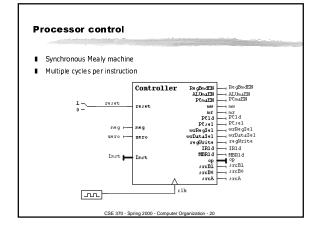

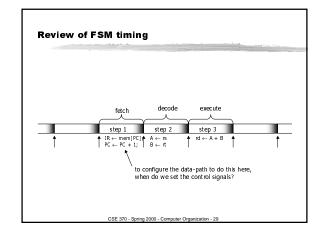

- How many states are needed to accomplish these transfers?

- data dependencies (where do values that are needed come from?)

- I resource conflicts (ALU, busses, etc.)

- In our case, it takes three cycles

- I one for each step

- all operation within a cycle occur between rising edges of the clock

- How do we set all of the control signals to be output by the state machine?

- I depends on the type of machine (Mealy, Moore, synchronous Mealy)

CSE 370 - Spring 2000 - Computer Organization - 28

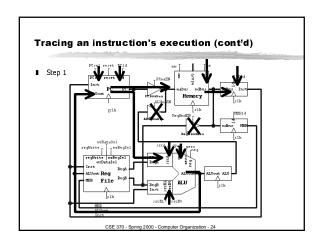

## FSM controller for CPU (reset and inst. fetch)

- Assume Moore machine

- I outputs associated with states rather than arcs

- Reset state and instruction fetch sequence

- On reset (go to Fetch state)

- I start fetching instructions

- PC will set itself to zero

$\label{eq:pc} \begin{array}{l} \text{mabus} \leftarrow \text{PC}\,;\\ \text{memory read};\\ \text{IR} \leftarrow \text{memory data bus};\\ \text{PC} \leftarrow \text{PC} + 1; \end{array}$

CSE 370 - Spring 2000 - Computer Organization - 31

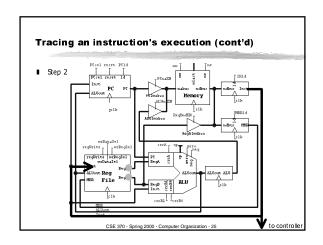

## FSM controller for CPU (decode)

- Operation decode state

- I next state branch based on operation code in instruction

- $\hbox{\bf I} \quad \text{read two operands out of register file} \quad$

- I what if the instruction doesn't have two operands?

CSE 370 - Spring 2000 - Computer Organization - 32

## FSM controller for CPU (instruction execution)

- For add instruction

- I configure ALU and store result in register

$rd \leftarrow A + E$

$\hbox{\bf I} \quad \hbox{other instructions may require multiple cycles}$

CSE 370 - Spring 2000 - Computer Organization - 33

## FSM controller for CPU (add instruction)

■ Putting it all together and closing the loop

I the famous instruction fetch decode execute

cycle

CSE 370 - Spring 2000 - Computer Organization - 34

## FSM controller for CPU

- Now we need to repeat this for all the instructions of our processor

- I fetch and decode states stay the same

- I different execution states for each instruction

- I some may require multiple states if available register transfer paths require sequencing of steps

CSE 370 - Spring 2000 - Computer Organization - 35