### Combinational logic

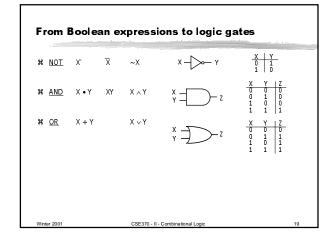

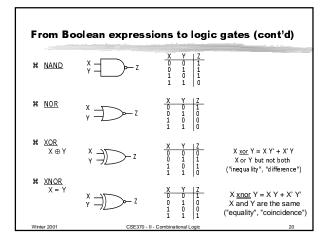

☐ Boolean algebra, proofs by re-writing, proofs by perfect induction ☐ Logic functions, truth tables, and switches ☑ NOT, AND, OR, NAND, NOR, XOR, . . . , minimal set

₩ Logic realization

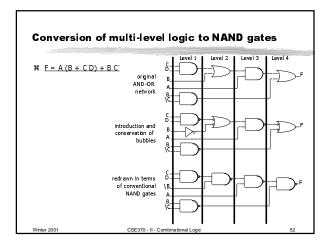

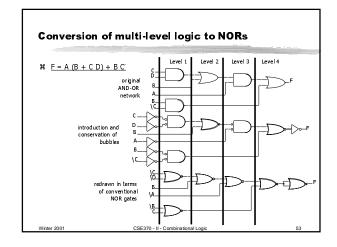

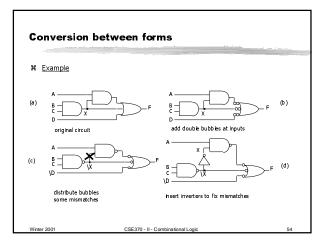

□ two-level logic and canonical forms, incompletely specified functions

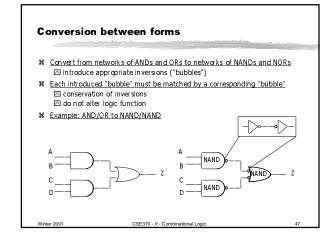

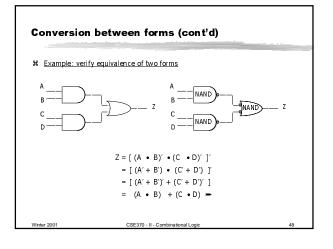

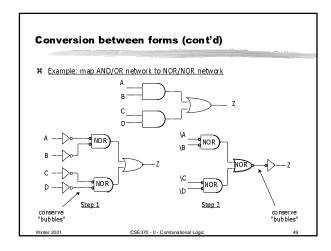

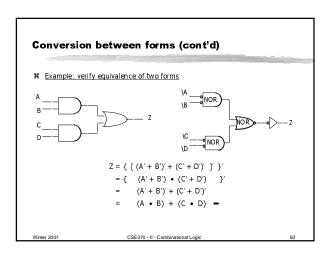

□ multi-level logic, converting between ANDs and ORs

¥ <u>Simplification</u>

□ uniting theorem

☐ transformations on networks of Boolean functions

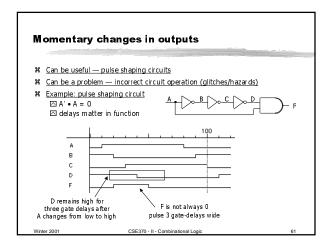

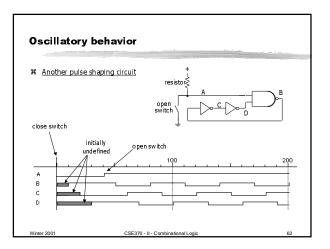

# Time behavior

# Time behavior

# Hardware description languages

CSE370 - II - Combinational Logi

## Possible logic functions of two variables # There are 16 possible functions of 2 input variables: # There are 16 possible functions of 2 input variables: # There are 16 possible functions of 2 input variables: # There are 16 possible functions of 2 input variables: # There are 16 possible functions of 2 input variables: # There are 16 possible functions of 2 input variables: # There are 16 possible functions of 2 input variables: # There are 16 possible functions of 2 input variables: # There are 16 possible functions of 2 input variables: # There are 16 possible functions of 2 input variables: # There are 16 possible functions of 2 input variables: # There are 16 possible functions of 2 input variables: # The Possible function function functions of 2 input variables: # The Possible function function

CSE370 - II - Combinational Logi

### Cost of different logic functions

# Different functions are easier or harder to implement

☐ each has a cost associated with the number of switches needed

△ 0 (F0) and 1 (F15): require 0 switches, directly connect output to low/high

△ X (F3) and Y (F5): require 0 switches, output is one of inputs

☐ X' (F12) and Y' (F10): require 2 switches for "inverter" or NOT-gate ☐ X nor Y (F4) and X nand Y (F14): require 4 switches

△ X or Y (F7) and X and Y (F1): require 6 switches

$\triangle$  X = Y (F9) and X  $\oplus$  Y (F6): require 16 switches

☐ thus, because NOT, NOR, and NAND are the cheapest they are the

functions we implement the most in practice

Minimal set of functions

# In fact, we can do it with only NOR or only NAND

□ NOT is just a NAND or a NOR with both inputs tied together

☐ and NAND and NOR are "duals", 1 1 0 that is, its easy to implement one using the other

$\begin{array}{ll} X \ \underline{\text{nand}} \ Y & \underline{\text{not}} \ ( \ (\text{not} \ X) \ \underline{\text{nor}} \ (\text{not} \ Y) \ ) \\ \text{\$} & \underline{\text{But lets not moYeDoGo}} f_{ast} \overline{=} \ \underline{\text{not}} \ ( \ (\underline{\text{not}} \ X) \ \underline{\text{nand}} \ (\underline{\text{not}} \ Y) \ ) \\ \hline \square \ \text{lets look at the mathematical foundation of logic} \end{array}$

CSE370 - II - Combinational Logic

```

## An algebraic structure consists of

☐ a set of elements B

☐ binary operations { + , • }

☐ and a unary operation { ' }

☐ such that the following axioms hold:

1. the set B contains at least two elements: a, b

2. closure: a + b is in B

3. commutativity: a + b = b + a

4. associativity: a + (b + c) = (a + b) + c

5. identity: a + (b + c) = (a + b) + c

6. distributivity: a + (b + c) = (a + b) • (a + c)

7. complementarity: a + a' = 1

Winter 2001

Winter 2001

### CSE370 - II - Combinational Logic

$ 5

```

### Axioms and theorems of Boolean algebra (cont'd)

```

\frac{\text{distributivity:}}{8. \quad X \bullet (Y + Z) = (X \bullet Y) + (X \bullet Z)} \quad 8D. \quad X + (Y \bullet Z) = (X + Y) \bullet (X + Z)

\frac{\text{uniting:}}{9. \quad X \cdot Y + X \cdot Y' = X}

9D. (X + Y) \cdot (X + Y') = X

\begin{array}{ll} \text{38} & \underline{\text{absorption}}; \\ 10. \ X + X \bullet Y = X \\ 11. \ (X + Y) \bullet Y = X \bullet Y \end{array} \\ 10D. \ X \bullet (X + Y) = X \\ 11D. \ (X \bullet Y') + Y = X + Y \end{array}

# factoring: 12. (X + Y) \bullet (X' + Z) = (X \bullet Z + X' \bullet Y) \bullet (X' + Z) \bullet (X \bullet Z + X' \bullet Y)

(X + Z) • (X' + Y)

# <u>concensus:</u> 13. (X \bullet Y) + (Y \bullet Z) + (X' \bullet Z) =  13D. (X + Y) \bullet (Y + Z) \bullet (X' + Z) =  (X + Y) \bullet (X' + Z) =

```

CSE370 - II - Combinational Logic

### Axioms and theorems of Boolean algebra (cont')

```

\frac{\text{de M or gan's:}}{14. (X + Y + ...)'} = X' \cdot Y' \cdot ...

14D. (X \bullet Y \bullet ...)' = X' + Y' + ...

15. f'(X_1, X_2, ..., X_n, 0, 1, +, \bullet) = f(X_1', X_2', ..., X_n', 1, 0, \bullet, +)

```

★ establishes relationship between • and +

CSE370 - II - Combinational Logic

### Axioms and theorems of Boolean algebra (cont')

```

₩ Duality

```

Winter 2001

☐ a dual of a Boolean expression is derived by replacing • by +, + by •, 0 by 1, and 1 by 0, and leaving variables unchanged  $\hfill \triangle$  any theorem that can be proven is thus also proven for its dual! △ a meta-theorem (a theorem about theorems)

$\begin{array}{ccc} \Re & \underline{\text{generalized duality:}} \\ & 17.\ f\left(X_1, X_2, \dots, X_n, 0, 1, +, \bullet\right) \Leftrightarrow f(X_1, X_2, \dots, X_n, 1, 0, \bullet, +) \end{array}$

### # Different than deMorgan's Law

$\hfill \square$  this is a statement about theorems

☐ this is not a way to manipulate (re-write) expressions

Winter 2001

CSE370 - II - Combinational Logic

### Proving theorems (rewriting)

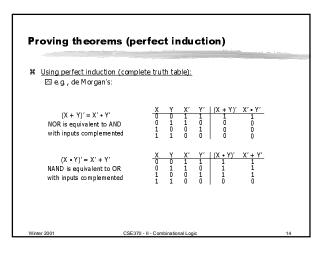

# Using the axioms of Boolean algebra:  $\triangle$  e.a., prove the theorem:  $X \bullet Y + X \bullet Y' = X$

distributivity (8) complementarity (5)  $X \bullet Y + X \bullet Y' = X \bullet (Y + Y')$   $X \bullet (Y + Y') = X \bullet (1)$   $X \bullet (1) = X =$ identity (1D)

$X + X \bullet Y = X$ □ e.g., prove the theorem:

> identity (1D)  $\begin{array}{ccccccc} X + X \bullet Y & = & X \bullet 1 + X \bullet Y \\ X \bullet 1 + X \bullet Y & = & X \bullet (1 + Y) \\ X \bullet (1 + Y) & = & X \bullet (1) \\ X \bullet (1) & = & X - \end{array}$ distributivity (8) identity (2) identity (1D)

Winter 2001 CSE370 - II - Combinational Logic

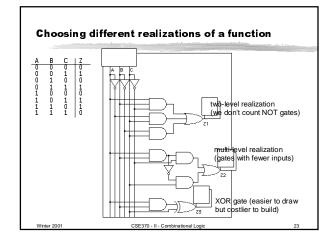

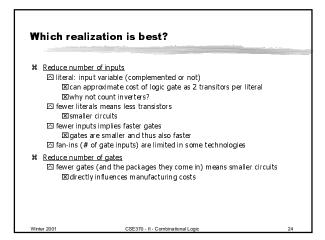

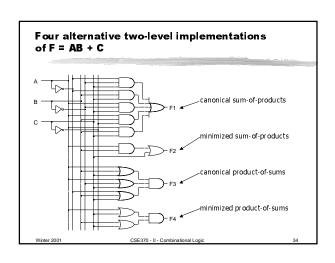

### Which is the best realization? (cont'd)

- - ☐ fewer level of gates implies reduced signal propagation delays ☐ minimum delay configuration typically requires more gates ⊠wider, less deep circuits

- ₩ How do we explore tradeoffs between increased circuit delay and size?

△ automated tools to generate different solutions

- ☐ logic minimization: reduce number of gates and complexity

- ☐ logic optimization: reduction while trading off against delay

## Are all realizations equivalent?

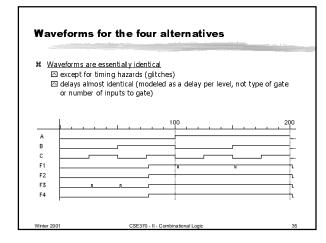

- # Under the same input stimuli, the three alternative implementations have almost the same waveform behavior

☐ delays are different

- ☐ glitches (hazards) may arise

- 🖾 variations due to differences in number of gate levels and structure

- ★ The three implementations are functionally equivalent

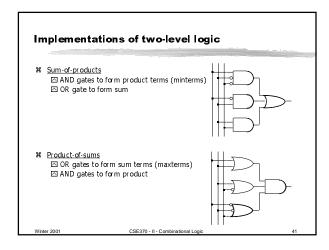

### Implementing Boolean functions

- 第 Technology independent

- □ canonical forms

- ☐ multi-level forms

- ★ Technology choices

- ☐ packages of a few gates ☐ regular logic

- ☐ two-level programmable logic

- ☐ multi-level programmable logic

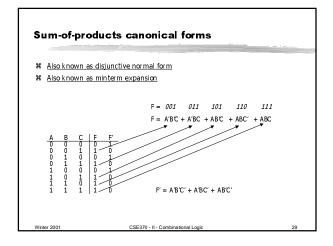

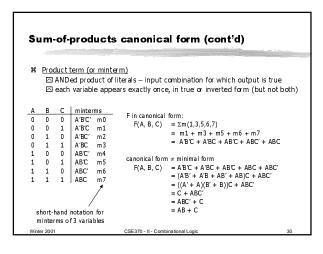

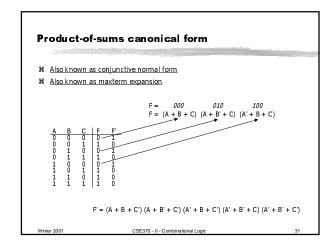

### **Canonical forms**

- **※** Truth table is the unique signature of a Boolean function

- # Many alternative gate realizations may have the same truth table

- ₩ Canonical forms

- □ standard forms for a Boolean expression

- ☐ provides a unique algebraic signature

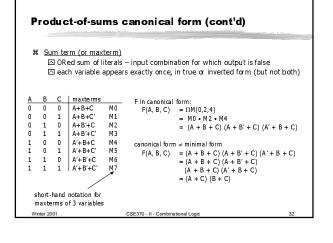

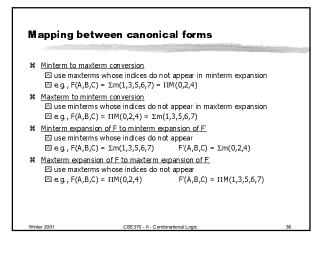

# \*\*Sum-of-products □ F' = A'B'C' + A'BC' + AB'C' \*\*Apply de Morgan's □ (F')' = (A'B'C' + A'BC' + AB'C')' □ F = (A + B + C) (A + B' + C) (A' + B + C) \*\*Product-of-sums □ F' = (A + B + C') (A + B' + C') (A' + B + C') (A' + B' + C) (A' + B' + C') \*\*Apply de Morgan's □ (F')' = ((A + B + C')(A + B' + C')(A' + B + C')(A' + B' + C)(A' + B' + C'))' □ F = A'B'C + A'BC + A'B'C + A'BC' + A'BC

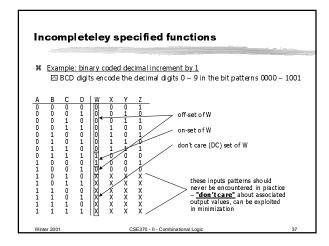

### Notation for incompletely specified functions

★ Don't cares and canonical forms

☐ so far, only represented on-set ☐ also represent don't-care-set

☐ need two of the three sets (on-set, off-set, dc-set)

# Canonical representations of the BCD increment by 1 function:

$$\triangle$$

Z = m0 + m2 + m4 + m6 + m8 + d10 + d11 + d12 + d13 + d14 + d15

$$\triangle$$

Z =  $\Sigma$  [ m(0,2,4,6,8) + d(10,11,12,13,14,15) ]

$\triangle$  Z =  $\Pi$  [ M(1,3,5,7,9) • D(10,11,12,13,14,15) ]

CSE370 - II - Combinational Logi

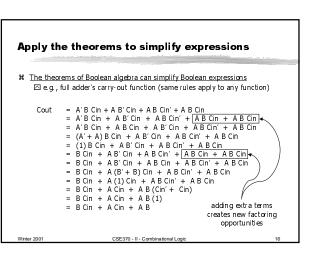

### Simplification of two-level combinational logic

- # Finding a minimal sum of products or product of sums realization

- exploit don't care information in the process

- # Algebraic simplification

- ☐ not an algorithmic/systematic procedure

☐ how do you know when the minimum realization has been found?

- 第 <u>Computer-aided design tools</u>

- ☐ precise solutions require very long computation times, especially for functions with many inputs (> 10)

☐ heuristic methods employed "educated guesses" to reduce amount of computation and yield good if not best solutions

- 第 Hand methods still relevant

- ☐ to understand automatic tools and their strengths and weaknesses

- ☐ ability to check results (on small examples)

CSE370 - II - Combinational Logic

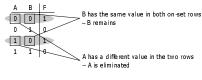

### The uniting theorem

- # Key tool to simplification: A (B' + B) = A

- ★ Essence of simplification of two-level logic

- ☐ find two element subsets of the ON-set where only one variable changes its value this single varying variable can be eliminated and a single product term used to represent both elements

$$F = A'B' + AB' = (A' + A)B' = B'$$

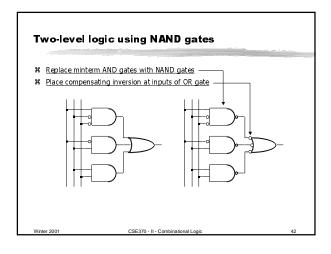

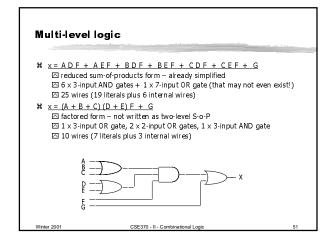

### Summary for multi-level logic

### ₩ <u>Advantages</u>

□ circuits may be smaller

☐ gates have smaller fan-in

☐ circuits may be faster

### ₩ <u>Disadvantages</u>

☐ more difficult to design

$\hfill \triangle$  tools for optimization are not as good as for two-level

□ analysis is more complex

CSE370 - II - Combinational Logic

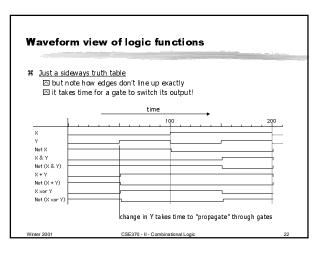

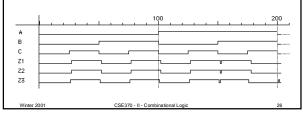

### Time behavior of combinational networks

### ₩ <u>Waveforms</u>

☑ visualization of values carried on signal wires over time ☐ useful in explaining sequences of events (changes in value)

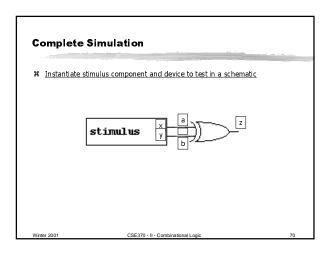

★ Simulation tools are used to create these waveforms

☐ input to the simulator includes gates and their connections

☐ input stimulus, that is, input signal waveforms

### ₩ Some terms

☐ gate delay — time for change at input to cause change at output ⊠min delay – typical/nominal delay – max delay  $oxed{\boxtimes}$  careful designers design for the worst case

☐ rise time — time for output to transition from low to high voltage

☐ fall time — time for output to transition from high to low voltage

riangle pulse width — time that an output stays high  $\sigma$  stays low between changes

### Hardware description languages

- 第 Describe hardware at varying levels of abstraction

- ₩ Structural description

- ☐ textual replacement for schematic  $\hfill \triangle$  hierarchical composition of modules from primitives

- # Behavioral/functional description ☐ synthesis generates circuit for module

- ₩ Simulation semantics

CSE370 - II - Combinational Logic

### **HDLs**

- \*\* Abel (circa 1983) developed by Data-I/O

□ targeted to programmable logic devices

□ not good for much more than state machines

- # ISP (circa 1977) research project at CMU

□ simulation, but no synthesis

- \* Verilog (circa 1985) developed by Gateway (absorbed by Cadence)

- ☑ similar to Pascal and C

- ☐ delays is only interaction with simulator ☐ fairly efficient and easy to write ☐ IEEE standard

- ¾ VHDL (circa 1987) DoD sponsαred standard

△ similar to Ada (emphasis on re-use and maintainability)

△ simulation semantics visible

△ very general but verbose

△ IEEE standard

```

Werill og

% Supports structural and behavioral descriptions

% Structural

△ explicit structure of the circuit

△ e.g., each logic gate instantiated and connected to others

% Behaviαal

△ program describes input/output behaviαr of circuit

△ many structural implementations could have same behaviαr

△ e.g., different implementation of one Boolean function

% We'll only be using behaviαral Verilog in DesignWorks

△ rely on schematic when we want structural descriptions

```

```

module xor_gate (out, a, b);

input a, b;

output out;

wire abar, bbar, t1, t2;

inverter invA (abar, a);

inverter invB (bbar, b);

and gate and1 (t1, a, bbar);

and gate and2 (t2, b, abar);

or_gate or1 (out, t1, t2);

endmodule

Where 2001 CSE370-II-CombinationalLogic 66

```

```

Simple behavioral model

₩ Continuous assignment

module xor_gate (out, a, b);

input

a, b;

output

out;

simulation register -

keeps track of

reg

out;

value of signal

assign #6 out = a ^ b;

endmodule

delay from input change

to output change

Winter 2001

CSE370 - II - Combinational Logic

```

```

Simple behavioral model

# always block

module xor_gate (out, a, b);

input a, b;

output out;

reg out;

always @(a or b) begin

#6 out = a ^ b;

end

endmodule

| specifies when block is executed |

ie. triggered by which signals

Winter 2001 | CSE370-II- Combinational Logic | 68

```

```

Driving a simulation

module stimulus (x, y);

х, у;

2-bit vector

reg [1:0]

cnt;

initial block executed

initial begin -

only once at start

cnt = 0;

of simulation

repeat (4) begin

#10 cnt = cnt + 1;

$display ("@ time=%d, x=%b, y=%b, cnt=%b",

$time, x, y, cnt); end

#10 $finish;

print to a console

end

assign x = cnt[1];

directive to stop

assign y = cnt[0];

endmodule

CSE370 - II - Combinational Logic

```

```

module Comparel (A, B, Equal, Alarger, Blarger);

input A, B;

output Equal, Alarger, Blarger;

assign #5 Equal = (A & B) | (~A & ~B);

assign #3 Alarger = (A & ~B);

assign #3 Blarger = (~A & B);

endmodule

```

### Hardware Description Languages vs. **Programming Languages**

- ₩ Program structure

- ☐ instantiation of multiple components of the same type ☐ specify interconnections between modules via schematic

- ☐ hierarchy of modules (only leaves can be HDL in DesignWorks)

- ¥ Assignment□ continuous assignment (logic always computes)

- ☐ propagation delay (computation takes time)

- ☐ timing of signals is important (when does computation have its effect)

- ₩ Data structures

- ☑ size explicitly spelled out no dynamic structures

- riangle no pointers

- ₩ Parallelism

- ☐ hardware is naturally parallel (must support multiple threads)

- △ assignments can occur in parallel (not just sequentially)

CSE370 - II - Combinational Logic

### Hardware Description Languages and Combinational Logic

- # Modules specification of inputs, outputs, bidirectional, and internal signals

- times (doesn't need to wait to be "called")

- # Propagation delay- concept of time and delay in input affecting gate output

- # Composition connecting modules together with wires

- # Hierarchy modules encapsulate functional blocks

- # Specification of don't care conditions (accomplished by setting output to "x").

# Specification of don't care conditions (accomplished by setting output to "x").

CSE370 - II - Combinational Logi

### Combinational logic summary

- **%** Logic functions, truth tables, and switches ☑ NOT, AND, OR, NAND, NOR, XOR, . . . , minimal set

- Axioms and theorems of Boolean algebra

proofs by re-writing and perfect induction

- **≋** Simplification

- ☑ two-level simplification

- Later

△ automation of simplification

□ multi-level logic

△ design case studies

☑ time behavior