| Comparis                                | on of latches and                                                     | flip-flops (cont'd)                                                       |

|-----------------------------------------|-----------------------------------------------------------------------|---------------------------------------------------------------------------|

| <u>Type</u><br>unclocked<br>latch       | When inputs are sampled always                                        | When output is valid<br>propagation delay from input change               |

| level-sensitive<br>latch                | clock high<br>(Tsu/Th around falling<br>edge of clock)                | propagation delay from input change<br>or clock edge (whichever is later) |

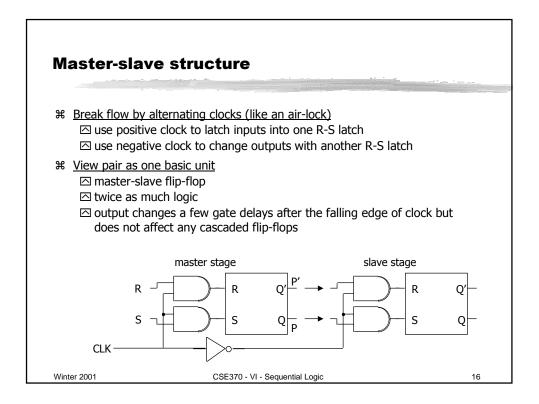

| master-slave<br>flip-flop               | clock high<br>(Tsu/Th around falling<br>edge of clock)                | propagation delay from falling edge of clock                              |

| negative<br>edge-triggered<br>flip-flop | clock hi-to-lo transition<br>(Tsu/Th around falling<br>edge of clock) | propagation delay from falling edge<br>of clock                           |

| Winter 2001                             | CSE370 - VI - Seque                                                   | ential Logic 25                                                           |

| EI   | in flan faaturas                                                                                                                                                                                                  |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

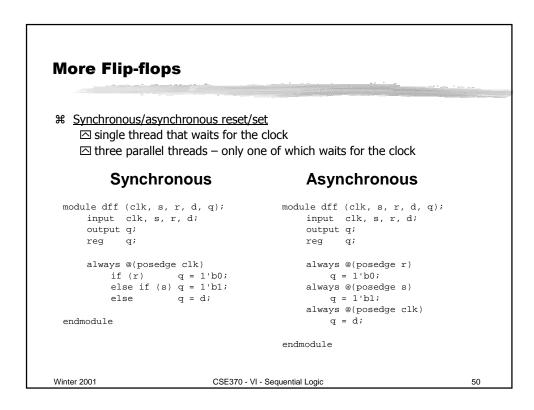

| •••  | ip-flop features                                                                                                                                                                                                  |    |

| Ħ    | Reset (set state to 0) – R<br>☐ synchronous: Dnew = R' • Dold (when next clock edge arrives)<br>☐ asynchronous: doesn't wait for clock, quick but dangerous                                                       |    |

| Ħ    | Preset or set (set state to 1) – S (or sometimes P)                                                                                                                                                               |    |

| Ħ    | Both reset and preset $\square$ Dnew = R' • Dold + S(set-dominant) $\square$ Dnew = R' • Dold + R'S(reset-dominant)                                                                                               |    |

| ж    | <u>Selective input capability (input enable or load) – LD or EN</u><br>$\square$ multiplexor at input: Dnew = LD' • Q + LD • Dold<br>$\square$ load may or may not override reset/set (usually R/S have priority) |    |

| Ħ    | Complementary outputs – Q and Q'                                                                                                                                                                                  |    |

| Wint | er 2001 CSE370 - VI - Sequential Logic                                                                                                                                                                            | 36 |

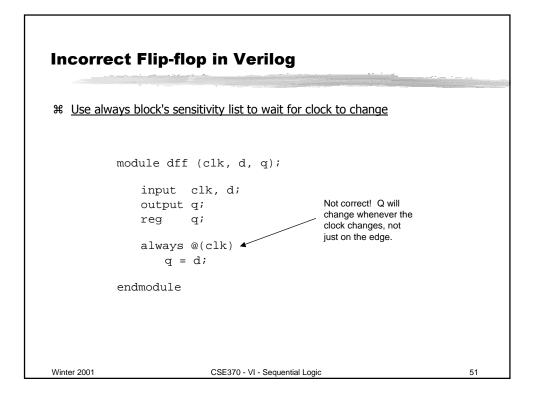

| Flip-flop ii          | n Verilog                                       |    |

|-----------------------|-------------------------------------------------|----|

| 策 <u>Use always l</u> | block's sensitivity list to wait for clock edge |    |

|                       | <pre>module dff (clk, d, q);</pre>              |    |

|                       | input clk, d;<br>output q;<br>reg q;            |    |

|                       | always @(posedge clk)<br>q = d;                 |    |

|                       | endmodule                                       |    |

|                       |                                                 |    |

| Winter 2001           | CSE370 - VI - Sequential Logic                  | 49 |

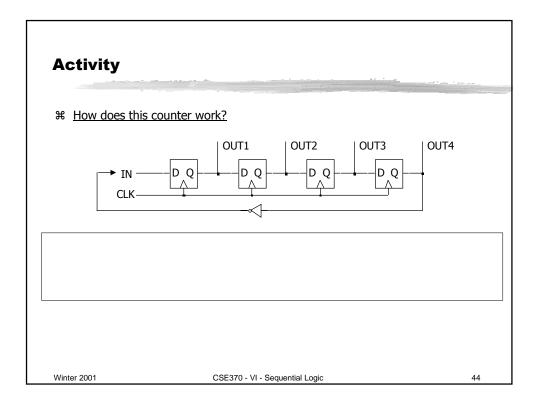

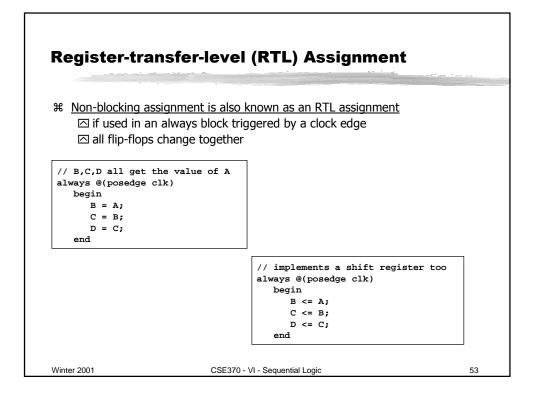

| Mobius Counter in Verilog |                                |  |  |  |

|---------------------------|--------------------------------|--|--|--|

| obius count               |                                |  |  |  |

|                           |                                |  |  |  |

| initial                   |                                |  |  |  |

| begin                     |                                |  |  |  |

| A = 1'b0;                 |                                |  |  |  |

| B = 1'b0;                 |                                |  |  |  |

| C = 1'b0;                 |                                |  |  |  |

| D = 1'b0;                 |                                |  |  |  |

| end                       |                                |  |  |  |

| always @(posedge o        | clk)                           |  |  |  |

| begin                     |                                |  |  |  |

| A <= ~D;                  |                                |  |  |  |

| B <= A;                   |                                |  |  |  |

| C <= B;                   |                                |  |  |  |

| D <= C;                   |                                |  |  |  |

| end                       |                                |  |  |  |

|                           |                                |  |  |  |

|                           |                                |  |  |  |

|                           |                                |  |  |  |

|                           |                                |  |  |  |

|                           |                                |  |  |  |

|                           |                                |  |  |  |

|                           |                                |  |  |  |

|                           |                                |  |  |  |

| r 2001                    | CSE370 - VI - Sequential Logic |  |  |  |