### Overview

- ♦ Last lecture

- Incompletely specified functions

- Design examples

- k-maps for POS minimization

- Today

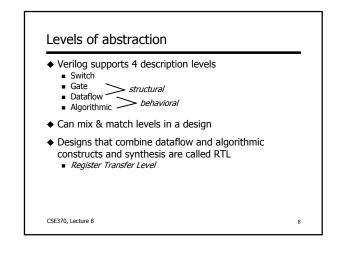

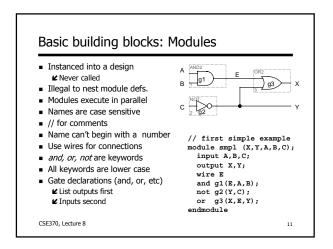

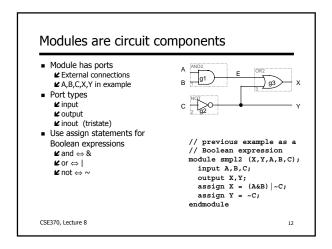

- Verilog

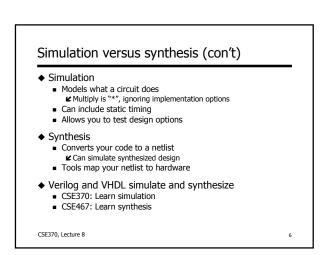

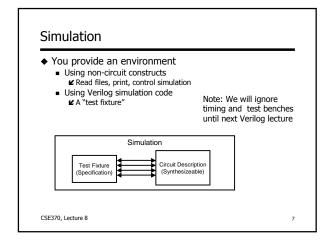

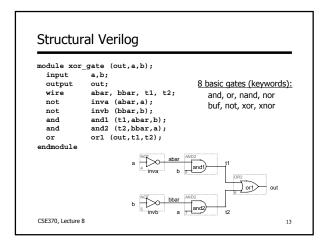

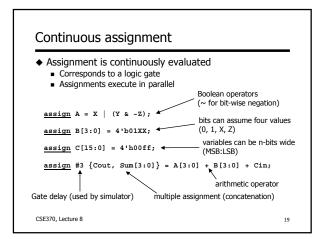

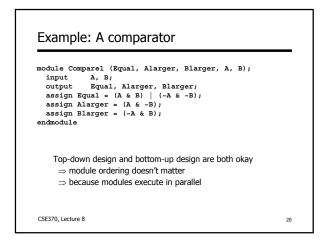

- ✓ Structural constructs ✔ Describing combinational circuits

CSE370, Lecture 8

## Ways of specifying circuits

#### Schematics

- Structural description Describe circuit as interconnected elements *L* Build complex circuits using hierarchy

- Large circuits are unreadable

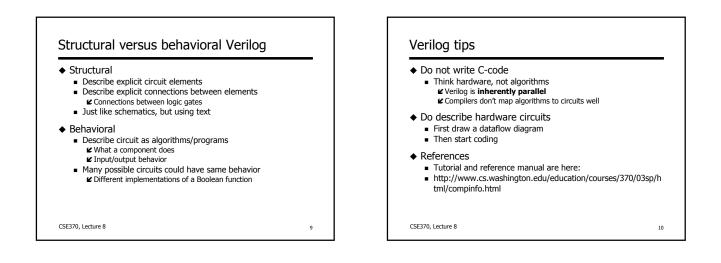

#### ♦ HDLs

- Hardware description languages

- ✔ Not programming languages✔ Parallel languages tailored to digital design

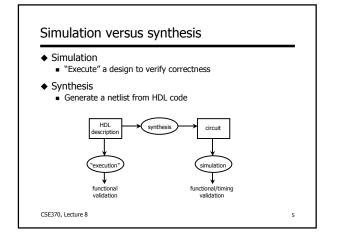

- Synthesize code to produce a circuit

CSE370, Lecture 8

1

3

## Hardware description languages (HDLs)

- ◆ Abel (~1983)

- Developed by Data-I/OTargeted to PLDs

- Limited capabilities (can do state machines)

- ◆ Verilog (~1985)

- Developed by Gateway (now part of Cadence)

Similar to C

- Moved to public domain in 1990

- ◆ VHDL (~1987)

- DoD sponsored

- Similar to Ada

CSE370, Lecture 8

2

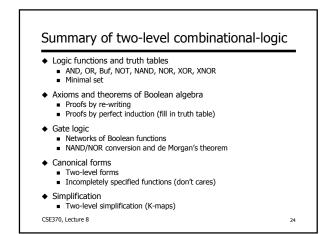

# Solving combinational design problems

25

- Step 1: Understand the problem

Identify the inputs and outputs

Draw a truth table

- Step 2: Simplify the logic

Draw a K-map

Write a simplified Boolean expression

SOP or POS

Use don't cares

- Step 3: Implement the design

Logic gates and/or Verilog

CSE370, Lecture 8