#### Lecture 7

- Verilog

- Structural constructs

- Describing combinational circuits

- Additional references

- Tutorial and reference manual are found in ActiveHDL help

- "Starter's Guide to Verilog 2001" by Michael Ciletti copies for borrowing in hardware lab

1

3

# Combinational design

- Step 1: Understand the problem

- Identify the inputs and outputs

- Draw a truth table

- Step 2: Simplify the logic

- Draw a K-map

- Write a simplified Boolean expression

- SOP or POS

- Use don't cares

- Step 3: Implement the design

- Logic gates and/or

- Verilog

2

# Ways of specifying circuits

- Schematics

- Structural description

- Describe circuit as interconnected elements

- Build complex circuits using hierarchy

- Large circuits are unreadable

- Hardware description languages (HDLs)

- Not programming languages

- Parallel languages tailored to digital design

- Synthesize code to produce a circuit

# Verilog versus VHDL

- Both "IEEE standard" languages

- Most tools support both

- Verilog is "simpler"

- Less syntax, fewer constructs

- VHDL is more structured.

- Can be better for large, complex systems

- Better modularization

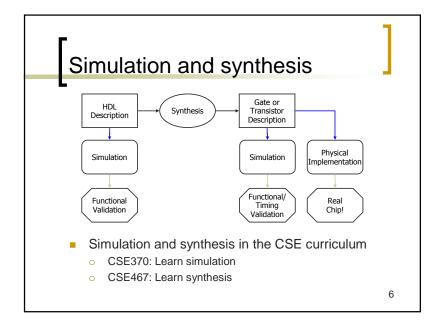

## Simulation and synthesis

- Simulation

- Models what a circuit does

- Multiply is "\*", ignoring implementation options

- o Allows you to test design options

- o "Execute" a design to verify correctness

- Synthesis

- Converts your code to a "netlist"

- Can simulate synthesized design

- Tools map your netlist to hardware

5

7

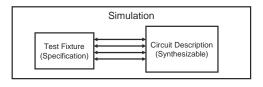

### Simulation

- You provide an environment

- Using non-circuit constructs

- Active-HDL waveforms, read files, print

- Using Verilog simulation code

- A "test fixture"

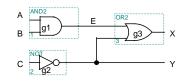

Specifying circuits in Verilog Three major styles Instances and wires Continuous assignments o "always" blocks "Behavioral" "Structural" reg E, X, Y; wire E; wire E; and g1(E,A,B); assign E = A & B; always @ (A or B or C) not g2(Y,C); assign Y = ~C; begin E = A & B;or g3(X,E,Y); assign  $X = E \mid Y;$ Y = ~C; $X = E \mid Y;$ 8

## Data types

- Values on a wire

- 0, 1, x (unknown or conflict), z (tristate or unconnected)

- Vectors

- A[3:0] vector of 4 bits: A[3], A[2], A[1], A[0]

- Unsigned integer value

- Indices must be constants

9

## Manipulating vectors

- Concatenating bits/vectors, use { }

- o e.g. sign extend

- B[7:0] = {A[3], A[3], A[3], A[3], A[3:0]};

- B[7:0] = {4{A[3]}, A[3:0]};

- Style: Use a[7:0] = b[7:0] + c[7:0]

Not a = b + c;

10

# Data types that do **NOT** exist

- Structures

- Pointers

- Objects

- Recursive types

Verilog is not C or Java or Lisp or ...!

Numbers

- Format: <sign><size><base><number>

- **1**4

- Decimal number

- -4'b11

- o 4-bit 2's complement binary of 0011 (is 1101)

- 12'b0000\_0100\_0110

- 12 bit binary number (\_ is ignored)

- 12'h046

- o 3-digit (12-bit) hexadecimal number

12

# Numbers are unsigned

- C[4:0] = A[3:0] + B[3:0];

- if A = 0110 (6) and B = 1010(-6),

then C = 10000 (not 00000)

- o B is zero-padded, not sign-extended

13

# Operators

| Verilog<br>Operator                                                                        | Name                                                                                                             | Functional Group                                                                     |

|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| 0                                                                                          | bit-select or part-select                                                                                        |                                                                                      |

| ()                                                                                         | parenthesis                                                                                                      |                                                                                      |

| !<br>&<br> <br> <br> -<br> <br> -<br> <br> <br> -<br> <br> -<br> -<br> -<br> -<br> -<br> - | logical negation<br>negation<br>reduction AND<br>reduction OR<br>reduction NOR<br>reduction NOR<br>reduction XOR | Logical<br>Bit-wise<br>Reduction<br>Reduction<br>Reduction<br>Reduction<br>Reduction |

| +                                                                                          | unary (sign) plus<br>unary (sign) minus                                                                          | Arithmetic<br>Arithmetic                                                             |

| {}                                                                                         | concatenation                                                                                                    | Concatenation                                                                        |

| {{ }}                                                                                      | replication                                                                                                      | Replication                                                                          |

| /<br>%                                                                                     | multiply<br>divide<br>modulus                                                                                    | Arithmetic<br>Arithmetic<br>Arithmetic                                               |

| *                                                                                          | binary plus<br>binary minus                                                                                      | Arithmetic<br>Arithmetic                                                             |

| <<<br>>>                                                                                   | shift left<br>shift right                                                                                        | Shift<br>Shift                                                                       |

| greater than<br>greater than or equal to<br>less than<br>less than or equal to | Relational<br>Relational<br>Relational<br>Relational                                                                                                                                                                                             |

|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| logical equality<br>logical inequality                                         | Equality<br>Equality                                                                                                                                                                                                                             |

| case equality<br>case inequality                                               | Equality<br>Equality                                                                                                                                                                                                                             |

| bit-wise AND                                                                   | Bit-wise                                                                                                                                                                                                                                         |

| bit-wise XOR<br>bit-wise XNOR                                                  | Bit-wise<br>Bit-wise                                                                                                                                                                                                                             |

| bit-wise OR                                                                    | Bit-wise                                                                                                                                                                                                                                         |

| logical AND                                                                    | Logical                                                                                                                                                                                                                                          |

| logical OR                                                                     | Logical                                                                                                                                                                                                                                          |

| conditional                                                                    | Conditional                                                                                                                                                                                                                                      |

|                                                                                | greater than or equal to less than less than or equal to less than or equal to less than or equal to logical equality case inequality case inequality case inequality bit wise AND bit-wise XOR bit-wise XNOR bit-wise OR logical AND logical OR |

#### Similar to Java operators

14

### Two abstraction mechanisms

- Modules

- More structural, but also behavioral

- Heavily used in 370 and "real" Verilog code

- Functions

- More behavioral

- Used to some extent in "real" Verilog, but not much in 370

# Basic building blocks: modules

```

// first simple example

module simple (X,Y,A,B,C);

input A,B,C;

output X,Y;

wire E

and g1(E,A,B);

not g2(Y,C);

or g3(X,E,Y);

endmodule

```

16

# Basic building blocks: modules

- Instanced into a design

- Never called

- Use wires for connections

- Modules execute in parallel

- Gate declarations (and, or, etc)

- List outputs first

- Inputs second

- Name can't begin with a number

- Names are case sensitive

- Keywords are in lowercase

- and, or, not are keywords

- Illegal to nest module definitions

- // for comments

17

# Modules are circuit components

- Module has ports

- External connections

- A,B,C,X,Y in example

- Port types

- input

- output

- inout (tristate)

- Use assign statements for Boolean expressions

- o and ⇔ &

- or ⇔

- o not ⇔ ~

// previous example as a

// Boolean expression

module simple2 (X,Y,A,B,C);

input A,B,C;

output X,Y;

assign X = (A&B)|~C;

assign Y = ~C;

endmodule

18

# Structural Verilog

```

module xor_gate (out,a,b);

input

a,b;

output

out;

wire

abar, bbar, t1, t2;

inva (abar,a);

not.

not

invb (bbar,b);

and1 (t1,abar,b);

and

and

and2 (t2,bbar,a);

or1 (out,t1,t2);

endmodule

8 basic gates (keywords):

and, or, nand, nor

buf, not, xor, xnor

19

```

# **Behavioral Verilog**

Describe circuit behavior

Not implementation

```

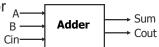

module full_addr (Sum,Cout,A,B,Cin);

input A, B, Cin;

output Sum, Cout;

assign {Cout, Sum} = A + B + Cin;

endmodule

```

{Cout, Sum} is a concatenation

#### Behavioral 4-bit adder

```

module add4 (SUM, OVER, A, B);

Buses are implicitly connected—

input [3:0] A;

If you write BUS[3:2], BUS[1:0],

input [3:01 B;

they become part of BUS[3:0]

output [3:0] SUM;

output OVER;

assign \{OVER, SUM[3:0]\} = A[3:0] + B[3:0];

endmodule

"[3:0] A" is a 4-wire bus labeled "A"

Bit 3 is the MSB

Bit 0 is the LSB

Can also write "[0:3] A"

Bit 0 is the MSB

Bit 3 is the LSB

21

```

# Continuous assignment Assignment is continuously evaluated

- - Corresponds to a logic gate

- Assignments execute in parallel

```

Boolean operators

(~ for bit-wise negation)

assign A = X | (Y & ~Z); *

bits can assume four values

(0, 1, X, Z)

assign B[3:0] = 4'b01XX; *

variables can be n-bits wide

assign C[15:0] = 16'h00ff; -

assign #3 \{Cout, Sum[3:0]\} = A[3:0] + B[3:0] + Cin;

gate delay (used by simulator)

22

```

### Invalid sequential assigns

```

assign A = X \mid (Y \& \sim Z);

"Reusing" a variable on the left

side of several assign statements

assign B = W | A;

is not allowed

assign A = Y & Z;

Cyclic dependencies also are bad

assign A = X \mid (Y \& \sim Z);

A depends on X

assign B = W | A;

which depends on B

which depends on A

assign X = B & Z;

23

```

# Example: 4-bit comparator

```

module Comparel (Equal, Alarger, Blarger, A, B);

input

A, B;

output

Equal, Alarger, Blarger;

assign Equal = (A & B) | (~A & ~B);

assign Alarger = (A & ~B);

assign Blarger = (~A & B);

endmodule

```

- Starting with 1-bit comparator

- Top-down design and bottom-up design are both okay

- Module ordering doesn't matter because modules execute in parallel

#### 4-bit comparator

25

27

#### **Functions**

Use functions for complex combinational logic

```

module and_gate (out, in1, in2);

in1, in2;

input

output

out;

assign out = myfunction(in1, in2);

function myfunction;

Benefit:

input in1, in2;

Functions force a result

begin

⇒ Compiler will fail if function

myfunction = in1 & in2;

does not generate a result

end

endfunction

endmodule

26

```

# Always code blocks

```

Variables that appear

on the left hand side in

an always block must

be declared as "reg"s

Sensitivity list:

reg A, B, C;

block is executed

each time one of

always @ (W or X or Y or Z) ←

them changes value

begin

A = X \mid (Y \& \sim Z);

B = W | A;

Statements in an always

A = Y & Z;

block are executed in

if (A & B) begin

B = Z;

C = W \mid Y;

end

BAD: All variables must be

assigned on every control path!!!

```

# Assignments

- Blocking assignments (Q = A)

- Variable is assigned immediately

- New value is used by subsequent statements

- Non-blocking assignments (Q <= A)</li>

- Variable is assigned after all scheduled statements are executed

- Value to be assigned is computed but saved for later parallel assignment

- Usual use: Register assignment

- Registers simultaneously take new values after the clock edge

# Blocking vs. non-blocking

Example: Swap

```

always @(posedge CLK)

begin

temp = B;

B = A;

A = temp;

end

always @(posedge CLK)

begin

A <= B;

B <= A;

end

```

29

# Verilog tips

- Do not write C-code

- Think hardware, not algorithms

- Verilog is inherently parallel

- Compilers don't map algorithms to circuits well

- **Do** describe hardware circuits

- First draw a dataflow diagram

- Then start coding