© 2005 Hank Levy

| TLBs                                                                                                                                                                                                                                                                                        |                  |   | Managing TLBs                                                                                                                                                                                                                                                                                |                  |   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---|

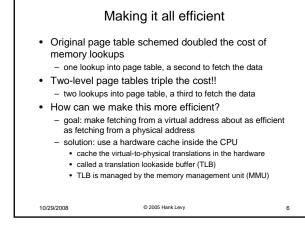

| <ul> <li>Translation lookaside buffers         <ul> <li>translates virtual page #s into PTEs (not physical addrs)</li> <li>can be done in single machine cycle</li> </ul> </li> </ul>                                                                                                       |                  |   | <ul> <li>Address translations are mostly handled by the TLB</li> <li>&gt;99% of translations, but there are TLB misses occasionally</li> <li>in case of a miss, who places translations into the TLB?</li> </ul>                                                                             |                  |   |

| <ul> <li>TLB is implemented in hardware         <ul> <li>is a fully associative cache (all entries searched in parallel)</li> <li>cache tags are virtual page numbers</li> <li>cache values are PTEs</li> <li>with PTE + offset, MMU can directly calculate the PA</li> </ul> </li> </ul>   |                  |   | <ul> <li>Hardware (memory management unit, MMU)         <ul> <li>knows where page tables are in memory</li> <li>OS maintains them, HW access them directly</li> <li>tables have to be in HW-defined format</li> <li>this is how x86 works</li> </ul> </li> </ul>                             |                  |   |

| <ul> <li>TLBs exploit locality <ul> <li>processes only use a handful of pages at a time</li> <li>16-48 entries in TLB is typical (64-192KB)</li> <li>can hold the "hot set" or "working set" of process</li> <li>hit rates in the TLB are therefore really important</li> </ul> </li> </ul> |                  |   | <ul> <li>Software loaded TLB (OS)         <ul> <li>TLB miss faults to OS, OS finds right PTE and loads TLB</li> <li>must be fast (but, 20-200 cycles typically)</li> <li>CPU ISA has instructions for TLB manipulation</li> <li>OS gets to pick the page table format</li> </ul> </li> </ul> |                  |   |

| 10/29/2008                                                                                                                                                                                                                                                                                  | © 2005 Hank Levy | 7 | 10/29/2008                                                                                                                                                                                                                                                                                   | © 2005 Hank Levy | 8 |

9

© 2005 Hank Levy

10/29/2008

## · Memory-mapped files

- instead of using open, read, write, close

"map" a file into a region of the virtual address space

e.g., into region with base 'X'

- accessing virtual address 'X+N' refers to offset 'N' in file

- initially, all pages in mapped region marked as invalid

- OS reads a page from file whenever invalid page accessed

- OS writes a page to file when evicted from physical memory

only necessary if page is dirty

© 2005 Hank Levy

14

10/29/2008

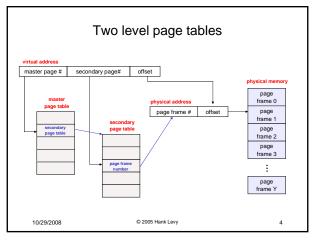

4