# **Productivity Problem**

- Designer = 100 gates/day, 10 lines tested-debugged verilog

- Design = 200,000 gates, optimum design team = 2

- Project = 1000 days, almost 3 years!

- Management expects project done in a year or less

- Result = Big Problem!

- Solutions?

## **Productivity Increase**

- Bigger Design team

- Coffman's Law

- Individual designer must produce more code

- Each line of code represents more gates

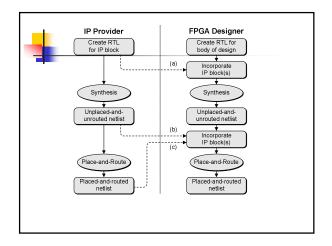

- Reuse designs

- Libraries

- Reuse old projects

- Buy IP (Intellectual Property)

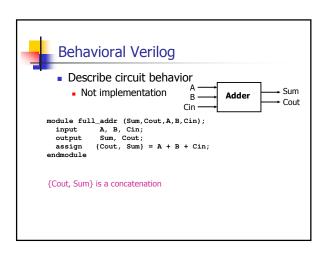

```

Structural Verilog

odule xor_gate (out,a,b);

input

a,b;

output

8 basic gates (keywords):

abar, bbar, t1, t2; inva (abar,a);

wire

and, or, nand, nor

buf, not, xor, xnor

not

invb (bbar.b):

and1 (t1,abar,b);

and

and2 (t2,bbar,a);

or1 (out, t1, t2);

endmodule

```

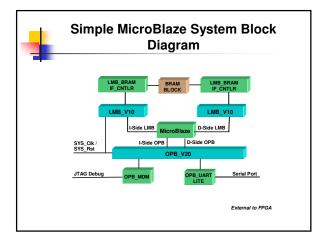

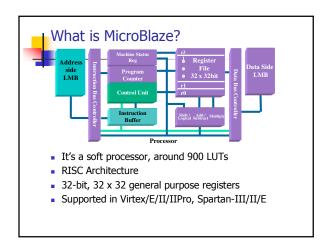

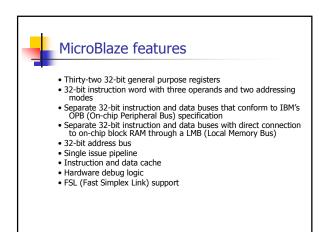

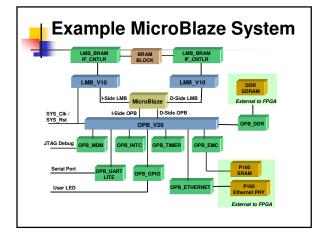

### More on MicroBlaze ...

- Harvard Architecture

- Configurable instruction cache, data cache soon

- Non-intrusive JTAG debug

- Support for 2 buses:

- LMB (Local Memory Bus) 1 clock cycle latency, connects to BRAM

- OPB (On-chip Peripheral Bus) part of the IBM CoreConnect™ standard, connects to other peripheral "Portable" IP between PPC and MB

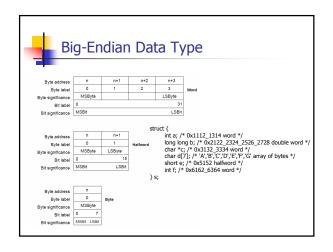

- Big endian, same as PowerPC PPC405

## MicroBlaze Interrupts and Exceptions

- Interrupt handling

- 1 Interrupt port

- 32+ interrupts and masking supported through interrupt controller(s)

- Exception handling

- No exceptions generated in Virtex-II versions

- One in Virtex/E and Spartan-II versions for MUL instruction

#### Software Tools

- GNU tool chain

- GCC GNU Compiler Collection

- GDB The GNU debugger

- Source code debugging

- Debug either C or assembly code

- XMD Xilinx Microprocessor Debug utility

- Separate Process

- Provides cycle accurate program execution data

- Supported targets: simulator, hardware board

# Software - XMD

- Interfaces GDB to a "target"

- Allows hardware debug without a ROM monitor or reduces debug logic by using xmd-stub (ROM monitor)

- Offers a variety of simulation targets

- Cycle accurate simulator

- Real hardware board interface via UART or MDM

- Includes remote debugging capability

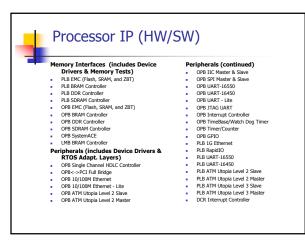

# More System Cores

- Processor System Reset

- Asynchronous external reset input is synchronized with clock

- Selectable active high or active low reset

- DCM Locked input

- Sequencing of reset signals coming out of reset:

- · First bus structures come out of reset

- Second Peripheral(s) come out of reset 16 clocks later

Third the CPU(s) come out of reset 16 clocks after the peripherals

- JTAG Controller

- Wrapper for the JTAGPPC primitive.

- Enables the PowerPC's debug port to be connected to the FPGA JTAG chain

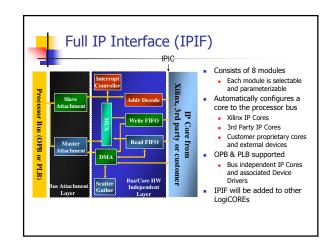

- IPIF User Core Templates

- Convenient way to add user core to OPB or PLB

## Timer / Counter

- Supports 32-bit OPB v2.0 bus interface

- Two programmable interval timers with interrupt, compare, and capture capabilities

- Programmable counter width

- One Pulse Width Modulation (PWM) output

## Watchdog Timer / Timebase

- Supports 32-bit bus interfaces

- · Watchdog timer (WDT) with selectable timeout period and interrupt

- · Two-phase WDT expiration scheme

- · Configurable WDT enable: enable-once or enable-

- · WDT Reset Status (was the last reset caused by the WDT?)

- · One 32-bit free-running timebase counter with rollover interrupt

### **Interrupt Controller**

- Number of interrupt inputs is configurable up to the width of the data bus width

- Interrupt controllers can be easily cascaded to provide additional interrupt inputs

- Master Enable Register for disabling the interrupt request output

- Each input is configurable for edge or level sensitivity rising or falling, active high or active low

- Output interrupt request pin is configurable for edge or level generation

### UART 16550 / 16450 / Lite

- Register compatible with industry standard 16550/16450

- 5, 6, 7 or 8 bits per character

- Odd, even or no parity detection and generation

- 1, 1.5 or 2 stop bit detection and generation

- Internal baud rate generator and separate RX clock input

- Modem control functions

- Prioritized transmit, receive, line status & modem control interrupts

- Internal loop back diagnostic functionality

- Independent 16 word transmit and receive FIFOs

### IIC

- 2-wire (SDA and SCL) serial interface

- Master/Slave protocol

- Multi-master operation with collision detection and arbitration

- Bus busy detection

- Fast Mode 400 KHz or Standard Mode 100 KHz operation

- 7 Bit, 10 Bit, and General Call addressing

- Transmit and Receive FIFOs 16 bytes deep

- Bus throttling

#### **SPI**

- 4-wire serial interface (MOSI, MISO, SCK, and SS)

- Master or slave modes supported

- Multi-master environment supported (requires tri-state drivers and software arbitration for possible conflict)

- Multi-slave environment supported (requires additional decoding and slave select signals)

- Programmable clock phase and polarity

- Optional transmit and receive FIFOs

- Local loopback capability for testing

## Ethernet 10/100 MAC

- 32-bit OPB master and slave interfaces

- Media Independent Interface (MII) for connection to external 10/100 Mbps PHY Transceivers

- Full and half duplex modes of operation

- Supports unicast, multicast, broadcast, and promiscuous addressing

- Provides auto or manual source address, pad, and Frame Check Sequence

## Ethernet 10/100 MAC (cont)

- Simple DMA and Scatter/Gather DMA architecture for low processor and bus utilization, as well as a simple memory-mapped direct I/O interface

- Independent 2K to 32K transmit and receive FIFOs

- Supports MII management control writes and reads with MII PHYs

- Supports VLAN and Pause frames

- Internal loopback mode

### 1 Gigabit MAC

- 64-bit PLB master and slave interfaces

- GMII for connection to external PHY Transceivers

- Optional PCS function with Ten Bit Interface (TBI) to external PHY devices

- Option PCS/PMA functions with SerDes interface to external transceiver devices for reduced signal count

- Full duplex only

- Provides auto or manual source address, pad, and Frame Check Sequence

### 1 Gigabit MAC (cont)

- Simple DMA and Scatter/Gather DMA architecture for low processor and bus utilization, as well as a simple memory-mapped direct I/O interface

- Independent, depth-configurable TX and RX FIFOs

- Supports MII management control writes and reads with MII PHYs

- Jumbo frame and VLAN frame support

- Internal loopback mode

### Single Channel HDLC

- Support for a single full duplex HDLC channel

- Selectable 8/16 bit address receive address detection, receive frame address discard, and broadcast address detection

- Selectable 16 bit (CRC-CCITT) or 32 bit (CRC-32) frame check sequence

- Flag sharing between back to back frames

- Data rates up to OPB\_Clk frequency

## Single Channel HDLC (cont)

- Simple DMA and Scatter/Gather DMA architecture for low processor and bus utilization, as well as a simple memory-mapped direct I/O interface

- Independent, depth-configurable TX and RX FIFOs

- Selectable broadcast address detection and receive frame address discard

- Independent RX and TX data rates

## ATM Utopia Level 2

- UTOPIA Level 2 master or slave interface

- UTOPIA interface data path of 8 or 16 bits

- Single channel VPI/VCI service and checking in received cells

- Header error check (HEC) generation and checking

- Parity generation and checking

- Selectively prepend headers to transmit cells, pass entire received cells or payloads only, and transfer 48 byte ATM payloads only

#### ATM Utopia Level 2 (cont)

- Simple DMA and Scatter/Gather DMA architecture for low processor and bus utilization, as well as a simple memory-mapped direct I/O interface

- Independent, depth-configurable TX and RX FIFOs

- Interface throughput up to 622 Mbps (OC12)

- Internal loopback mode

### **OPB-PCI** Bridge

- 33/66 MHz, 32-bit PCI buses

- Full bridge functionality

- OPB Master read/write of a remote PCI target (both single and burst)

- PCI Initiator read/write of a remote OPB slave (both single and multiple)

- Supports up to 3 PCI devices with unique memory PCI memory space

- Supports up to 6 OPB devices with unique memory OPB memory space

- PCI and OPB clocks can be totally independent

## System ACE Controller

- Used in conjunction with System ACE CompactFlash Solution to provide a System ACE memory solution.

- System ACE Microprocessor Interface (MPU)

- Read/Write from or to a CompactFlash device

- MPU provides a clock for proper synchronization

- ACE Flash (Xilinx-supplied Flash Cards)

- Densities of 128 MBits and 256 Mbits

- CompactFlash Type 1 form factor

- Supports any standard CompactFlash module, or IBM microdrives up to 8 Gbits, all with the same form factor.

- Handles byte, half-word, and word transfers

### **GPIO**

- OPB V2.0 bus interface with byte-enable support

- Supports 32-bit bus interface

- Each GPIO bit dynamically programmable as input or output

- Number of GPIO bits configurable up to size of data bus interface

- Can be configured as inputs-only to reduce resource utilization

# **Memory Controllers**

- PLB and OPB interfaces

- External Memory Controller

- Synchronous Memory (ZBT)

- Asynchronous Memory (SRAM, Flash)

- Internal Block Memory (BRAM) Controllers

- DDR and SDRAM

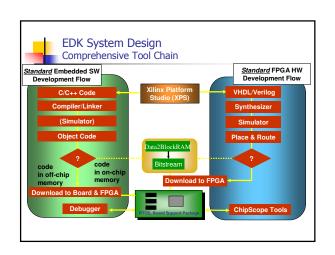

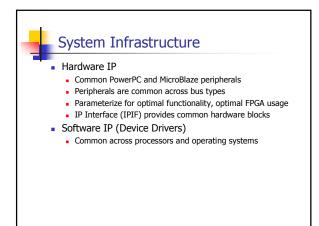

# Design Flow

- Design Entry with Xilinx Platform Studio

- Generate system netlist with XPS

- Generate hardware bitstream with XPS

- Download and sanity check design with XPS and XMD