## **Exceptions/Interrupts**

#### **Definition:**

- an "unexpected" event in the normal flow of execution

- interrupts, traps, faults, aborts, exceptions

- exceptions caused by instruction execution within the processor

- interrupts caused by some event external to the processor

#### Some examples:

- •

- .

- •

- •

- •

- •

- •

- .

CSE471

Susan Eggers

**Precise Interrupts**

**Precise interrupts** preserve the model that instructions execute in program-generated order

If an interrupt occurs, the processor can recover from it

What happens on a precise interrupt

- · identify the instruction that caused the interrupt

- pipelines execute several instructions at once: how determine which one caused the exception?

- · let the instructions before faulting instruction finish

- disable writes for faulting & subsequent instructions

- · force trap instruction into pipeline

- trap routine

- save the state of the executing program

- · correct the cause of the interrupt

- · restore program state

- restart faulting & subsequent instructions

CSE471 Susan Eggers 2

CSE471 Susan Eggers

## **How Pipelines Complicate Interrupts**

It's fairly simple to maintain precise interrupt in the R3000 integer pipeline

- one instruction fetched and executed each cycle

- instructions executed in fetch order

#### Simultaneous interrupts

- a solution: handle them in program order

- · still precise

#### Interrupts out of order wrt sequential instruction execution

- subsequent instruction causes an interrupt before a previous instruction

- interrupts still must be handled in program order for precise interrupts

- · interrupt handled before the write stage

- a solution: interrupt recorded in a per-instruction bit vector which flows with it down the pipeline interrupts for *this* instruction handled before it changes any state restart all instructions in the pipeline interrupts are precise: why?

CSE471 Susan Eggers

# **How Pipelines Complicate Interrupts**

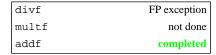

## **Multicycle operations**

- some types

- · floating point operations

- integer multiply & divide

- can cause imprecise interrupts because operations don't necessarily complete in program-generated order

- example:

- cannot restart interrupting & subsequent instructions because some have completed

- completed instruction may have overwritten one its source operands

CSE471 Susan Eggers