| Туре                                    | When inputs are sampled                                               | When output is valid                                                      |

|-----------------------------------------|-----------------------------------------------------------------------|---------------------------------------------------------------------------|

| unclocked<br>latch                      | always                                                                | propagation delay from input change                                       |

| level-sensitive<br>latch                | clock high<br>(Tsu/Th around falling<br>edge of clock)                | propagation delay from input change<br>or clock edge (whichever is later) |

| master-slave<br>flip-flop               | clock high<br>(Tsu/Th around falling<br>edge of clock)                | propagation delay from falling edge of clock                              |

| negative<br>edge-triggered<br>flip-flop | clock hi-to-lo transition<br>(Tsu/Th around falling<br>edge of clock) | propagation delay from falling edge of clock                              |

## Summary of latches and flip-flops

- Bevelopment of D-FF

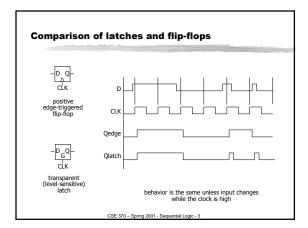

⊡ level-sensitive used in custom integrated circuits

⊠can be made with 4 switches

⊡ edge-triggered used in programmable logic devices

- G good choice for data storage register

Historically J-K FF was popular but now never used

G similar to R-S but with 1-1 being used to toggle output (complement state)

G good in days of TTL/SSI (more complex input function: D = JQ' + K'Q

G not a good choice for PALs/PLAs as it requires 2 inputs

G can always be implemented using D-FF

CSE 370 - Spring 2001 - Sequential Logic - 9

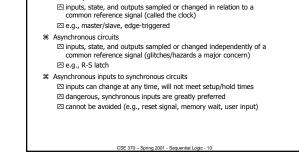

Metastability and asynchronous inputs

# Clocked synchronous circuits