# Lecture 12: Time and Glitches

CSE 370, Autumn 2007 Benjamin Ylvisaker

### Where We Are

• Last lecture: Multi-Level Logic

• This lecture: Circuit Delay and Timing

• Next lecture: Adders, Comparators, ALUs

• Exam 1 on Wednesday

• Homework 4 in progress

• Lab 4 this week

University of Washington, Comp. Sci. and Eng.

CSE 370, Autumn, 2007, Lecture 12

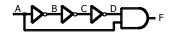

### Sometimes Time Matters

University of Washington, Comp. Sci. and Eng.

CSE 370, Autumn, 2007, Lecture 12

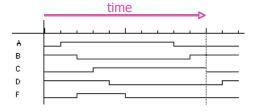

#### Glitches and Hazards

University of Washington, Comp. Sci. and Eng.

CSE 370, Autumn, 2007, Lecture 12

### Where Glitches Come From

University of Washington, Comp. Sci. and Eng.

CSE 370, Autumn, 2007, Lecture 12

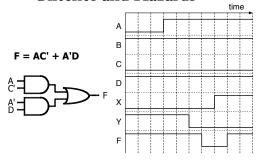

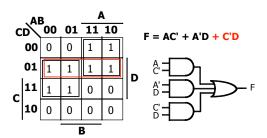

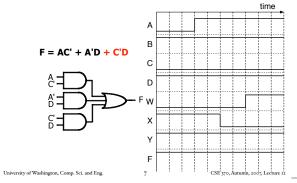

#### Avoiding Glitches in 2-Level Circuits

#### Additional Gate Prevents Glitches

## Terminology of Hazards

- Static 1-Hazard

- Static o-Hazard 0

- Dynamic Hazards  $\begin{bmatrix} 1 & 1 & 1 \\ 0 & 1 & 1 \end{bmatrix}$

University of Washington, Comp. Sci. and Eng.

CSE 370, Autumn, 2007, Lecture 12

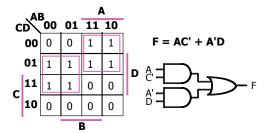

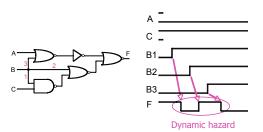

## A Dynamic Hazard

## Avoiding Dynamic Hazards

- Very hard

- Automated tools can help

- In practice, use 2-level circuits if you must avoid hazards at all costs

University of Washington, Comp. Sci. and Eng.

10

CSE 370, Autumn, 2007, Lecture 12

#### Now You Try

- $F(A,B,C,D) = \neg AB + A\neg CD + \neg BCD$

- Draw waves that illustrate one input pattern/ transition that can cause a glitch, and identify which gates would have to be slow or fast

- Change the circuit to make it hazard-free and draw the resulting circuit

University of Washington, Comp. Sci. and Eng.

...

CSE 370, Autumn, 2007, Lecture 12

#### Thank You for Your Attention

- Read lab 4

- Study for the exam

- Continue working on homework 4

- Continue reading the book