#### Lecture 25 Last lecture

#### Logistics

- HW9 and Ant extra credit problem are due now

- All lab must be done by 6pm today.

- Review session tomorrow CSE403 11:30am

- Final Exam 6/9 here 8:30am

#### Today

- Review materials from the entire class

- Announcement of final exam extra credit problem

- Evaluation: me and Nikhil (leave last 15 min for this)

- Tomorrow: can take more questions and go over examples.

CSE370, Lecture 25

### What you should know

- Combinational logic basics

- Binary/hex/decimal numbers

- Ones and twos complement arithmetic

- Truth tables

- Boolean algebra

- Basic logic gates

- Schematic diagrams

- Timing diagrams

- de Morgan's theorem

- AND/OR to NAND/NOR logic conversion

- K-maps (up to 4 variables), logic minimization, don't cares

- SOP, POS

- Minterm and maxterm expansions (canonical, minimized)

CSE370, Lecture 25 2

### What you should know

- Combinational logic applications

- Combinational design

- ∠ K-map

- **∠** Boolean equation

- ✓ Schematics

- Multiplexers/demultiplexers

- PLAs/PALs

- ROMs

- Adders

CSE370, Lecture 25

3

# What you should know

- Sequential logic building blocks

- Latches (R-S and D)

- Flip-flops (D and T)

- Latch and flip-flop timing (setup/hold time, prop delay)

- Timing diagrams

- Asynchronous inputs and metastability

- Registers

CSE370, Lecture 25

4

### What you should know

- Counters

- Timing diagrams

- Shift registers

- Ring counters

- State diagrams and state-transition tables

- Counter design procedure

- 1. Draw a state diagram

- 2. Draw a state-transition table

- 3. Encode the next-state functions

- 4. Implement the design

- Self-starting counters

CSE370, Lecture 25

### What you should know

- Finite state machines

- Timing diagrams (synchronous FSMs)

- Moore versus Mealy versus synchronized Mealy

- FSM design procedure

- 1. State diagram

- 2. state-transition table

- 3. State minimization

- 4. State encoding

- 5. Next-state logic minimization

- 6. Implement the design

- State minimization

- One-hot / output-oriented encoding

- FSM design guidelines

- **∠** Separate datapath and control

- Pipelining, retiming partitioning basics

CSE370, Lecture 25

## Partitioning rules

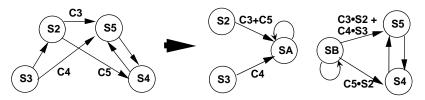

Rule #1: Source-state transformation Replace by transition to idle state (SA)

Rule #2: Destination state transformation Replace with exit transition from idle state

CSE370, Lecture 25

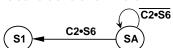

### Partitioning rules (con't)

Rule #3: Multiple transitions with same source or destination Source ⇒ Replace by transitions to idle state (SA) Destination ⇒ Replace with exit transitions from idle state

Rule #4: Hold condition for idle state OR exit conditions and invert

CSE370, Lecture 25

8

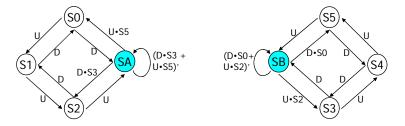

# Example: 6 state up/down counter (con't)

- ◆ Count sequence S<sub>0</sub>, S<sub>1</sub>, S<sub>2</sub>, S<sub>3</sub>, S<sub>4</sub>, S<sub>5</sub>

S<sub>2</sub> goes to S<sub>A</sub> and holds, leaves after S<sub>5</sub>

S<sub>5</sub> goes to S<sub>B</sub> and holds, leaves after S<sub>2</sub>

Down sequence is similar

CSE370, Lecture 25