### Overview

- Last lecture

- Finished counter design

- ∠ Design example

- ✓ Self-starting counters

- Today

- Introduction to finite-state machines

- **∠** Example: A parity checker

CSE370, Lecture 20

#### Finite state machines

- ◆ FSM: A system that visits a finite number of logically distinct states

- Counters are simple FSMs

- Outputs and states are identical

- Visit states in a fixed sequence

- FSMs are more complex than counting

- Outputs can depend on current state and on inputs

- State sequencing depends on current state and on inputs

2

CSE370, Lecture 20

CSE370, Lecture 20

CSE370, Lecture 20

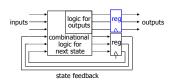

Generalized FSM model

- ◆ State variables (state vector) holds circuit state

- Stored in registers

- ◆ Combinational logic computes next state and outputs

- Next state is a function of current state and inputs

- Outputs are functions of

- ∠ Current state (Moore machine)

CSE370, Lecture 20

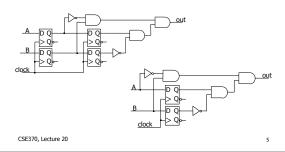

Moore versus Mealy machines Moore machine

Outputs are a function inputsmbinational logic for next state logic for → outputs Outputs change synchronously with state changes logic for Mealy machine Outputs depend on state mbinationa and on inputs logic for next state Input changes can cause immediate output changes

(asynchronous) state feedback

# Example: Moore versus Mealy

- ◆ Circuits recognize AB=10 followed by AB=01

- What kinds of machines are they?

#### Specifying outputs for a Moore machine Output is a function of state only Specify output in the state bubble Example: Detector for 01 or 10 current reset input state output B C B 0 0 0 A B reset D (A/0) В CCDDEECECB 0

# Specifying outputs for a Mealy machine

- Output is a function of state and inputs

- Specify outputs on transition arcsExample: Detector for 01 or 10

| reset | input | current<br>state | next<br>state | current<br>output |

|-------|-------|------------------|---------------|-------------------|

| 1     | -     | _                | Α             | 0                 |

| 0     | 0     | Α                | В             | 0                 |

| 0     | 1     | Α                | С             | 0                 |

| 0     | 0     | В                | В             | 0                 |

| 0     | 1     | В                | С             | 1                 |

| 0     | 0     | С                | В             | 1                 |

| 0     | 1     | С                | С             | 0                 |

|       |       |                  | ı             |                   |

|       |       |                  |               |                   |

CSE370, Lecture 20

# Comparing Moore and Mealy machines

- Moore machines

- Safer do use because outputs change at clock edge

May take additional logic to decode state into outputs

- Mealy machines

- + Typically have fewer states

- + React faster to inputs don't wait for clock

Asynchronous outputs can be dangerous

- We will often design synchronous Mealy machines

- Design a Mealy machine

- Then register the outputs

CSE370, Lecture 20

Synchronous (registered) Mealy machine

- ◆ Registered state and registered outputs

- No glitches on outputs

- No race conditions between communicating machines

CSE370, Lecture 20

FSM design

- Generalized counter design

- Counter-design procedure

- 1. State diagram

- 2. State-transition table

- 3. Next-state logic minimization

- 4. Implement the design

- FSM-design procedure

- 1. State diagram and state-transition table State minimization

- 3. State assignment (or state encoding)

- 4. Next-state logic minimization

- 5. Implement the design

CSE370, Lecture 20

10

### Example: A parity checker

Serial input string

CSE370, Lecture 20

- OUT=1 if odd # of 1s in input

- OUT=0 if even # of 1s in input

- 1. State diagram and state-transition table

| 0<br>Even<br>[0] | \            | Present<br>State           | Input            | Next<br>State              | Present<br>Output |

|------------------|--------------|----------------------------|------------------|----------------------------|-------------------|

| Odd [1]          | ı            | Even<br>Even<br>Odd<br>Odd | 0<br>1<br>0<br>1 | Even<br>Odd<br>Odd<br>Even | 0<br>0<br>1<br>1  |

| J.O.             | Moore-machin | ne state diag              | ram              |                            |                   |

### Parity checker (con't)

- 2. State minimization: Already minimized

- Need both states (even and odd)

- Use one flip-flop

- 3. State assignment (or state encoding)

| Present<br>State | Input | Next<br>State | Present<br>Output |

|------------------|-------|---------------|-------------------|

| 0                | 0     | 0             | 0                 |

| 0                | 1     | 1             | 0                 |

| 1                | 0     | 1             | 1                 |

| 1                | 1     | 0             | 1                 |

|                  |       | I             |                   |

Assignment Even = 0Odd = 1

12

CSE370, Lecture 20

11

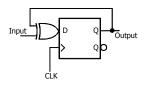

# Parity checker (con't)

- Next-state logic minimization

Assume D flip-flops

- Next state = (present state) XOR (present input)

Present output = present state

- 5. Implement the design

CSE370, Lecture 20

13

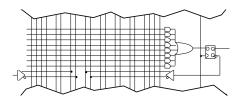

# Implementation

- ◆ Can map FSMs to programmable logic devices

Macro-cell = DFF + two-level logic

• Other options: Gate arrays, semicustom ICs, etc.

CSE370, Lecture 20

14