# Realizing Boolean logic

- Algebraic expressions to gates

- Mapping between different gates

- Discrete logic gate components (used in lab 1)

Winter 2010

CSE370 - III - Realizing Boolean Logic

# A simple example: 1-bit binary adder

- Inputs: A, B, Carry-in

- Outputs: Sum, Carry-out

| <i>(</i> | <b>}</b> | Co     | ut C   | in<br>∐√ | $\mathcal{L}$ | 1 |

|----------|----------|--------|--------|----------|---------------|---|

|          | A<br>B   | A<br>B | A<br>B | A<br>B   | A<br>B        |   |

|          | S        | S      | S      | S        | S             |   |

| Α | В | Cin | Cout | S |  |

|---|---|-----|------|---|--|

| 0 | 0 | 0   | 0    | 0 |  |

| 0 | 0 | 1   | 0    | 1 |  |

| 0 | 1 | 0   | 0    | 1 |  |

| 0 | 1 | 1   | 1    | 0 |  |

| 1 | 0 | 0   | 0    | 1 |  |

| 1 | 0 | 1   | 1    | 0 |  |

| 1 | 1 | 0   | 1    | 0 |  |

| 1 | 1 | 1   | 1    | 1 |  |

S = A' B' Cin + A' B Cin' + A B' Cin' + A B Cin Cout = A' B Cin + A B' Cin + A B Cin' + A B Cin

Winter 2010

CSE370 - III - Realizing Boolean Logic

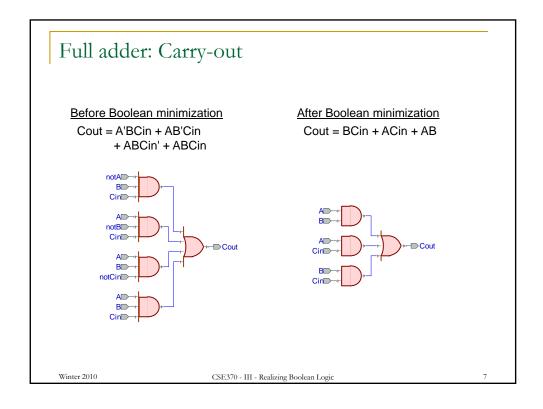

## Apply the theorems to simplify expressions

- The theorems of Boolean algebra can simplify expressions

- e.g., full adder's carry-out function

```

Cout

= A' B Cin + A B' Cin + A B Cin' + A B Cin

= A' B Cin + A B' Cin + A B Cin' + A B Cin + A B Cin

= A' B Cin + A B Cin + A B' Cin + A B Cin' + A B Cin

= (A' + A) B Cin + A B' Cin + A B Cin' + A B Cin

= (1) B Cin + A B' Cin + A B Cin' + A B Cin

= B Cin + A B' Cin + A B Cin' + A B Cin + A B Cin

= B Cin + A B' Cin + A B Cin + A B Cin' + A B Cin

= B Cin + A (B' + B) Cin + A B Cin' + A B Cin

= B Cin + A (1) Cin + A B Cin' + A B Cin

= B Cin + A Cin + A B (Cin' + Cin)

= B Cin + A Cin + A B (1)

adding extra terms

= B Cin + A Cin + A B

creates new factoring

opportunities

Winter 2010

CSE370 - III - Realizing Boolean Logic

```

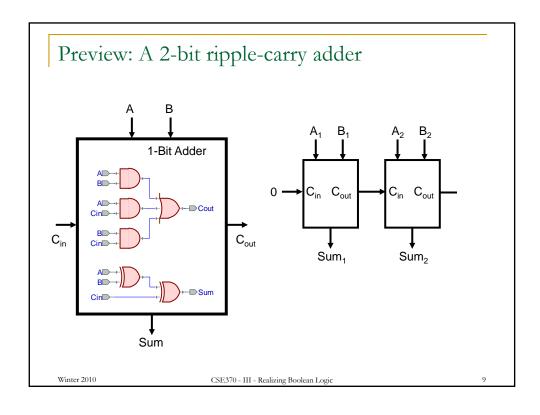

## A simple example: 1-bit binary adder

- Inputs: A, B, Carry-in

- Outputs: Sum, Carry-out

| f | <b>}</b> | Co     | ut C   | in<br>}√ | 7      | ì |

|---|----------|--------|--------|----------|--------|---|

|   | A<br>B   | A<br>B | A<br>B | A<br>B   | A<br>B |   |

|   | S        | S      | S      | S        | S      |   |

| В | Cin                   | Cout                            | S                                                    |

|---|-----------------------|---------------------------------|------------------------------------------------------|

| 0 | 0                     | 0                               | 0                                                    |

| 0 | 1                     | 0                               | 1                                                    |

| 1 | 0                     | 0                               | 1                                                    |

| 1 | 1                     | 1                               | 0                                                    |

| 0 | 0                     | 0                               | 1                                                    |

| 0 | 1                     | 1                               | 0                                                    |

| 1 | 0                     | 1                               | 0                                                    |

| 1 | 1                     | 1                               | 1                                                    |

|   | 0<br>0<br>1<br>1<br>0 | 0 0<br>0 1<br>1 0<br>1 1<br>0 0 | 0 0 0<br>0 1 0<br>1 0 0<br>1 1 1 1<br>0 0 0<br>0 1 1 |

$$\begin{array}{c} A \\ B \\ \hline \\ Cin \end{array} \longrightarrow \begin{array}{c} S \\ \hline \\ \end{array} \longrightarrow \begin{array}{c} Cout \\ \end{array}$$

$$Cout = B Cin + A Cin + A B$$

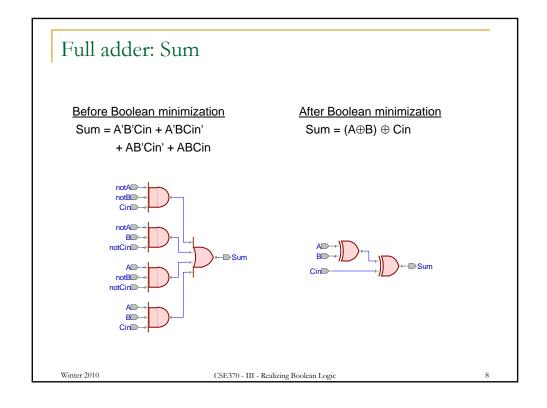

$$S = A' B' Cin + A' B Cin' + A B' Cin' + A B Cin$$

=  $A' (B' Cin + B Cin') + A (B' Cin' + B Cin)$

=  $A' Z + A Z'$

=  $A xor Z = A xor (B xor Cin)$

Winter 2010

CSE370 - III - Realizing Boolean Logic

## From Boolean expressions to logic gates

Winter 2010

CSE370 - III - Realizing Boolean Logic

From Boolean expressions to logic gates (cont'd)

NOR

XOR X ⊕ Y

XNOR X = Y

X xnor Y = X Y + X' Y' X and Y are the same ("equality", "coincidence")

Winter 2010

CSE370 - III - Realizing Boolean Logic

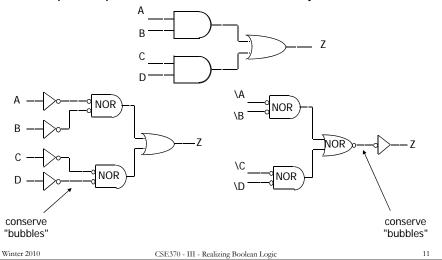

## Conversion between gate types

Example: map AND/OR network to NOR-only network

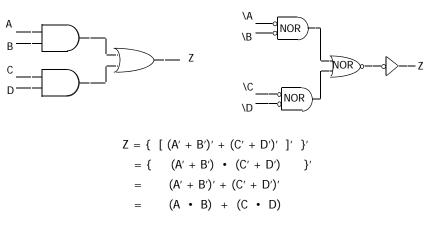

# Conversion between gate types (cont'd)

Example: verify equivalence of two forms

Winter 2010

CSE370 - III - Realizing Boolean Logic

# Activity: convert to NAND gates Activity: convert to NAND gates Activity: convert to NAND gates Activity: convert to NAND gates

# Example: tally circuit (outputs # of 1s in inputs)

| X1 | X2 | Х3 | T2 | T1 |                                                                |

|----|----|----|----|----|----------------------------------------------------------------|

| 0  | 0  | 0  | 0  | 0  |                                                                |

| 0  | 0  | 1  | 0  | 1  |                                                                |

| 0  | 1  | 0  | 0  | 1  | T1 = X1' X2' X3 + X1' X2 X3'                                   |

| 0  | 1  | 1  | 1  | 0  | + X1 X2' X3' + X1 X2 X3                                        |

| 1  | 0  | 0  | 0  | 1  |                                                                |

| 1  | 0  | 1  | 1  | 0  | = (X1' X2' + X1 X2) X3                                         |

| 1  | 1  | 0  | 1  | 0  | + (X1' X2 + X1 X2') X3'                                        |

| 1  | 1  | 1  | 1  | 1  | = (X1 xor X2)' X3<br>+ (X1 xor X2) X3'<br>= (X1 xor X2) xor X3 |

|    |    |    |    |    | T2 = X1' X2 X3 + X1 X2' X3                                     |

|    |    |    |    |    | + X1 X2 X3' + X1 X2 X3                                         |

|    |    |    |    |    | = X1' (X2 X3) + X1 (X2 +                                       |

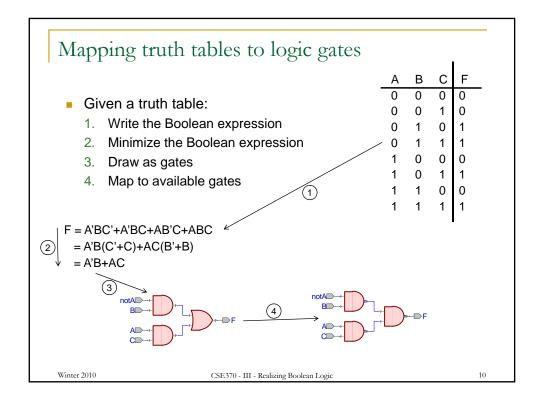

# From Boolean expressions to logic gates

More than one way to map expressions to gates

$$\circ$$

e.g.,  $Z = A' \bullet B' \bullet (C + D) = (A' \bullet (B' \bullet (C + D)))$

use of 3-input gate

Winter 2010

CSE370 - III - Realizing Boolean Logic

15

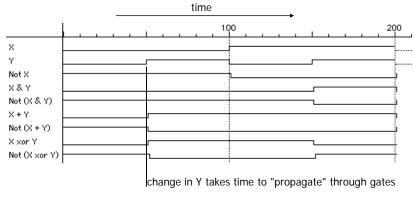

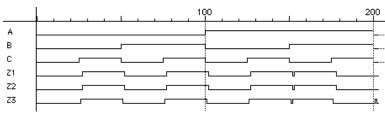

## Waveform view of logic functions

- Just a sideways truth table

- but note how edges don't line up exactly

- it takes time for a gate to switch its output!

Winter 2010

CSE370 - III - Realizing Boolean Logic

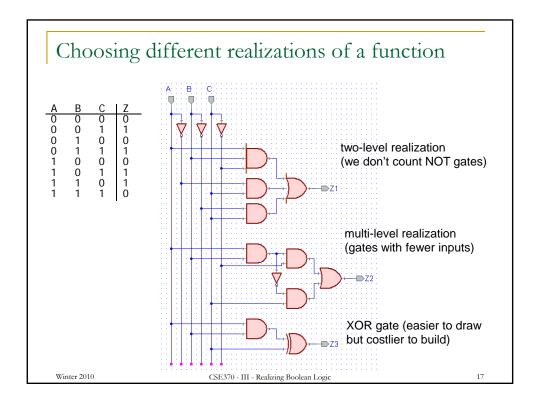

## Are all realizations equivalent?

- Under the same input stimuli, the three alternative implementations have almost the same waveform behavior

- delays are different

- □ glitches (hazards) may arise these could be bad, it depends

- variations due to differences in number of gate levels and structure

- The three implementations are functionally equivalent

Winter 2010 CSE370 - III - Realizing

### Which realization is best?

- Reduce number of inputs

- literal: input variable (complemented or not)

- can approximate cost of logic gate as 2 transistors per literal

- why not count inverters?

- fewer literals means less transistors

- smaller circuits

- fewer inputs implies faster gates

- gates are smaller and thus also faster

- fan-ins (# of gate inputs) are limited in some technologies

- the programmable logic we'll be using later in the quarter

- Reduce number of gates

- fewer gates (and the packages they come in) means smaller circuits

- directly influences manufacturing costs

Winter 2010

CSE370 - III - Realizing Boolean Logic

19

#### Which realization is best? (cont'd)

- Reduce number of levels of gates

- fewer level of gates implies reduced signal propagation delays

- minimum delay configuration typically requires more gates

- wider, less deep circuits

- Hazards/glitches

- one without hazards may be preferable/necessary

- How do we explore tradeoffs between increased circuit delay and size?

- automated tools to generate different solutions

- logic minimization: reduce number of gates and complexity

- logic optimization: reduction while trading off against delay

Winter 2010

CSE370 - III - Realizing Boolean Logic

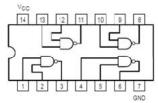

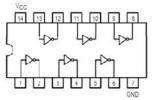

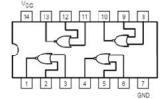

## Random logic gates

- Transistors quickly integrated into logic gates (1960s)

- Catalog of common gates (1970s)

- Texas Instruments Logic Data Book the yellow "bible"

- all common packages listed and characterized (delays, power)

- typical packages:

- in 14-pin IC: 6-inverters, 4 NAND gates, 4 XOR gates

- Today, very few of these parts are still in use

- However, parts libraries exist for chip design

- designers reuse already characterized logic gates on chips

- same reasons as before

- difference is that the parts don't exist in physical inventory created as needed

Autumn 2006

CSE370 -  $\underline{V}$  - Implementation Technologies

21

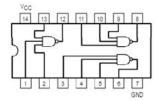

## Some logic gate components

Quad 2-input NANDs - '00

6 inverters (NOTs) - '04

Quad 2-input NORs - '02

3 3-input NANDs - '10

Winter 2010

CSE370 - III - Realizing Boolean Logic