| Shift register                                                      | in Verilog                          |   |

|---------------------------------------------------------------------|-------------------------------------|---|

| module shift_req<br>input clk;<br>input in;<br>output [0:3] c       | rister (clk, in, out);<br>put;      |   |

| <pre>reg [0:3] out;<br/>initial begin<br/>out = 0; //<br/>end</pre> | <pre>out[0:3] = {0, 0, 0, 0};</pre> |   |

| always @(posed<br>out = {in, o<br>end                               |                                     |   |

| endmodule                                                           |                                     |   |

| Autumn 2010                                                         | CSE370 - XV - Sequential Verilog    | 8 |

| 5                                                                                    | erilog                                                                                                                   |

|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| module binary_counter (clk, c8, c4, c2,                                              | , c1); add RCO                                                                                                           |

| input clk;                                                                           | module binary_counter (clk, c8, c4, c2, c1, rco)                                                                         |

| output c8, c4, c2, c1;<br>reg [3:0] count;                                           | <pre>input clk;<br/>output c8, c4, c2, c1, rco;</pre>                                                                    |

| <pre>initial begin</pre>                                                             | <pre>reg [3:0] count;<br/>reg rco;</pre>                                                                                 |

| always @(posedge clk) begin<br>count = count + 4'b0001;<br>end                       | initial begin end                                                                                                        |

| <pre>assign c8 = count[3];<br/>assign c4 = count[2];<br/>assign c2 = count[1];</pre> | <pre>always @(posedge clk) begin end<br/>assign c8 = count[3];<br/>assign c4 = count[2];<br/>assign c2 = count[1];</pre> |

| <pre>assign c1 = count[0];<br/>endmodule</pre>                                       | <pre>assign c1 = count[0];<br/>assign rco = (count == 4b'1111);<br/>endmodule</pre>                                      |

```

if

Same as Java/C if statement

// Simple 4-1 mux

module mux4 (sel, A, B, C, D, Y);

input [1:0] sel;

// 2-bit control signal

input A, B, C, D;

output Y;

reg Y;

// target of assignment

always @(sel or A or B or C or D)

if

(sel == 2'b00) Y = A;

else if (sel == 2'b01) Y = B;

else if (sel == 2'b10) Y = C;

else if (sel == 2'b11) Y = D;

endmodule

\Rightarrow Single if statements synthesize to multiplexers

\Rightarrow Nested if /else statements usually synthesize to logic

Autumn 2010

21

CSE370 - XV - Sequential Verilog

```

```

if (another way)

// Simple 4-1 mux

module mux4 (sel, A, B, C, D, Y);

input [1:0] sel;

// 2-bit control signal

input A, B, C, D;

output Y;

// target of assignment

reg Y;

always @(sel or A or B or C or D)

if (sel[0] == 0)

if (sel[1] == 0) \quad Y = A;

Y = B;

else

else

if (sel[1] == 0) Y = C;

Y = D;

else

endmodule

Autumn 2010

CSE370 - XV - Sequential Verilog

22

```

```

case

// Simple 4-1 mux

module mux4 (sel, A, B, C, D, Y);

input [1:0] sel;

// 2-bit control signal

input A, B, C, D;

output Y;

// target of assignment

reg Y;

always @(sel or A or B or C or D)

case (sel)

2'b00: Y = A;

2'b01: Y = B;

2'b10: Y = C;

2'b11: Y = D;

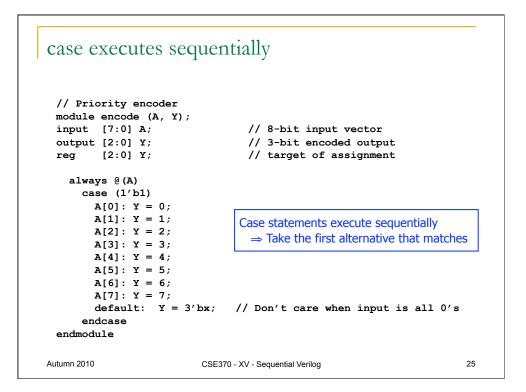

case executes sequentially

endcase

\Rightarrow First match executes

endmodule

\Rightarrow Don't need to break out of case

case statements synthesize to muxes

Autumn 2010

CSE370 - XV - Sequential Verilog

23

```

| default case                                                                                                                                                                 |                                                                                                                                             |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|----|

| <pre>// Simple binary en<br/>module encode (A, Y<br/>input [7:0] A;<br/>output [2:0] Y;<br/>reg [2:0] Y;</pre>                                                               | <pre>coder (input is 1-hot) - comb. logic );</pre>                                                                                          |    |

| always @(A)<br>case (A)<br>8'b0000001:<br>8'b0000010:<br>8'b0001000:<br>8'b00010000:<br>8'b00100000:<br>8'b01000000:<br>8'b10000000:<br>default: Y =<br>endcase<br>endmodule | Y = 1;       the compiler will create         Y = 2;       a latch for Y - not good         Y = 3;       y = 4;         Y = 5;       y = 6; |    |

| Autumn 2010                                                                                                                                                                  | CSE370 - XV - Sequential Verilog                                                                                                            | 24 |

```

for

// simple encoder

module encode (A, Y);

input [7:0] A;

// 8-bit input vector

// 3-bit encoded output

output [2:0] Y;

reg

[2:0] Y;

// target of assignment

// Temporary variables for program

integer i;

[7:0] test;

reg

always @(A) begin

test = 8b'0000001;

Y = 3' bx;

for (i = 0; i < 8; i = i + 1) begin

if (A == test) Y = i;

test = test << 1; // Shift left, pad with 0s</pre>

end

end

for statements synthesize as

endmodule

cascaded combinational logic

\Rightarrow Verilog unrolls the loop

Autumn 2010

CSE370 - XV - Sequential Verilog

26

```