# **CSE370 Final Exam (Dec 14, 1999)**

There are 4 problems for a total of 100 points. The point value of each problem is indicated in the table below. I will try to stick to the point values this time!

Each problem is on a separate sheet of paper. Write your answer neatly in the space provided. If you need more space (you shouldn't), there are a couple of extra sheets at the end of the exam, but please make sure that you indicate clearly the problem to which the comments apply.

Please do not ask or provide anything to anyone else in the class during the exam. Make sure to ask clarification questions early so that both you and the others may benefit as much as possible form the answers.

Problem 1 (18): \_\_\_\_

Problem 2 (24): \_\_\_\_

Problem 3 (28): \_\_\_\_

Problem 4 (30): \_\_\_\_

#### Problem 1: Carry Lookahead.

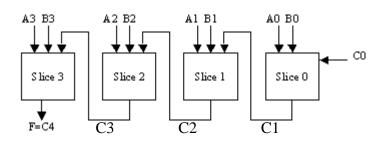

A four-bit ripple carry comparator (F= A>B) is shown below. In general,  $C_{i+1} = 1$  if  $\{Ai..A0\} > \{Bi..B0\}$ . For example, C2 is true if (A1A0 > B1B0), so F = C4.

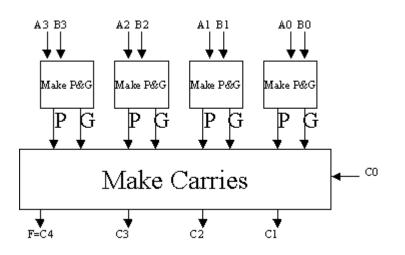

A carry lookahead design of the same function is shown below.

## Part A: Make P&G (9)

Determine the Boolean logic equations for Pi and Gi given Ai and Bi.

- Gi = 1 if and only if Ai and Bi generate a carry

- Pi = 1 if and only if Ai and Bi propagate a carry, but do not generate one.

Find POS expressions for Pi(Ai,Bi) and Gi(Ai,Bi), show your work.

Pi =\_\_\_\_\_

Gi =\_\_\_\_\_

| Ν | ame | : |

|---|-----|---|

|   |     |   |

## Part B. Make Carries. (9)

Write a two level equation for C4(Co, P3..P0, G3..G0). It might help for you to write the equations for C1,C2, and C3 first to get the idea.

C4 = \_\_\_\_\_

If all gates count as 1 delay (except input inversions), what is the worst delay from any input to C4. Explain.

## **Problem 2: Storage Elements**

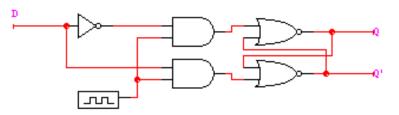

Consider the storage element shown below.

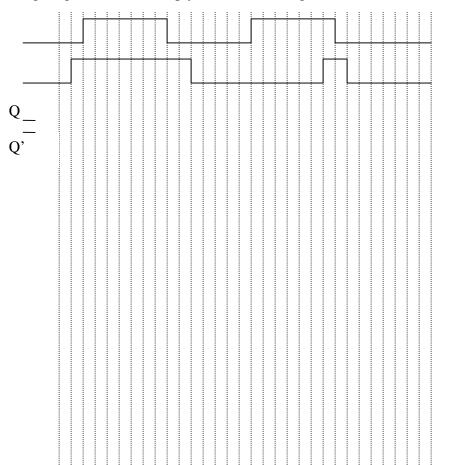

**Part A (12).** Assuming all gates have a 10ns delay (including the inverter) complete the timing diagram below, each time division is 10ns. Feel free to add additional signals to the timing diagram if it will help you think it through.

**Part B** (12pts). What are the setup, hold, and propagation delays for this storage element (see definitions below). In each case, be specific about the edge of the clock from which you are measuring time. Explain your answers.

- Tprop is defined as the CLK to Q delay, assuming that D is stable.

- Tsu is defined as the minimum time before the latching clock edge during which D must remain stable to ensure proper operation of the latch

- Th is defined as the minimum time after the latching clock edge during which D must remain stable to ensure proper operation of the latch.

## 3. State Machine Design

Design a 2-bit synchronous "skip counter" that has two control inputs: C (for "count") and S (for "skip"). If C is asserted then the value in the counter will be incremented by 1. If C is not asserted and S is asserted then the value in the counter will be incremented by 2, otherwise the value in the counter remains unchanged. The system has two outputs V1and V0 that indicate the current value of the count. The following table fully specifies the function of the skip-counter:

| С                     | S | Cur.<br>State | Next<br>State | V1,V0 |  |

|-----------------------|---|---------------|---------------|-------|--|

| 0                     | 0 | n             | n             | n     |  |

| 0                     | 1 | n             | n+2           | n     |  |

| 1                     | - | n             | n+1           | n     |  |

| Where $0 \le n \le 3$ |   |               |               |       |  |

Part A (14). Draw the complete finite state machine diagram.

**Part B** (14). Using *output encoding*, and positive edge triggered D flip-flops, determine the minimized two-level next state functions and draw the complete state machine schematic clearly indicating inputs and outputs. Assuming 1 time unit per gate, Tsu = 4, and Tp = 2, what is the minimum clock period for your counter?

## **Problem 4. Controller Design**

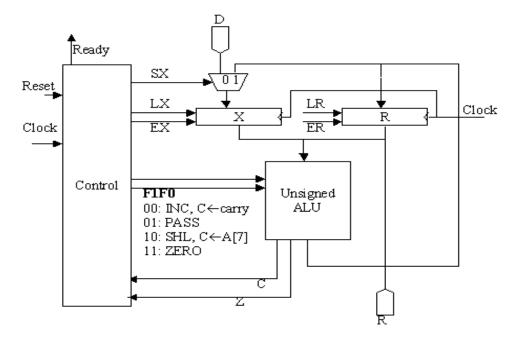

Given the following 8-bit datapath and associated control points, the problem is to

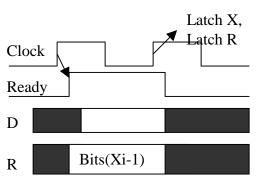

design a controller to count the number of 1's in the input data byte (D). The timing interface shown is the same as it was for the multiplier, except that there is only one data value to read. [When you assert Ready, the input data  $(X_i)$ value will be available on D until the end of that clock cycle, and you must ensure that the result of the previous

#### **Inputs and Control Points:**

- SX: Select D or ALU output to load into X (if LX is asserted)

- LX: Load X (1 is load, 0 is hold)

- EX: Enable X output (1 is enabled, 0 is tri-stated)

- ER: Enable R output (1 is enabled, 0 is tri-stated)

- LR: Load R (1 is load, 0 is hold)

- F1,F0: Opcode for ALU as defined above. ZERO sets the output to zero regardless of the inputs.

- D: Data input

#### Outputs

- Z: Zero condition code. Set any time the result of an ALU operation is zero

- C: Carry condition code. Set by SHL (C  $\leftarrow$  A[7]), and INC.

- R: Data output.

**Part A (15).** Design the controller state diagram. For each state, indicate the register transfer operation that is being performed and indicate which control lines are asserted in that state. You can use as many states as you like, but you shouldn't need more than FOUR. Be sure to identify your reset state.

**Part B.** Do one of the following two options. You do NOT need to come up with minimized expressions for your logic. Make sure to include the synchronous Reset input in your design.

**Option 1 (15):** If you can, implement your state machine using the 2-bit skip counter from Problem 4, slightly modified below, as your only storage element. The skip counter definition has been modified by the addition of an asynchronous reset input (R) as defined in the table below.

| R | C | S | Cur.<br>State | Next<br>State | Count (V1,V0) |

|---|---|---|---------------|---------------|---------------|

| 0 | 0 | 0 | n             | n             | n             |

| 0 | 0 | 1 | n             | n+2           | n             |

| 0 | 1 | - | n             | n+1           | n             |

| 1 | - | - | n             | 0             | n             |

| Modified 2-bit Skij | p Counter (1 | R input added) |

|---------------------|--------------|----------------|

|---------------------|--------------|----------------|

Where  $0 \le n \le 3$

**Option 2 (10):** Otherwise use a regular counter with R,L,C control inputs that work according the following function table. Your regular counter can have as many bits as you need.

#### **Regular m-bit counter (R input added)**

|   | R | L | C | D | Cur.<br>State | Next<br>State | Count<br>(VmV0) |

|---|---|---|---|---|---------------|---------------|-----------------|

| ĺ | 0 | 0 | 0 | - | n             | n             | n               |

|   | 0 | 0 | 1 | - | n             | n+1           | n               |

|   | 0 | 1 | - | m | n             | m             | n               |

|   | 1 | - | - | - | n             | 0             | n               |

Name:\_\_\_\_\_ Student No.\_\_\_\_\_

Name:\_\_\_\_\_ Student No.\_\_\_\_\_