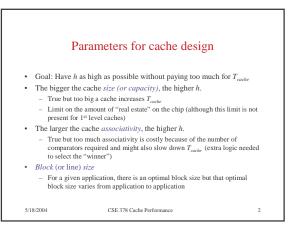

- Basic performance metric: *hit ratio h*

- h = Number of memory references that hit in the cache / total number of memory references Typically h = 0.90 to 0.97

- Equivalent metric: *miss rate* m = 1 -*h*

5/18/2004

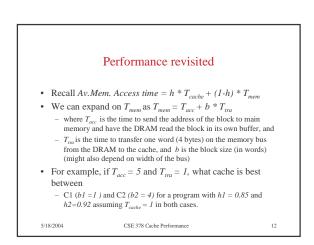

Other important metric: Average memory access time Av.Mem. Access time = h \* T<sub>cache</sub> + (1-h) \* T<sub>mem</sub> where T<sub>cache</sub> is the time to access the cache (e.g., 1 cycle) and T<sub>mem</sub> is the time to access main memory (e.g., 50 cycles) (Of course this formula has to be modified the obvious way if you have a hierarchy of caches)

CSE 378 Cache Performance

|                       | these num                                                | bers)                                                |

|-----------------------|----------------------------------------------------------|------------------------------------------------------|

| MICRO                 | L1                                                       | L2                                                   |

| Alpha 21064           | 8K(I), 8K(D), WT,<br>1-way, 32B                          | 128K to 8MB,WB,<br>1-way.32B                         |

| Alpha 21164           | 8K(I), 8K(D), WT,<br>1-way, 32B ,D l-u fr.               | 96K, WB, on-chip,<br>3-way,32B,l-u free              |

| Alpha 21264           | 64K(I), 64K(D),?,<br>2-way, ?                            | up to 16MB                                           |

| Pentium               | 8K(I),8K(D),both,<br>2-way, 32 B                         | Depends                                              |

| Pentium II,<br>III,IV | 16K(I),16K(D), WB,<br>4-way(I),2-way(D),<br>32B,1-u free | 256K-1MBK,32B,way,<br>on-chip or tightly-<br>coupled |

| PowerPC 620  | 32K(I),32K(D),WE<br>8-way, 64B   | B 1MB TO 128ME<br>WB, 1-way |

|--------------|----------------------------------|-----------------------------|

| MIPS R10000  |                                  |                             |

| UN UltraSpar | cIII 32K(I),64K(D),1-u,<br>4-way | 4-8MB 1-way                 |

| MD K7        | 64k(I), 64K(D)                   | 1                           |

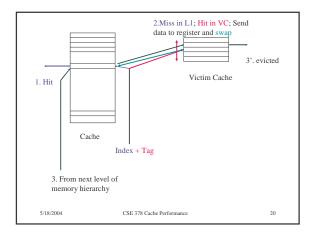

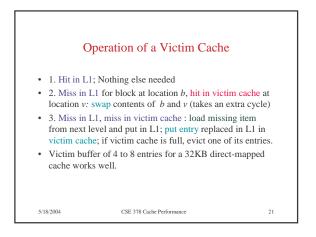

- Example of an "hardware assist"

- Victim cache: Small fully-associative buffer "behind" the cache and "before" main memory

- Of course can also exist if cache hierarchy

E.g., behind L1 and before L2, or behind L2 and before main memory)

- Main goal: remove some of the conflict misses in directmapped caches (or any cache with low associativity)

5/18/2004

CSE 378 Cache Performance

19