# Supporting an Operating System

### CSE 378 Spring 2009

## **Topics**

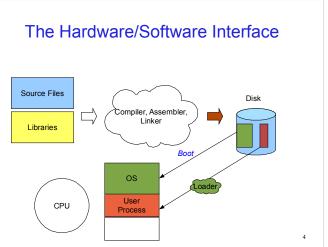

- We've seen how the ISA supports individual user applications

- You know how to "compile" C code, say, to assembler

- The instruction set we've seen is enough to implement all of C (for instance)

- How do computer systems work?

- What's the role of the ISA?

- What's the role of the OS?

- How are these related to the roles of the compiler, linker, loader?

2

1

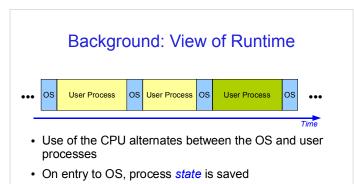

- PC and register contents written to save area in OS memory

- · Process dispatch is handing CPU back to a user process

- Reload register contents, and jump back to saved PC

### **Context For Today's Topics**

- The goal is "a computer system" that can do the sorts of things you're used to:

- I/O

- Run more than one app at a time, etc.

- Achieving this high level goal is an orchestration of:

- Software: the OS, linker, compiler, libraries, etc. have cooperating roles

- ISA: must provide some key functionality

- · This is particularly the case for allowing the OS to do things its responsible for

**Topics**

6

8

- Hardware: must implement the ISA

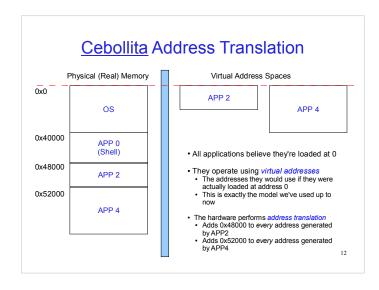

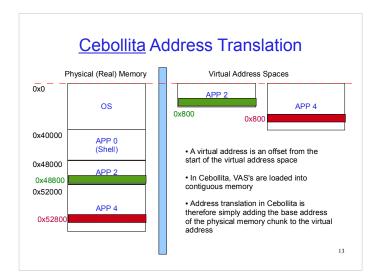

### Today vs. Tomorrow Today: · For concreteness, we'll be talking today about the - Address Translation (Virtual Memory) Cebollita architecture · Managing main memory - It contains most concepts required to understand a current - Exceptions (desktop) computer · Managing the CPU - The techniques used lie somewhere in the past on the - Memory Mapped Devices computer's evolutionary tree An implementation technique · We'll look at more modern virtual memory concepts a • Friday: little later in the course - I/O - More sophisticated OS facilities and implementations are CSE 451 - System calls 7

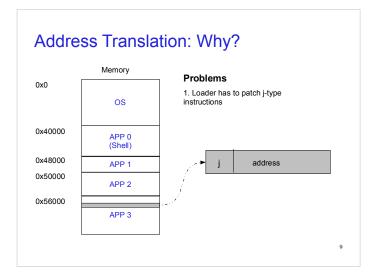

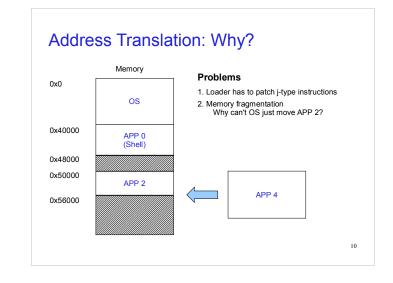

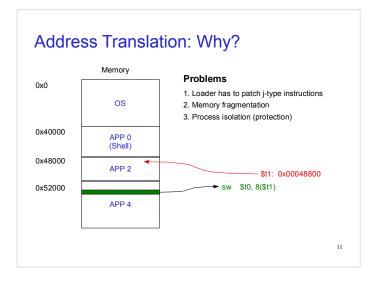

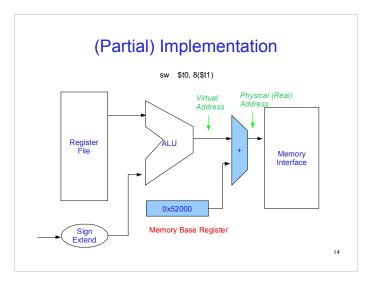

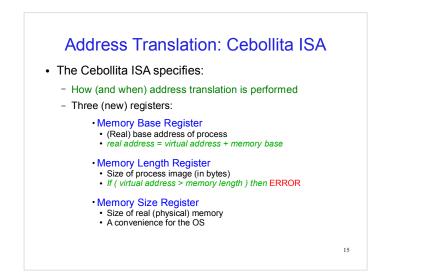

### Address Translation: OS

- · First pass overview:

- The loader (OS) finds enough contiguous memory to hold the new process image

- The process image is read from disk into that memory

- The memory base and length registers are set

Problem: What happens when mem base register is set?

- The OS jumps to the entry point of the new process

17

### Address Translation: Protection

- Process isolation is the most important benefit of (the Cebollita) address translation

- Process isolation requires checking access permission per-instruction

- There must be hardware support

- Virtual addresses provide isolation by making it impossible for one process to name the memory belonging to another process

- There is no memory address a process can utter that names the physical memory used by another process (so long as the OS makes no mistakes in setting the base register)

18

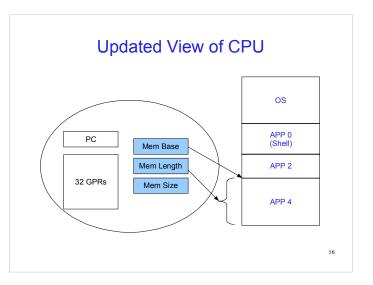

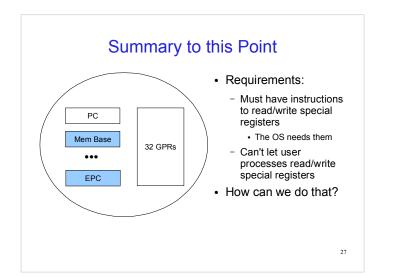

CPU

(virtual) Memory

PC

User

Mem Base

32 GPRs

Mem Size

Registers in blue are accessible only to the OS.

Chronic Memory

Registers in blue are accessible only to the OS.

Chronic Memory

Chronic Memory

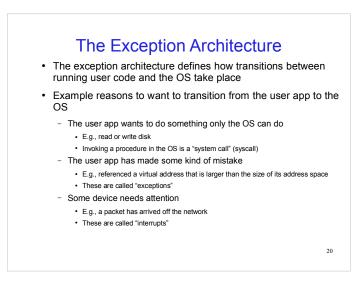

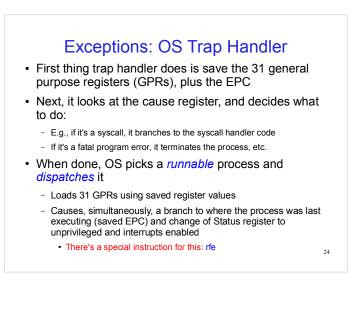

### The Cebollita Exception Architecture

- The ISA specifies four new registers:

- EPC: the PC when the exception/interrupt occurred

- Handler Address: what the PC should be set to

This is the address of the OS's *trap handler* routine

- Cause: indicates what happened

- E.g., 4 means addressing exception; 16 means overflow; 2 means disk needs attention

- Status: a bit mask

- Privilege bit: set to 1 if the OS is currently running; 0 if a user app

Interrupt enable bit: set to 0 to disable "raising exceptions/interrupts

21

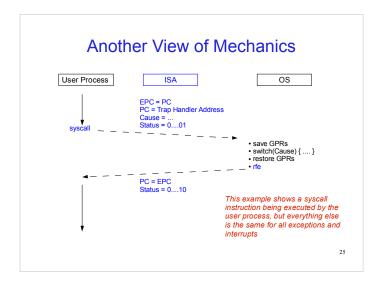

### **Exceptions: ISA**

- When an exception or interrupt occurs, if the interrupt enable bit is 0, ignore (or leave pending)

- · Otherwise, do all this in the current cycle:

- Save the current value of the PC in register EPC

- Set the PC to the value of the trap handler address register

- Set the value of the Cause register

- Update the status register:

- Set the privilege bit on (because the next instruction to be executed is the trap handler, in the OS)

22

Set the interrupt enable bit off

**Exceptions: ISA Mechanics** os Status: 0....10 Status: 0....01 Handler: 0x1E0 Handler: 0x1E0 Cause: xxxxx Cause: 4 EPC: XXXXX EPC: 0x200 User Process PC: 0x200 PC: 0x1E0 Before exception After exception This is the only way for a user process to "enter" the OS 23

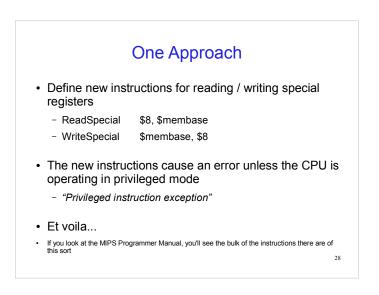

# Why Does This Work? OS can read / write these registers If a user process tries to read or write them: thas to construct and use an address no smaller than 0x40000000 That causes an addressing exception The memory allocated to it is smaller than that The address it issued is larger than the memory length register Addressing exception A side-effect of this design is that no virtual address space can be bigger than 0x4000000 bytes long Not a worry for us... Note: Physical memory could still be 2<sup>32</sup> bytes There'd be a chunk "missing"

# Summary

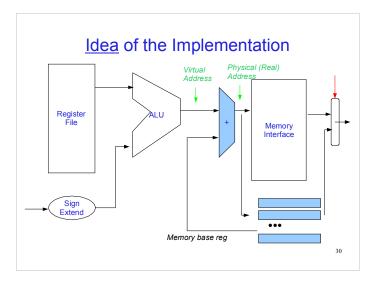

- Processes issue virtual addresses; hardware performs address translation to get real address

- Allows flexibility in use of main memory

- Provides process isolation / protection

- CPU have privileged and unprivileged modes

- Allows OS to do things user processes can't

- Exception architecture ensures that:

- The only way to go into privileged mode is to enter the OS

- The only place to enter the OS is the trap handler

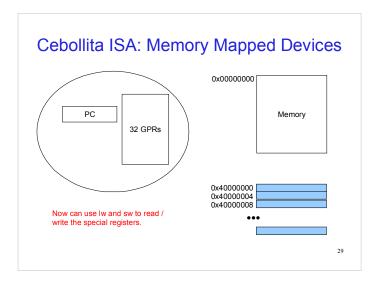

- Memory mapped devices exploits these properties to provide access to control registers without needing new instructions

32