# Do Not Open The Test Until Told To Do So

**MIPS** Reference Data

1

|                                     |            |        |                                                                     |           | 1000 C                                |

|-------------------------------------|------------|--------|---------------------------------------------------------------------|-----------|---------------------------------------|

| CORE INSTRUCTI                      | ON SE      | т      |                                                                     |           |                                       |

|                                     | MNE-       |        |                                                                     |           | OPCODE/                               |

|                                     | MON-       |        |                                                                     |           | FUNCT                                 |

| NAME                                | IC         | MAT    | ( <i>U</i>                                                          |           | (Hex)                                 |

| Add                                 | add        | R      | R[rd] = R[rs] + R[rt]                                               | (1)       | 0 / 20 <sub>hex</sub>                 |

| Add Immediate                       | addi       | I      | R[rt] = R[rs] + SignExtImm (1)                                      | )(2)      | 8 <sub>hex</sub>                      |

| Add Imm. Unsigned                   | addiu      | 1      | R[rt] = R[rs] + SignExtImm                                          | (2)       | 9 <sub>hex</sub>                      |

| Add Unsigned                        | addu       | R      | R[rd] = R[rs] + R[rt]                                               |           | 0 / 21 <sub>hex</sub>                 |

| And                                 | and        | R      | R[rd] = R[rs] & R[rt]                                               |           | 0 / 24 <sub>hex</sub>                 |

| And Immediate                       | andi       | 1      | R[rt] = R[rs] & ZeroExtImm                                          | (3)       | chex                                  |

| Branch On Equal                     | beq        | I      | if(R[rs]==R[rt])<br>PC=PC+4+BranchAddr                              | (4)       | 4 <sub>hex</sub>                      |

| Branch On Not Equa                  | bne        | I      | if(R[rs]!=R[rt])<br>PC=PC+4+BranchAddr                              | (4)       | 5 <sub>hex</sub>                      |

| Jump                                | j          | J      | PC=JumpAddr                                                         | (5)       | 2 <sub>bex</sub>                      |

| Jump And Link                       | jal        | J      | R[31]=PC+8;PC=JumpAddr                                              | (5)       | 3 <sub>bex</sub>                      |

| Jump Register                       | jr         | R      | PC=R[rs]                                                            |           | 0 / 08 <sub>hex</sub>                 |

|                                     | -          |        | R[rt]={24'b0,M[R[rs]                                                |           |                                       |

| Load Byte Unsigned<br>Load Halfword |            | 1      | R[rt]={16'b0,M[R[rs]                                                | (2)       | 24 <sub>hex</sub>                     |

| Unsigned<br>Load Upper Imm.         | lhu<br>lui | I<br>I | +SignExtImm](15:0)}<br>R[rt] = {imm, 16'b0}                         | (2)       | 25 <sub>hex</sub><br>f <sub>hex</sub> |

| Load Word                           | lw         | 1      | R[rt] = M[R[rs]+SignExtImm]                                         | (2)       | <sup>thex</sup><br>23 <sub>hex</sub>  |

|                                     |            |        |                                                                     | (2)       | 2-3hex                                |

| Nor                                 | nor        | R      | $R[rd] = \sim (R[rs]   R[rt])$                                      |           | 0 / 27 <sub>hex</sub>                 |

| Or                                  | or         | R      | R[rd] = R[rs]   R[rt]                                               |           | 0 / 25 <sub>hex</sub>                 |

| Or Immediate                        | ori        | I      | R[rt] = R[rs]   ZeroExtImm                                          | (3)       | d <sub>hex</sub>                      |

| Set Less Than                       | slt        | R      | R[rd] = (R[rs] < R[rt]) ? 1 : 0                                     |           | 0 / 2a <sub>hex</sub>                 |

| Set Less Than Imm.                  | slti       | I      | R[rt] = (R[rs] < SignExtImm)<br>? 1 : 0                             | (2)       | a <sub>hex</sub>                      |

| Set Less Than Imm.<br>Unsigned      | sitiu      | I      | R[rt] = (R[rs] < SignExtImm)<br>? 1 : 0 (2)                         | )(6)      | b <sub>hex</sub>                      |

| Set Less Than<br>Unsigned           | sltu       | R      | $R[rd] = (R[rs] \le R[rt]) ? 1 : 0$                                 | (6)       | 0 / 2b <sub>hex</sub>                 |

| Shift Left Logical                  | sll        | R      | $R[rd] = R[rt] \le shamt$                                           |           | 0 / 00 <sub>hex</sub>                 |

| Shift Right Logical                 | srl        | R      | R[rd] = R[rt] >> shamt                                              |           | 0 / 02 <sub>hex</sub>                 |

| Store Byte                          | sb         | I      | M[R[rs]+SignExtImm](7:0) = R[rt](7:0)                               | (2)       | $28_{hex}$                            |

| Store Halfword                      | sh         | I      | M[R[rs]+SignExtImm](15:0) = R[rt](15:0)                             | (2)       | $29_{hex}$                            |

| Store Word                          | SW         | I      | M[R[rs]+SignExtImm] = R[rt]                                         | (2)       | 2b <sub>hex</sub>                     |

| Subtract                            | sub        | R      | R[rd] = R[rs] - R[rt]                                               | (1)       | 0 / 22 <sub>hex</sub>                 |

| Subtract Unsigned                   | subu       | R      | R[rd] = R[rs] - R[rt]                                               |           | 0 / 23 <sub>hex</sub>                 |

| 0 -                                 |            |        | se overflow exception                                               |           |                                       |

|                                     |            |        | mm = { 16{immediate[15]}, imm                                       | edia      | te }                                  |

|                                     |            |        | $mm = \{ 16\{1b'0\}, immediate \}$                                  | adia4     | a 2160 )                              |

|                                     | (5) Jur    | npAdo  | ddr = { 14{immediate[15]}, imme<br>tr = { PC+4[31:28], address, 2'b | al<br>0 } | ., 200 j                              |

|                                     |            |        | s considered unsigned numbers (v                                    |           | s comp.)                              |

| BASIC INSTRUCT                      | ON FC      | RMA    | TS                                                                  |           |                                       |

| R opcode                            | rs         |        | rt rd shamt                                                         | T         | funct                                 |

| 31 26                               |            | 21 20  |                                                                     | 65        | 0                                     |

| I opcode                            | rs         |        | rt immedia                                                          | te        |                                       |

| 31 26                               | 25         | 21 20  |                                                                     |           | 0                                     |

| J opcode<br>31 26                   | 25         |        | address                                                             |           | 0                                     |

|                                     |            |        |                                                                     |           |                                       |

| ARITHMETIC CORE INSTRUCTION SET (2) OPCOD |        |         |                                                                                                 |           |  |  |  |  |  |

|-------------------------------------------|--------|---------|-------------------------------------------------------------------------------------------------|-----------|--|--|--|--|--|

|                                           | MNE-   |         | 0                                                                                               | FMT / FT/ |  |  |  |  |  |

|                                           | MON-   | FOR     |                                                                                                 | FUNCT     |  |  |  |  |  |

| NAME                                      | IC     | MAT     | OPERATION                                                                                       | (Hex)     |  |  |  |  |  |

| Branch On FP True                         | bc1t   | FI      | if(FPcond)PC=PC+4+BranchAddr (4                                                                 | ) 11/8/1/ |  |  |  |  |  |

| Branch On FP Faise                        | bclf   | FI      | if(!FPcond)PC=PC+4+BranchAddr(4                                                                 | ) 11/8/0/ |  |  |  |  |  |

| Divide                                    | div    | R       | Lo=R[rs]/R[rt]; Hi=R[rs]%R[rt]                                                                  | 0///1a    |  |  |  |  |  |

| Divide Unsigned                           | divu   | R.      | Lo=R[rs]/R[rt]; Hi=R[rs]%R[rt] (6                                                               | ) 0///1b  |  |  |  |  |  |

| FP Add Single                             | add.s  | FR      | F[fd] = F[fs] + F[ft]                                                                           | 11/10//0  |  |  |  |  |  |

| FP Add<br>Double                          | add.d  | FR      | ${F[fd],F[fd+1]} = {F[fs],F[fs+1]} + {F[ft],F[ft+1]}$                                           | 11/11//0  |  |  |  |  |  |

| FP Compare Single                         | c.x.s* | FR      | FPcond = (F[fs] op F[ft])?1:0                                                                   | 11/10//y  |  |  |  |  |  |

| FP Compare<br>Double                      | c.x.d* | FR      | $FPcond = ({F[fs], F[fs+1]} op {F[ft], F[ft+1]})? 1:0$                                          | 11/11//y  |  |  |  |  |  |

|                                           |        | op is : | ==, <, or <=) ( y is 32, 3c, or 3e)                                                             |           |  |  |  |  |  |

| FP Divide Single                          | div.s  | FR.     |                                                                                                 | 11/10//3  |  |  |  |  |  |

| FP Divide<br>Double                       | div.d  | FR      | ${F[fd], F[fd+1]} = {F[fs], F[fs+1]} / {F[ft], F[ft+1]}$                                        | 11/11//3  |  |  |  |  |  |

| FP Multiply Single                        | mul.s  | FR      | F[fd] = F[fs] * F[ft]                                                                           | 11/10//2  |  |  |  |  |  |

| FP Multiply<br>Double                     | mul.d  | FR      | ${F[fd],F[fd+1]} = {F[fs],F[fs+1]} * {F[ft],F[ft+1]}$                                           | 11/11//2  |  |  |  |  |  |

| FP Subtract Single                        | sub.s  | FR      | F[fd]=F[fs] - F[ft]                                                                             | 11/10//1  |  |  |  |  |  |

| FP Subtract<br>Double                     | sub.d  | FR      | ${F[fd],F[fd+1]} = {F[fs],F[fs+1]} - {F[ft],F[ft+1]}$                                           | 11/11//1  |  |  |  |  |  |

| Load FP Single                            | lwc1   | 1       | F[rt]=M[R[rs]+SignExtImm] (2                                                                    | ) 31///   |  |  |  |  |  |

| Load FP<br>Double                         | ldcl   | I       | F[rt]=M[R[rs]+SignExtlmm]; (2<br>F[rt+1]=M[R[rs]+SignExtlmm+4]                                  | ) 35//    |  |  |  |  |  |

| Move From Hi                              | mfhi   | R       | R[rd] = Hi                                                                                      | 0 ///10   |  |  |  |  |  |

| Move From Lo                              | mflo   | R       | R[rd] = Lo                                                                                      | 0 ///12   |  |  |  |  |  |

| Move From Control                         | mfc0   | R       | R[rd] = CR[rs]                                                                                  | 10 /0//0  |  |  |  |  |  |

| Multiply                                  | mult   | R       | ${Hi,Lo} = R[rs] * R[rt]$                                                                       | 0///18    |  |  |  |  |  |

| Multiply Unsigned                         | multu  | R       | ${Hi,Lo} = R[rs] * R[rt]$ (6                                                                    | ) 0///19  |  |  |  |  |  |

| Store FP Single                           | swcl   | I       | M[R[rs]+SignExtImm] = F[rt] (2)                                                                 | ) 39///   |  |  |  |  |  |

| Store FP<br>Double                        | sdc1   | I       | $ \begin{split} M[R[rs]+SignExtImm] &= F[rt]; \\ M[R[rs]+SignExtImm+4] &= F[rt+1] \end{split} $ | ) 3d///   |  |  |  |  |  |

#### FLOATING POINT INSTRUCTION FORMATS

| FR | opcode | fmt   | ft    | fs    | fd        | funct |

|----|--------|-------|-------|-------|-----------|-------|

|    | 31 26  | 25 21 | 20 16 | 15 11 | 10 6      | 5 0   |

| Fl | opcode | fmt   | ft    |       | immediate |       |

|    | 31 26  | 25 21 | 20 16 | 15    |           | 0     |

### PSEUDO INSTRUCTION SET

| NAME                         | MNEMONIC | OPERATION                                    |

|------------------------------|----------|----------------------------------------------|

| Branch Less Than             | blt      | if(R[rs] <r[rt]) pc="Label&lt;/td"></r[rt])> |

| Branch Greater Than          |          | if(R[rs]>R[rt]) PC = Label                   |

| Branch Less Than or Equal    | ble      | if(R[rs]<=R[rt]) PC = Label                  |

| Branch Greater Than or Equal | bge      | if(R[rs]>=R[rt]) PC = Label                  |

| Load Immediate               | 1i       | R[rd] = immediate                            |

| Move                         | move     | R[rd] = R[rs]                                |

### REGISTER NAME, NUMBER, USE, CALL CONVENTION

| NAME      | NUMBER | USE                                                      | PRESERVED ACROSS<br>A CALL? |

|-----------|--------|----------------------------------------------------------|-----------------------------|

| \$zero    | 0      | The Constant Value 0                                     | N.A.                        |

| \$at      | 1      | Assembler Temporary                                      | No                          |

| \$v0-\$v1 | 2-3    | Values for Function Results<br>and Expression Evaluation | No                          |

| \$a0-\$a3 | 4-7    | Arguments                                                | No                          |

| \$t0-\$t7 | 8-15   | Temporaries                                              | No                          |

| \$s0-\$s7 | 16-23  | Saved Temporaries                                        | Yes                         |

| \$t8-\$t9 | 24-25  | Temporaries                                              | No                          |

| \$k0-\$k1 | 26-27  | Reserved for OS Kernel                                   | No                          |

| \$gp      | 28     | Global Pointer                                           | Yes                         |

| \$sp      | 29     | Stack Pointer                                            | Yes                         |

| \$fp      | 30     | Frame Pointer                                            | Yes                         |

| Sra       | 31     | Return Address                                           | Yes                         |

Copyright 2007 by Elsevier, Inc., All rights reserved. From Patterson and Hennessy, Computer Organization and Design, 3rd ed. revised

## Midterm Exam – CSE378 Autumn 2009

This is closed book, closed notes, closed calculator and closed neighbor test.

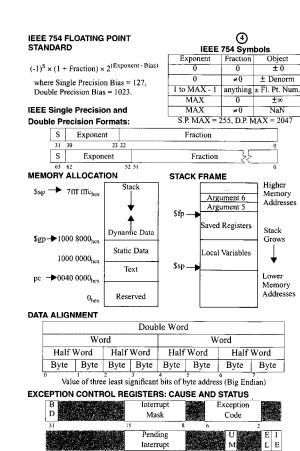

- 2. [2 points] The x in Question1 is what hexadecimal number?

- [2 points] When the x of Question 1 is interpreted as a single precision floating point number, what are the bit values for its sign \_\_\_\_\_, exponent \_\_\_\_\_\_, fraction \_\_\_\_\_\_

- 4. [2 points] What number is the zero for single precision floating point exponents?

- 5. [4 points] Express the 0 of an n-bit bias-represented number as an expression.

- 6. [5 points] Using the "green card", translate the following bit sequence interpreted as MIPS machine code into assembly language be sure to include the correct register names, addresses, immediate values, etc.

0000 0011 1110 0000 0000 0000 0000 1000 \_\_\_\_\_

- 7. [6 points] Register \$t0 contains an arbitrary bit sequence; write three assembly instructions to set the "even bits" to 0 and to keep the odd bits. (Bit 0 is even.)

- 8. [8 points] MIPS hardware does not directly implement the pseudo-instruction: abs \$result, \$source

for storing the absolute value of register **\$source** into register **\$result**. Show the kind of MIPS code the assembler might create for this instruction.

[5 points] If we try the experiment of executing Ib \$t0, 0(\$t1) Ih \$t0, 0(\$t1) Iw \$t0, 0(\$t1)

and discover that only two of the three instructions is legal, what do we know about the value in 1?

10. [25 Points] The following "move to front" C code moves A[n] of an integer array A to A[0], (n < m, the size of the array.)</li>

| t = A[n];                                                                | // Remove A[n]           |

|--------------------------------------------------------------------------|--------------------------|

| for (i=n; 0 <i; i)="" td="" {<=""><td>// Start at hi, go to lo</td></i;> | // Start at hi, go to lo |

| A[i] = A[i-1];                                                           | // Shift item "right"    |

| }                                                                        |                          |

| A[0] = t;                                                                | // Refill A[0]           |

Write this operation in assembly language assuming the base address of A is in a0 and the value of the array index n is in a1. Comment profusely. (Hint: Focus on getting the code correct, rather than finding the most clever solution.)

- 11. [8 points] Suppose the top element on the stack is the integer i in a C function. Show assembly code to push i-- onto the stack.

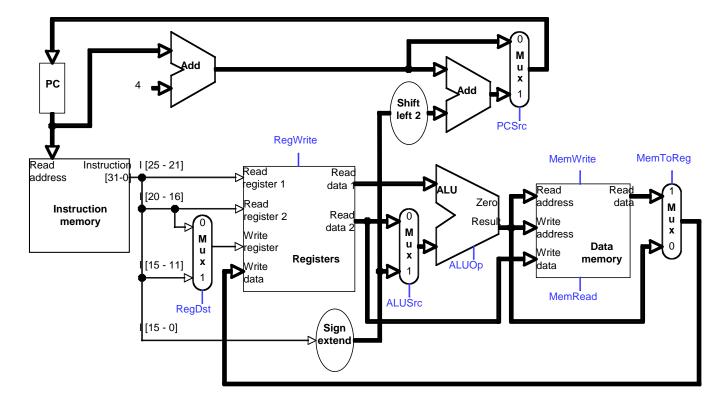

- 12. [5 points] List the opcodes (of the core instruction set, i.e. no pseudos) for all of the instructions that use the "Shift left 2" circuit of the following diagram.

- 13. [8 points] In the diagram above, highlight in color those portions of the circuit that are *active when computing store for the store word instruction*. (Note that other portions will be active in this single cycle implementation; mark *only those portions that contribute to the operation of the instruction*, including control.)

- 14. [5 points] Give the control lines and their settings required to implement the single cycle store instruction above.

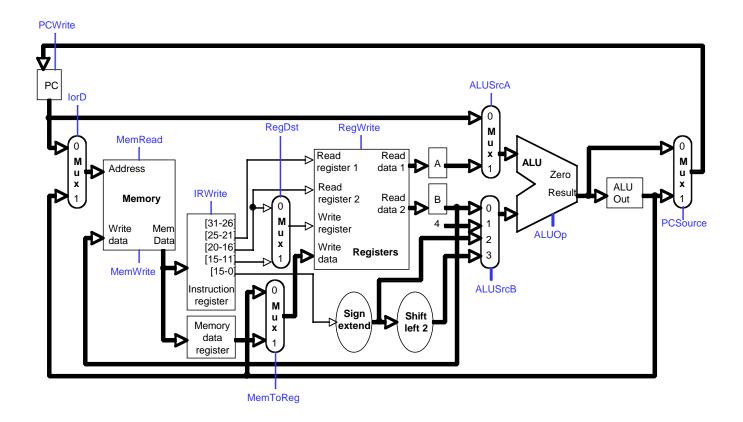

**15**. [8 points] In the accompanying diagram mark in color those portions of the circuit active during the third cycle of a store instruction in this multicycle processor design. (Hint: Think of what you know from cycle 3.)

- 16. [4 points] If ALU operations take 2 ns, register reads/writes take 1ns, and memory operations each take (thanks to a miracle!) 10ns,

- a. How long is the single cycle design's clock cycle?

- b. How long is the multicycle design's clock cycle?

Show your work.

| opcode       | (1) MIPS<br>funct | funct                             | Bina           |            | Deci- |          | ASCII      | Deci-    | Hexa-     | ASC   |

|--------------|-------------------|-----------------------------------|----------------|------------|-------|----------|------------|----------|-----------|-------|

|              |                   |                                   |                |            |       | deci-    | Char-      |          | deci-     | Cha   |

| 31:26)       | (5:0)             | (5:0)                             | Dina           | .,         | mal   | mal      | acter      | mal      | mal       | acte  |

| (1)          | s11               | add./                             | 00 00          | 00         | 0     | 0        | NUL        | 64       | 40        | @     |

| (1)          | 511               | sub.f                             | 00 00          |            | 1     | 1        | SOH        | 65       | 40        | Ă     |

| 4            | * T               |                                   | 00 00          |            | 2     | 2        |            |          | 41        | B     |

| 5            | srl<br>sra        | mul.f                             | 00 00          |            | 23    | 2        | STX<br>ETX | 66<br>67 | 42        | Č     |

| jal          | sllv              | div.f                             | 00 00          |            | 4     | 4        |            | 68       | 43        | - D   |

| beq          | \$11V             | sqrt.f                            |                |            |       |          | EOT        |          |           |       |

| bne          |                   | abs.f                             | 00 01          |            | 5     | 5        | ENQ        | 69       | 45        | E     |

| blez         | srlv              | mov.f                             | 00 01          |            | 6     | 6        | ACK        | 70       | 46        | F     |

| bgtz         | srav              | neg.f                             | 00 01          |            | 7     | 7        | BEL        | 71       | 47        | G     |

| addi         | jr                |                                   | 00 10          |            | 8     | 8        | BS         | 72       | 48        | Ĥ     |

| addiu        | jalr              |                                   | 00 10          |            | 9     | 9        | HT         | 73       | 49        | I     |

| slti         | movz              |                                   | 00 10          |            | 10    | a        | LF         | 74       | 4a        | J     |

| sltiu        | movn              |                                   | 00 10          |            | 11    | b        | VT         | 75       | <u>4b</u> | K     |

| andi         | syscall           | round.w.f                         | 00 11          |            | 12    | с        | FF         | 76       | 4c        | L     |

| ori          | break             | trunc.w.f                         | 00 11          |            | 13    | d        | CR         | 77       | 4d        | М     |

| xori         |                   | ceil.w,f                          | 00 11          |            | 14    | e        | so         | 78       | 4e        | Ν     |

| lui          | sync              | floor.w.f                         | 00 11          | 11         | 15    | f        | SI         | 79       | 4f        | 0     |

|              | mfhi              |                                   | 01 00          |            | 16    | 10       | DLE        | 80       | 50        | P     |

| (2)          | mthi              |                                   | 01 00          |            | 17    | 11       | DC1        | 81       | 51        | Q     |

|              | mflo              | movz <i>.f</i>                    | 01 00          |            | 18    | 12       | DC2        | 82       | 52        | R     |

|              | mtlo              | movn <i>f</i>                     | 01 00          | 11         | 19    | 13       | DC3        | 83       | 53        | S     |

|              |                   |                                   | 01 01          | 00         | 20    | 14       | DC4        | 84       | 54        | Т     |

|              |                   |                                   | 01 01          |            | 21    | 15       | NAK        | 85       | 55        | U     |

|              |                   |                                   | 01 01          | 10         | 22    | 16       | SYN        | 86       | 56        | V     |

|              |                   |                                   | 01 01          |            | 23    | 17       | ETB        | 87       | 57        | Ŵ     |

|              | mult              |                                   | 01 10          |            | 24    | 18       | CAN        | 88       | 58        | X     |

|              | multu             |                                   | 01 10          |            | 25    | 19       | EM         | 89       | 59        | Ŷ     |

|              | dív               |                                   | 01 10          |            | 26    | la       | SUB        | 90       | 5a        | ż     |

|              | divu              |                                   | 01 10          |            | 27    | 16       | ESC        | 91       | 5b        | . Ĩ   |

|              |                   |                                   | 01 11          |            | 28    | 10       | FS         | 92       | 5c        | - 1   |

|              |                   |                                   | 01 11          |            | 29    | 1d       | GS         | 93       | 5d        | ì     |

|              |                   |                                   | 01 11          |            | 30    |          | RS         | 94       | 5e        | ž     |

|              |                   |                                   | 01 11          |            | 31    | le<br>lf | US         | 95       | 5f        |       |

| ь            | add               |                                   | 10 00          |            | 32    | 20       |            | 95       | 60        |       |

| lh           |                   | cvt.s.f                           | 10 00          |            | 33    | 20       | Space      | 97       | 61        |       |

| lwl          | addu<br>sub       | cvt.d.f                           |                |            | 34    | 22       | !          | 98       |           | a     |

|              |                   |                                   | 10 00          |            |       |          |            |          | 62        | b     |

| lw           | subu              |                                   | 10 00          |            | 35    | 23       | #          | 99       | 63        | c     |

| lbu          | and               | cvt.w <i>f</i>                    | 10 01          |            | 36    | 24       | \$         | 100      | 64        | d     |

| lhu          | or                |                                   | 10 01          |            | 37    | 25       | %          | 101      | 65        | e     |

| lwr          | xor               |                                   | 10 01          |            | 38    | 26       | &          | 102      | 66        | f     |

|              | nor               |                                   | 10.01          |            | 39    | 27       |            | 103      | 67        | g     |

| sb           |                   |                                   | 10 10          |            | 40    | 28       | (          | 104      | 68        | h     |

| sh           |                   |                                   | 10 10          |            | 41    | 29       | )<br>*     | 105      | 69        | i     |

| swl          | slt               |                                   | 10 10          |            | 42    | 2a       |            | 106      | 6a        | j     |

| sw           | sltu              |                                   | 10 10          | 11         | 43    | 2b       | +          | 107      | 6b        | k     |

|              |                   |                                   | 1011           | 00         | 44    | 2c       | ,          | 108      | 6c        | 1     |

|              |                   |                                   | 10 11          | 01         | 45    | 2d       | -          | 109      | 6d        | m     |

| swr          |                   |                                   | 1011           |            | 46    | 2e       |            | 110      | 6e        | n     |

| cache        |                   |                                   | 10 11          |            | 47    | 2f       | 1          | 111      | 6f        | 0     |

| 11           | tge               | c.f.f                             | 11 00          |            | 48    | 30       | 0          | 112      | 70        | p     |

| lwc1         | tgeu              | c.un.f                            | 11 00          |            | 49    | 31       | ĩ          | 113      | 71        | q     |

| lwc2         | tlt               | c.eq.f                            | 11 00          |            | 50    | 32       | 2          | 114      | 72        | r     |

| pref         | tltu              | c.ueq.f                           | 11 00          |            | 51    | 33       | 3          | 115      | 73        | s     |

|              | teq               | c.olt.f                           | 11 00          |            | 52    | 34       | 4          | 116      | 74        | <br>t |

| ldc1         | cey               |                                   | 11 01          |            | 53    | 35       | 5          | 117      | 75        | u u   |

| ldc2         | the               | c.ult.f                           |                |            | 54    | 36       | 6          | 118      | 76        |       |

| Lac2         | tne               | c.ole.f                           | 11 01          |            |       |          |            |          |           | v     |

|              |                   | c.ule.f                           | 11 01          |            | 55    | 37       | 7          | 119      | 77        | w     |

| 5C .         |                   | c.sf.f                            | 11 10          |            | 56    | 38       | 8          | 120      | 78        | х     |

| swc1         |                   | c.ngle.f                          | 11 10          |            | 57    | 39       | 9          | 121      | 79        | У     |

| swc2         |                   | c.seq.f                           | 11 10          |            | 58    | 3a       | :          | 122      | 7a        | Z     |

|              |                   | c.ngl <i>.f</i>                   | 11 10          |            | 59    | 3b       | ;          | 123      | 7Ъ        | {     |

|              |                   | c.lt.f                            | 11 11          | 00         | 60    | 3c       | <          | 124      | 7c        | - T   |

|              |                   |                                   |                |            | 61    | 3d       | =          | 125      | 7d        | j     |

| sdc1         |                   | c.nge./                           | 11 11          | <b>U</b> 1 |       |          |            |          |           |       |

| sdel<br>sdc2 |                   | c.nge <i>.f</i><br>c.le <i>.f</i> | 11 11<br>11 11 |            | 62    | 3e       | >          | 126      | 7e        | ~     |

LE BD = Branch Delay, UM = User Mode, EL = Exception Level, IE =Interrupt Enable EXCEPTION CODES

| EXCEP  |      |                             |                            |      |                          |

|--------|------|-----------------------------|----------------------------|------|--------------------------|

| Number | Name |                             | Number                     | Name |                          |

| 0      | Int  | Interrupt (hardware)        | 9                          | Bp   | Breakpoint Exception     |

| 4      | AdEL |                             | Address Error Exception 10 |      | Reserved Instruction     |

| 1 7    | Auee | (load or instruction fetch) | 10                         | RI   | Exception                |

| 5      | AdES | Address Error Excep-        | 11                         | CpU  | Coprocessor              |

|        | Aubo | tion (store)                | 11                         | CpO  | Unimplemented            |

| 6      | IBE  | Bus Error on                | 12                         | Ov   | Arithmetic Overflow      |

| 0      | IDE  | Instruction Fetch           | 12                         | 00   | Exception                |

| 7      | DBE  | Bus Error on                |                            | Tr   | Trop                     |

| '      |      | Load or Store               | 13                         |      | Trap                     |

| 8      | Sys  | Syscall Exception           | 15                         | FPE  | Floating Point Exception |

SIZE PREFIXES (10<sup>x</sup> for Disk, Communication; 2<sup>x</sup> for Memory)

|   |                                    | PRE-     |                                    | PRE-         |                   | PRE-     |                   | PRE-      |

|---|------------------------------------|----------|------------------------------------|--------------|-------------------|----------|-------------------|-----------|

|   | SIZE                               | FIX      | SIZE                               | FIX          | SIZE              | FIX      | SIZE              | FIX       |

|   | 10 <sup>3</sup> , 2 <sup>10</sup>  | Kilo-    | 10 <sup>15</sup> , 2 <sup>50</sup> | Peta-        | 10-3              | milli-   | 10-15             | femto-    |

|   | 10 <sup>6</sup> , 2 <sup>20</sup>  | Mega-    | 10 <sup>18</sup> , 2 <sup>60</sup> | Exa-         | 10-6              | micro-   | 10-18             | atto-     |

|   | 10 <sup>9</sup> , 2 <sup>30</sup>  | Giga-    | $10^{21}, 2^{70}$                  | Zetta-       | 10-9              | nano-    | 10-21             | zepto-    |

|   | 10 <sup>12</sup> , 2 <sup>40</sup> | Tera-    | $10^{24}, 2^{80}$                  | Yotta-       | 10 <sup>-12</sup> | pico-    | 10 <sup>-24</sup> | yocto-    |

| Т | he symbol                          | for each | prefix is ju                       | st its first | letter, e         | except µ | is used           | for micro |

(2) opcode(31:26) ==  $17_{\text{ten}} (11_{\text{hex}})$ ; if fmt(25:21)== $16_{\text{ten}} (10_{\text{hex}}) f = s$  (single); if fmt(25:21)= $17_{ten}(11_{hex})f = d$  (double)

Copyright 2007 by Elsevier, Inc., All rights reserved. From Patterson and Hennessy, Computer Organization and Design, 3rd ed. revised