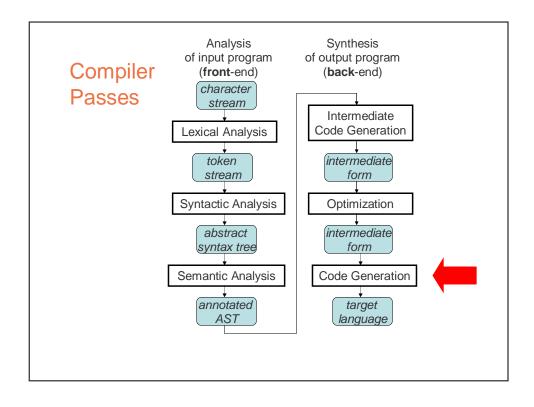

### **Target Code Generation**

Input: intermediate language (IL)

Output: target language program

Target languages:

- absolute binary (machine) code

- relocatable binary code

- assembly code

– C

Target code generation must bridge the gap

# The gap, if target is machine code

| IL                                                                       | Machine Code                                                                                                       |

|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| global variables                                                         | global static memory                                                                                               |

| unbounded number of<br>interchangeable local<br>variables                | fixed number of registers, of various<br>incompatible kinds, plus unbounded number<br>of stack locations           |

| built-in parameter passing & result returning                            | calling conventions defining where arguments & results are stored and which registers may be overwritten by callee |

| statements                                                               | machine instructions                                                                                               |

| statements can have<br>arbitrary subexpression<br>trees                  | instructions have restricted operand addressing                                                                    |

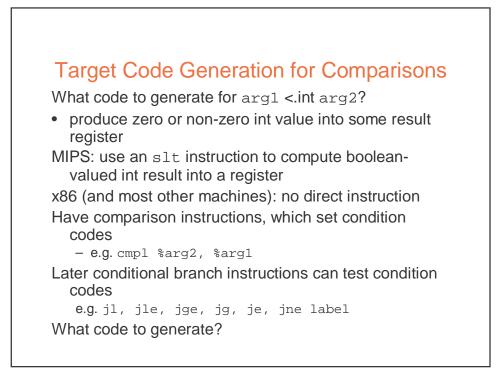

| conditional branches based<br>on integers representing<br>Boolean values | conditional branches based on condition codes (maybe)                                                              |

### Tasks of Code Generator

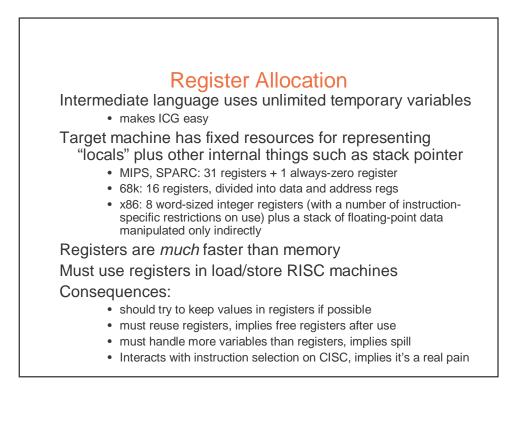

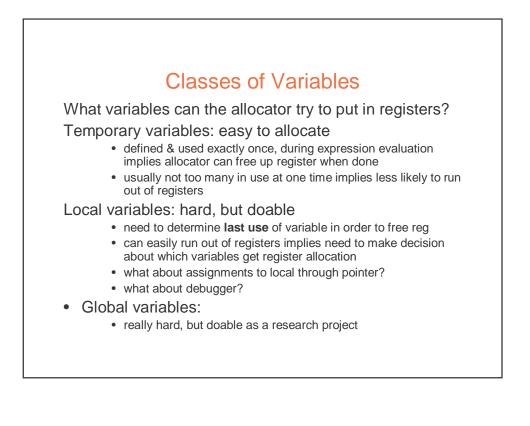

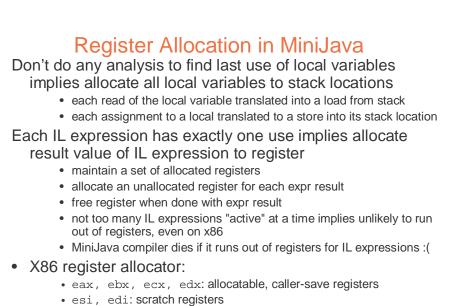

#### **Register allocation**

- for each IL variable, select register/stack location/global memory location(s) to hold it

- can depend on type of data, which operations manipulate it

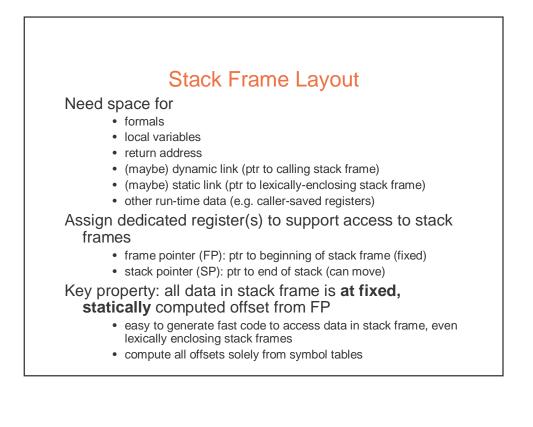

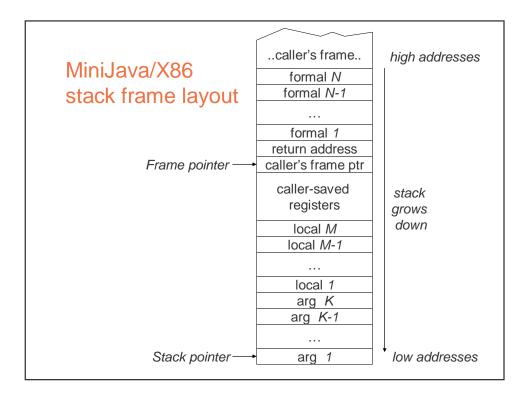

- Stack frame layout

- compute layout of each function's stack frame

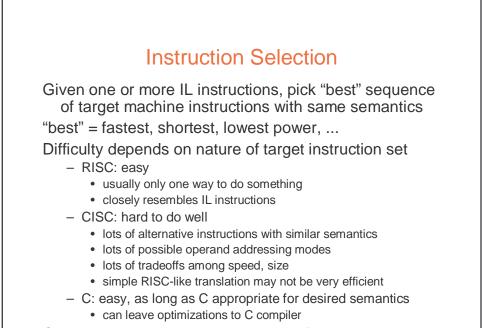

- Instruction selection

- for each IL instruction (sequence), select target language instruction (sequence)

- includes operand addressing mode selection

- Can have complex interactions

- instruction selection depends on where operands are allocated

- some IL variables may not need a register, depending on the instructions & addressing modes that are selected

### **Classes of Registers**

What registers can the allocator use?

Fixed/dedicated registers

- stack pointer, frame pointer, return address, ...

- claimed by machine architecture, calling convention, or internal convention for special purpose

- not easily available for storing locals

- Scratch registers

- couple of registers kept around for temp values e.g. loading a spilled value from memory in order to operate on it

- Allocatable registers

- remaining registers free for register allocator to exploit

- Some registers may be overwritten by called procedures implies caller must save them across calls, if allocated

- · caller-saved registers vs. callee-saved registers

- esp: stack pointer; ebp: frame pointer

- floating-point stack, for double values

| <ul> <li>starts running callee's code</li> <li>Stack pointer arg 1</li> </ul> |

|-------------------------------------------------------------------------------|

|-------------------------------------------------------------------------------|

Correctness a big issue, particularly if codegen complex

| Example                                                       |  |

|---------------------------------------------------------------|--|

| IL code:<br>t3 = t1 + t2;<br>Target code (MIPS):              |  |

| add \$3,\$1,\$2<br>Target code (SPARC):                       |  |

| add %1,%2,%3<br>Target code (68k):                            |  |

| mov.l d1,d3<br>add.l d2,d3                                    |  |

| Target code (x86):<br>movl %eax,%ecx<br>addl %ebx,%ecx        |  |

| 1 IL instruction may expand to several target<br>instructions |  |

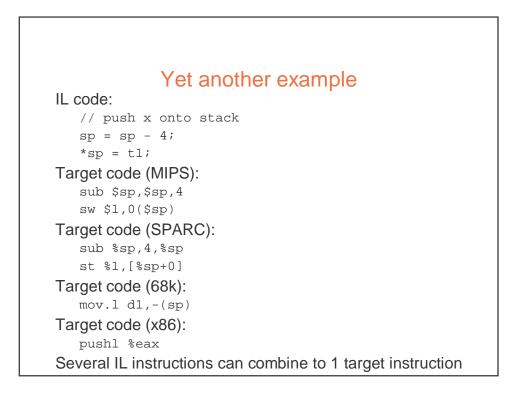

# Another Example

```

IL code:

t1 = t1 + 1;

Target code (MIPS):

add $1,$1,1

Target code (SPARC):

add $1,1,$1

Target code (68k):

add.1 #1,d1...or...

inc.1 d1

Target code (x86):

addl $1,$eax ...or...

incl $eax

Can have choices

```

• it's a pain to have choices; requires making decisions

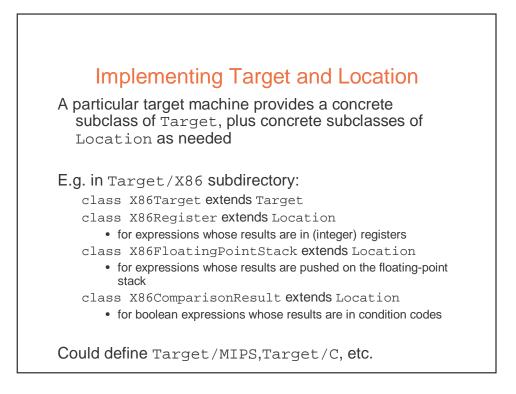

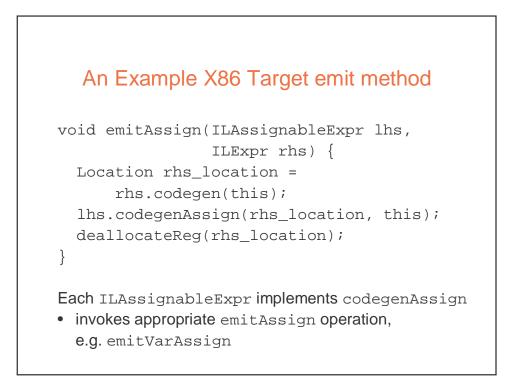

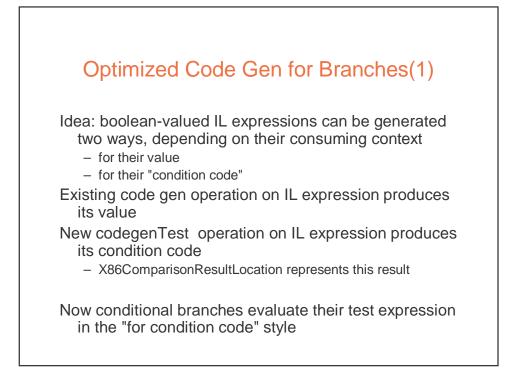

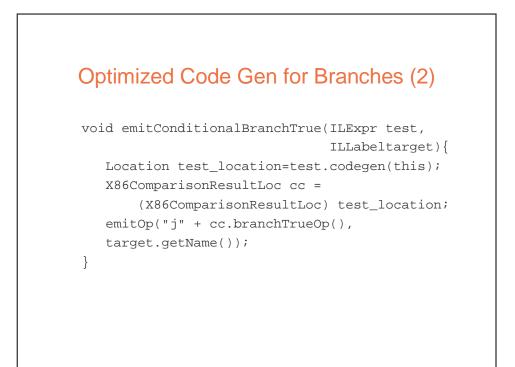

#### Instruction Selection in MiniJava Expand each IL statement into some number of target machine instructions don't attempt to combine IL statements together In Target subdirectory: abstract class Target abstract class Location · defines abstract methods for emitting machine code for statements, e.g. emitVarAssign, emitFieldAssign, emitBranchTrue · defines abstract methods for emitting machine code for statements, e.g. emitVarRead, emitFieldRead, emitIntMul • return Location representing where result is allocated IL statement and expression classes invoke these operations to generate their machine code • each IL stmt, expr has a corresponding emit operation on the Target class Details of target machines are hidden from IL and the rest of the compiler behind the Target and Location interfaces

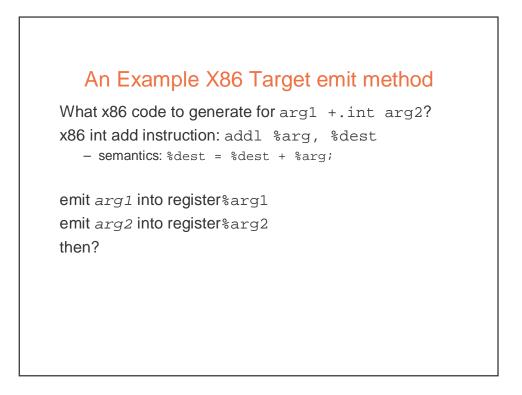

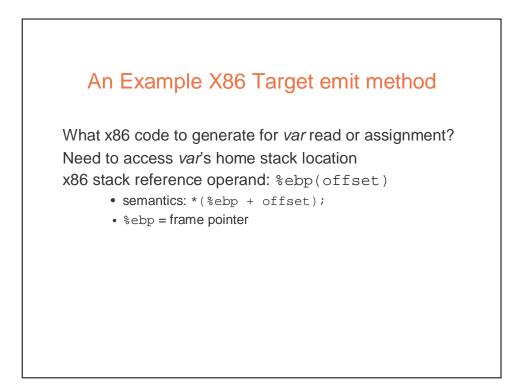

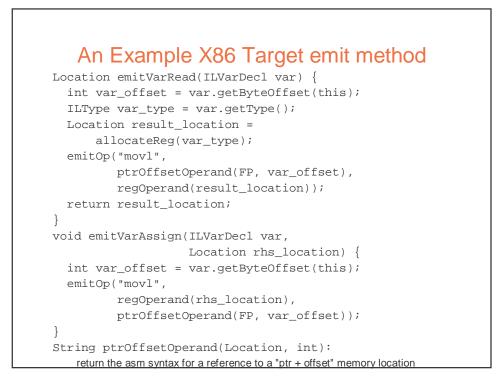

### An Example X86 emit method

```

Location emitIntConstant(int value) {

Location result location =

allocateReg(ILType.intILType());

emitOp("movl",

intOperand(value),

regOperand(result_location));

return result_location;

}

Location allocateReg(ILType):

allocate a new register to hold a value of the given type

void emitOp(String opname, String arg1, ...):

emit assembly code

String intOperand(int):

return the asm syntax for an int constant operand

String regOperand(Location):

return the asm syntax for a reference to a register

```

```

Location emit IntAdd(ILExprarg1,ILExprarg2) {

Location arg1_location=arg1.codegen(this);

Location arg2_location=arg2.codegen(this);

emitOp("addl",

regOperand(arg2_location),

regOperand(arg1_location));

deallocateReg(arg2_location);

return arg1_location;

}

void deallocateReg(Location):

deallocate register,

make available for use by later instructions

```

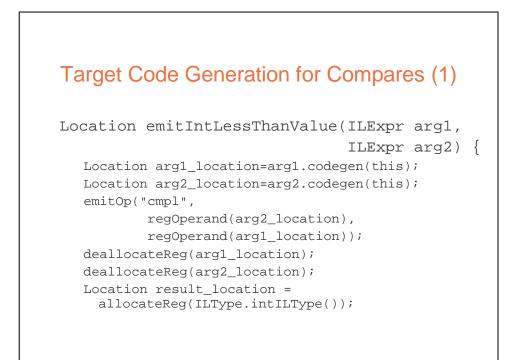

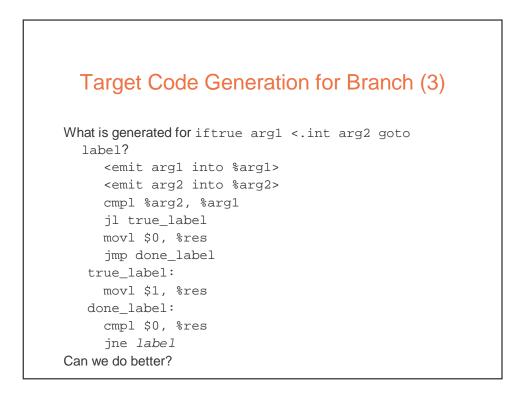

```

String true_label = getNewLabel();

emitOp("jl", true_label);

emitOp("movl", intOperand(0),

regOperand(result_location));

String done_label = getNewLabel();

emitOp("jmp", done_label);

emitLabel(true_label);

emitOp("movl", intOperand(1),

regOperand(result_location));

emitLabel(done_label);

return result_location;

```

}

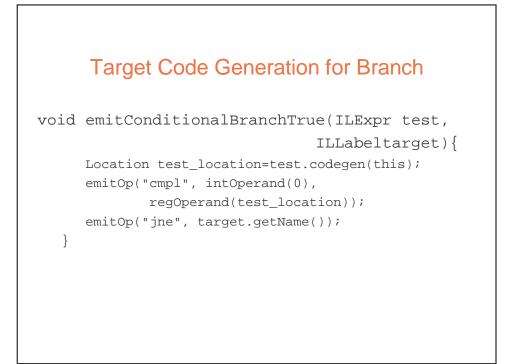

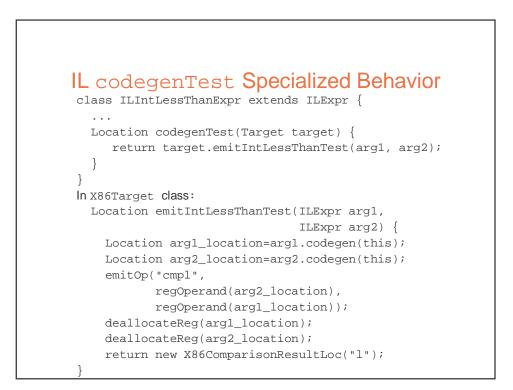

### IL codegenTest Default Behavior

```

class ILExpr extends ILExpr {

...

Location codegenTest(Target target) {

return target.emitTest(this);

}

}

In X86Target class:

Location emitTest(ILExpr arg) {

Location arg_location = arg.codegen(this);

emitOp("cmpl", intOperand(0),

regOperand(arg_location));

deallocateReg(arg_location);

return new X86ComparisonResultLoc("ne");

}

```

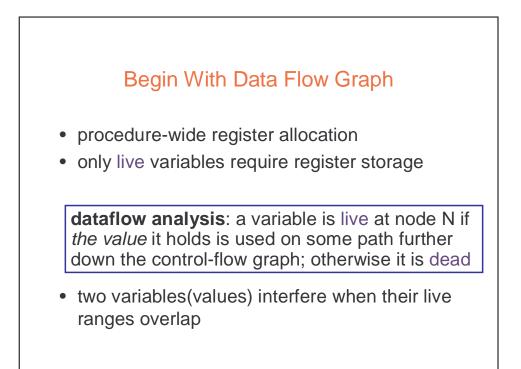

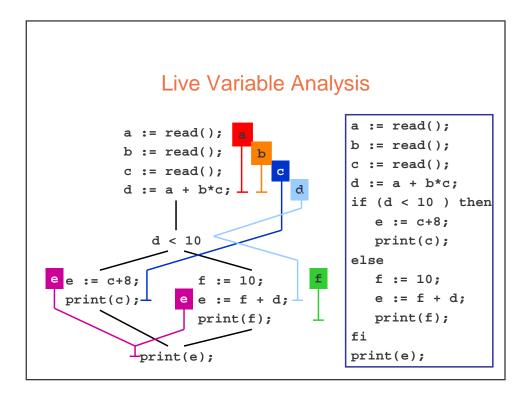

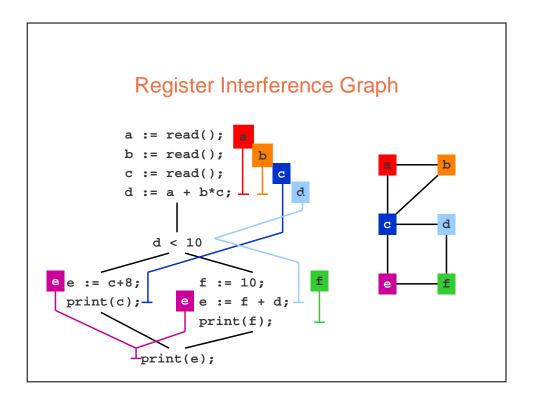

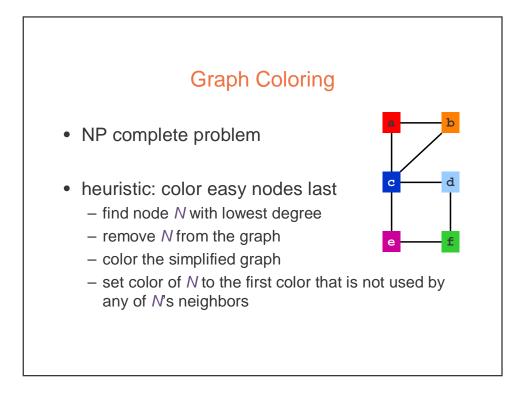

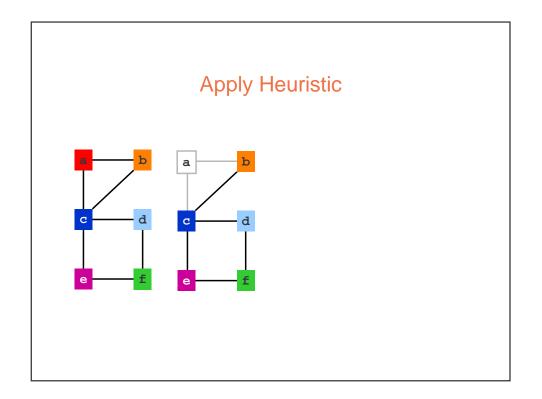

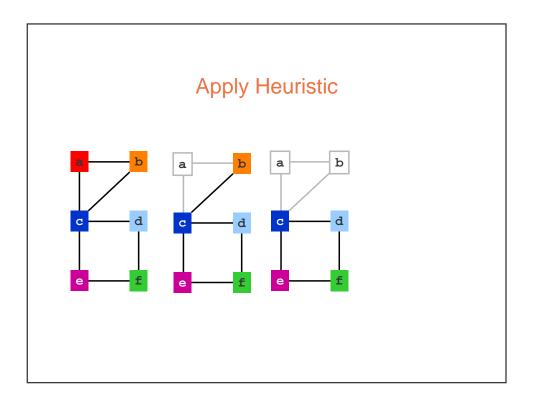

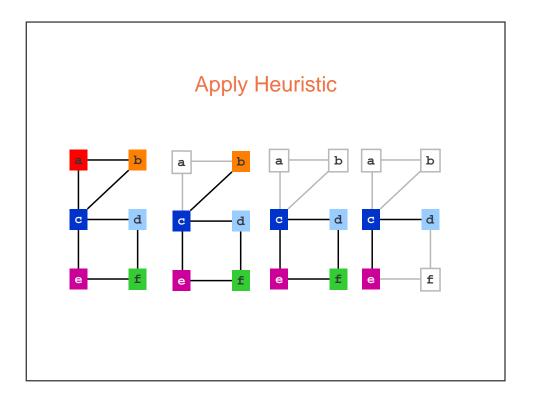

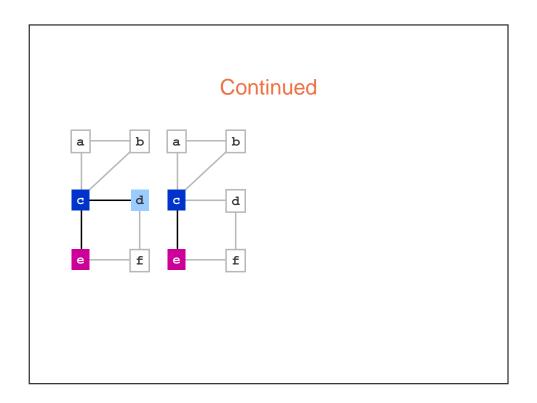

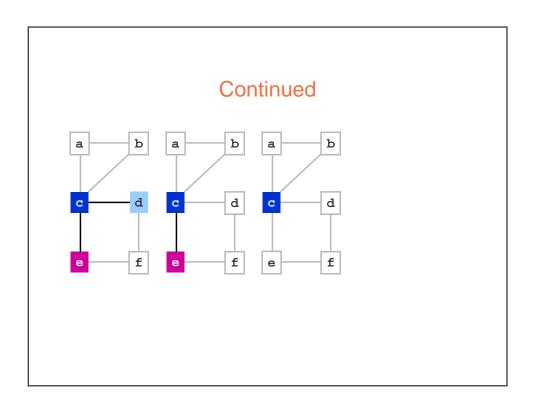

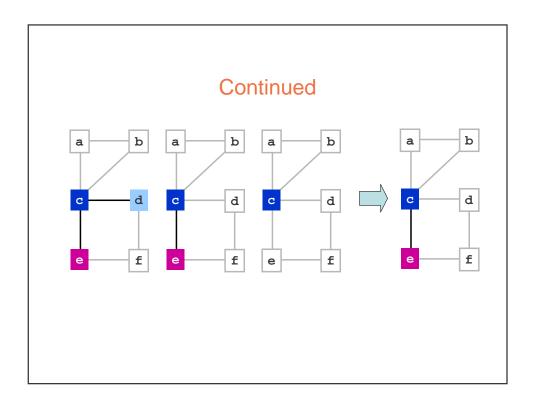

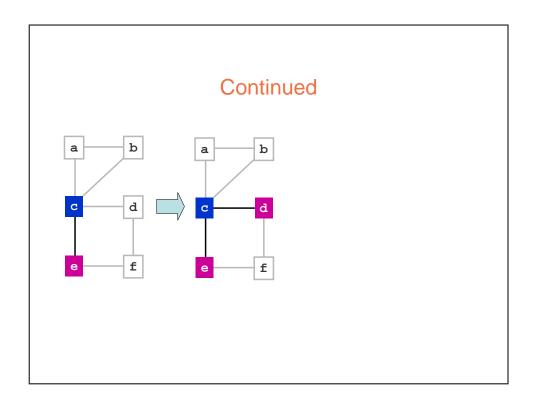

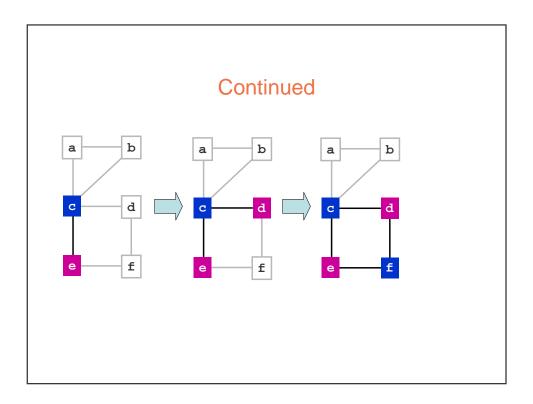

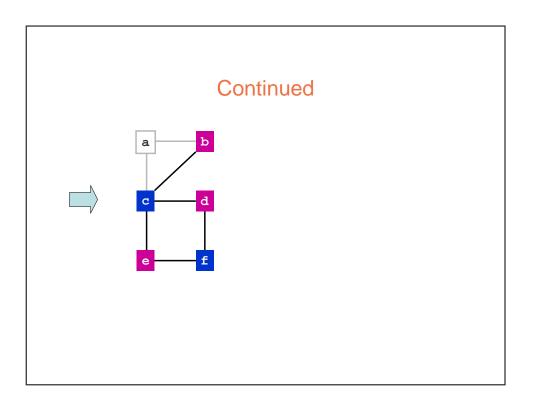

# **Register Allocation -- A Cool Algorithm**

- How to convert the infinite sequence of temporary data references, t1, t2, ... into finite assignment register numbers \$8, \$9, ..., \$25

- Goal: Use available registers with minimum spilling

- Problem: Minimizing the number of registers is NP-complete ... it is equivalent to chromatic number--minimum colors to color nodes of graph so no edge connects same color

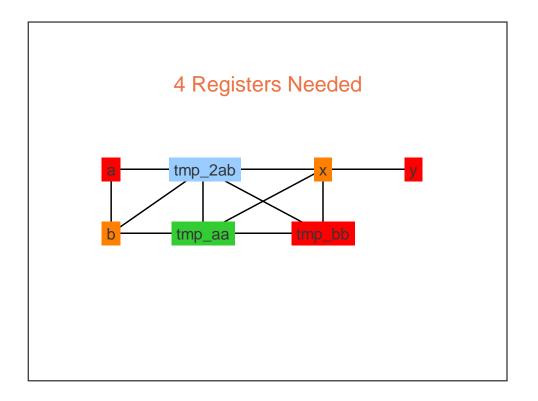

# Example

```

{ int tmp_2ab = 2*a*b;

int tmp_aa = a*a;

int tmp_bb = b*b;

x := tmp_aa + tmp_2ab + tmp_bb;

y := tmp_aa - tmp_2ab + tmp_bb;

}

```

given that a and b are live on entry and dead on exit, and that x and y are live on exit:

- (a) construct the register interference graph

- (b) color the graph; how many registers are needed?

# **Code Generation Summary**

- Code generation is

- Machine specific

- Error prone

- Least "elegant" of the compilation process

- Code generation is

- Place where key transformation takes place in the compiler

- Most visible impact on performance