# **Computer Instructions**

#### CSE 410, Spring 2004 **Computer Systems**

http://www.cs.washington.edu/education/courses/410/04sp/

#### **Reading and References**

- Readings

- » Chapter 3.1-3.4, Computer Organization and Design, Patterson and Hennessy

- Other References

- » See MIPS Run, D Sweetman

- section 8.5, Instruction encoding

- section 11.6, Endianness

| 31-Mar-2004 | cse410-02-instructions © 2004 University of Washington | 1 | 31-Mar-2004 | cse410-02-instructions © 2004 University of Washington | 2 |

|-------------|--------------------------------------------------------|---|-------------|--------------------------------------------------------|---|

|             |                                                        |   |             |                                                        |   |

|             |                                                        |   |             |                                                        |   |

|             |                                                        |   |             |                                                        |   |

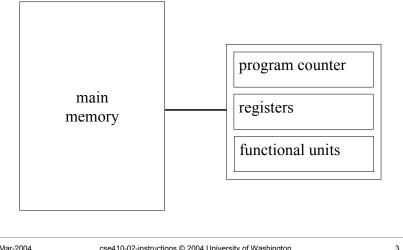

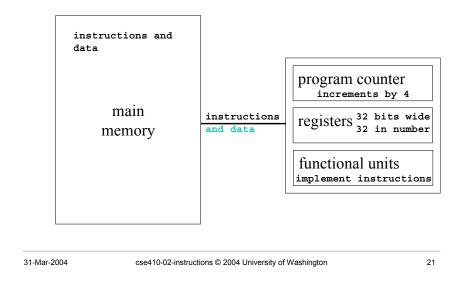

## A very simple organization

cse410-02-instructions © 2004 University of Washington

#### Instructions in main memory

- Instructions are stored in main memory » each byte in memory has a number (an address)

- Program counter (PC) points to the next instruction

- » All MIPS instructions are 4 bytes long, and so instruction addresses are always multiples of 4

- Program addresses are 32 bits long  $2^{32} = 4,294,967,296 = 4$  GigaBytes (GB)

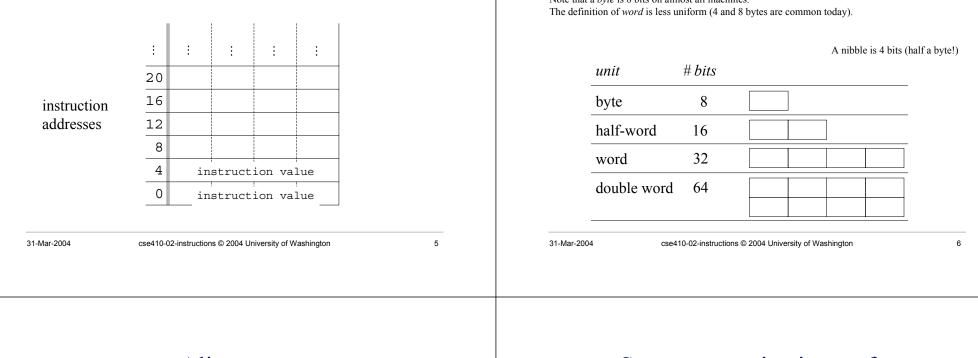

#### Instructions in memory

#### Alignment

- An object in memory is "aligned" when its address is a multiple of its size

- Byte: always aligned

- Halfword: address is multiple of 2

- Word: address is multiple of 4

- Double word: address is multiple of 8

- Alignment simplifies load/store hardware

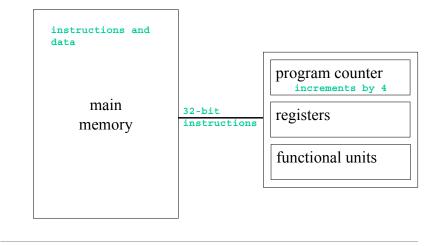

#### System organization so far

31-Mar-2004

7

#### Some common storage units

Note that a byte is 8 bits on almost all machines.

#### **MIPS** Registers

- 32 bits wide

- » 32 bits is 4 bytes

- » same as a word in memory

- » signed values from  $-2^{31}$  to  $+2^{31}-1$

- » unsigned values from 0 to  $2^{32}$ -1

- easy to access and manipulate

- » 32 registers (not related to being 32 bits wide)

cse410-02-instructions © 2004 University of Washington

» on chip, so very fast to access

#### Register addresses

- 32 general purpose registers

- how many bits does it take to identify a register?

- » 5 bits, because  $2^5 = 32$

- 32 registers is a compromise selection

- » more would require more bits to identify

- » fewer would be harder to use efficiently

9

#### Register numbers and names

| number                    | name     | usage                                            |  |

|---------------------------|----------|--------------------------------------------------|--|

| 0 zero                    |          | always returns 0                                 |  |

| 1at                       |          | reserved for use as assembler temporary          |  |

| 2-3 <b>v0, v1</b>         |          | values returned by procedures                    |  |

| 4 - 7                     | a0-a3    | first few procedure arguments                    |  |

| 8-15, 24, 25 <b>t0-t9</b> |          | temps - can use without saving                   |  |

| 16-23 <b>s0-s7</b>        |          | temps - must save before using                   |  |

| 26,27 k0, k1              |          | reserved for kernel use - may change at any time |  |

| 28                        | gp       | global pointer                                   |  |

| 29                        | sp       | stack pointer                                    |  |

| 30                        | fp or s8 | frame pointer                                    |  |

| 31 <b>ra</b>              |          | return address from procedure                    |  |

|                           |          |                                                  |  |

#### How are registers used?

cse410-02-instructions © 2004 University of Washington

- Many instructions use 3 registers

- » 2 source registers

- » 1 destination register

- For example

- » add \$t1, \$a0, \$t0

- add a0 and t0 and put result in t1

- » add \$t1,\$zero,\$a0

- move contents of a0 to t1 (t1 = 0 + a0)

31-Mar-2004

31-Mar-2004

#### R-format instructions: 3 registers **R**-format fields • 32 bits available in the instruction op code source 1 source 2 dest shamt function • 15 bits for the three 5-bit register numbers 6 bits 5 bits 5 bits 5 bits 5 bits 6 bits • The remaining 17 bits are available for some common R-format instructions specifying the instruction » arithmetic: add, sub, mult, div » 6-bit op code - basic instruction identifier » logical: and, or, sll, srl » 5-bit shift amount » comparison: slt (set on less than) » 6-bit function code » jump through register: jr 31-Mar-2004 13 31-Mar-2004 cse410-02-instructions © 2004 University of Washington cse410-02-instructions © 2004 University of Washington 14

## Bits are just bits

- The bits mean whatever the designer says they mean when the ISA is defined

- How many possible 3-register instructions are there?

- » 2<sup>17</sup> = 131,072

- » includes all values of op code, shamt, function

- As the ISA develops over the years, the encoding tends to become less logical

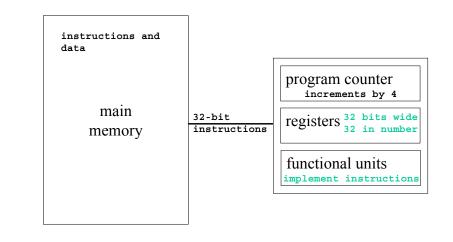

## System organization again

#### Transfer from memory to register

• Load instructions

| ≫ | word:      | lw  | rt, | address |

|---|------------|-----|-----|---------|

| ≫ | half word: | lh  | rt, | address |

|   |            | lhu | rt, | address |

| » | byte:      | lb  | rt, | address |

|   |            | lbu | rt, | address |

- signed load => sign bit is extended into the upper bits of destination register

- unsigned load  $\Rightarrow 0$  in upper bits of register

cse410-02-instructions © 2004 University of Washington

#### Transfer from register to memory

• Store instructions » word: rt, address sw » half word: sh rt, address » byte: rt, address sb 31-Mar-2004 cse410-02-instructions © 2004 University of Washington 18 **I**-format fields

#### The "address" term

- There is one basic addressing mode: offset + base register value

- Offset is 16 bits (± 32 KB)

- Load word pointed to by s0, add t1, store

- \$t0,0(\$s0) lw

- add \$t0,\$t0,\$t1

- \$t0,0(\$s0) sw

| op code | base reg | <pre>src/dest</pre> | offset or immediate value |

|---------|----------|---------------------|---------------------------|

| 6 bits  | 5 bits   | 5 bits              | 16 bits                   |

- The contents of the base register and the offset value are added together to generate the address for the memory reference

- Can also use the 16 bits to specify an immediate value, rather than an address

31-Mar-2004

19

#### Instructions and Data flow

#### The eye of the beholder

- Bit patterns have no inherent meaning

- A 32-bit word can be seen as

- » a signed integer ( $\pm 2$  Billion)

- » an unsigned integer or address pointer (0 to 4B)

- » a single precision floating point number

- » four 1-byte characters

- » an instruction

- 31-Mar-2004 cse410-02-instructions © 2004 University of Washington

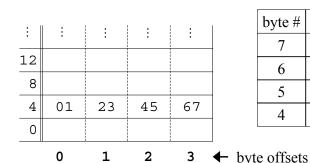

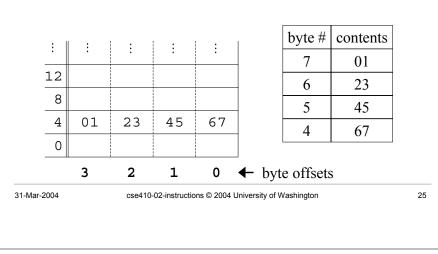

#### Big-endian, little-endian

- A 32-bit word in memory is 4 bytes long

- but which byte is which address?

- Consider the 32-bit number 0x01234567

- » four bytes: 01, 23, 45, 67

- » most significant bits are 0x01

- » least significant bits are 0x67

#### Data in memory- big endian

#### Big endian - most significant bits are in byte 0 of the word

| contents |

|----------|

| 67       |

| 45       |

| 23       |

| 01       |

|          |

23

#### Data in memory- little endian

Little endian - least significant bits are in byte 0 of the word