|                                                                                                                                      | Reading and References                                                                                                                 |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Input / Output                                                                                                                       | <ul> <li>Reading         <ul> <li>Section 8.1-8.5, Computer Organization and Design,<br/>Patterson and Hennessy</li> </ul> </li> </ul> |  |  |  |

| CSE 410, Spring 2004<br>Computer Systems                                                                                             |                                                                                                                                        |  |  |  |

| http://www.cs.washington.edu/education/courses/410/04sp/                                                                             |                                                                                                                                        |  |  |  |

| pr-2004 cse410-15-input-output © 2004 University of Washington 1                                                                     | 30-Apr-2004 cse410-15-input-output © 2004 University of Washington 2                                                                   |  |  |  |

|                                                                                                                                      |                                                                                                                                        |  |  |  |

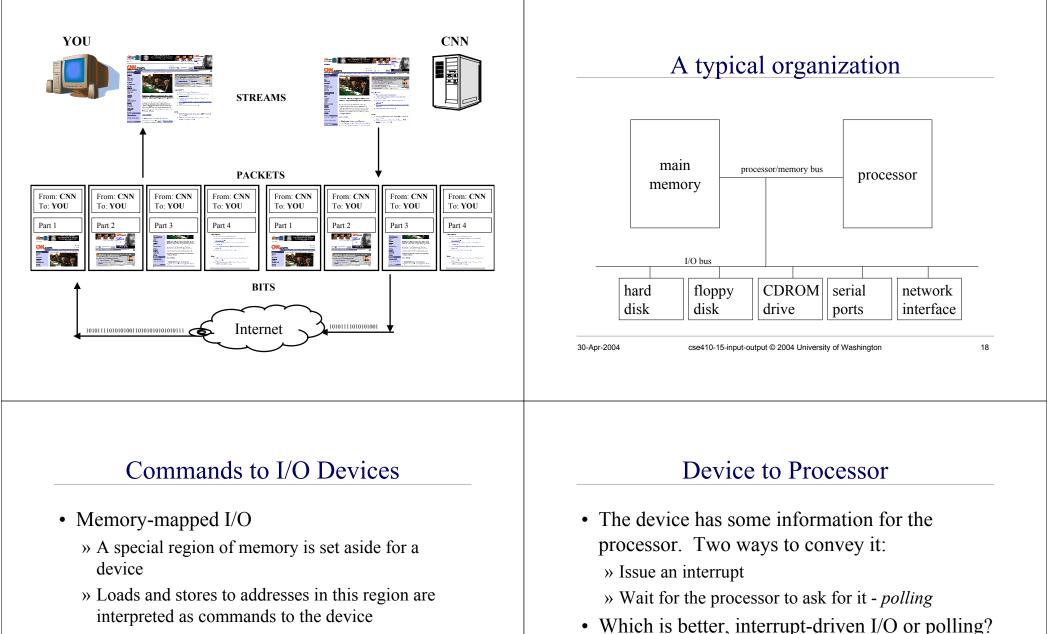

| Why Input and Output?                                                                                                                | A typical organization                                                                                                                 |  |  |  |

| Why Input and Output?<br>Everything we have done so far is based on<br>moving data / instructions between main<br>memory and the CPU | main processor/memory bus                                                                                                              |  |  |  |

| Everything we have done so far is based on<br>moving data / instructions between main                                                |                                                                                                                                        |  |  |  |

## Types of I/O devices

• Behavior

» input only (keyboard, mouse, sensor) » output only (monitor, LED display, actuator) » input and output (network, disk, tape, CD-RW)

• Partner

» human or machine

• Data rate

30-Apr-2004

» negligible to KiloBytes/Second to MegaBytes/S

cse410-15-input-output © 2004 University of Washington

#### Three Characteristic Devices

• Mouse

» input only; human; .01-.02 KB/s

- Magnetic disks » input and output; machine; 100-10,000 KB/s

- Networks

30-Apr-2004

» input and output; machine; 500-6000 KB/s

#### **Detecting Mouse Motion**

- Mechanical

- » Two perpendicular wheels on the inside connected to potentiometers

- Optical

- » LED and a photodetector on the bottom

- Optomechanical

- » The wheels have slots; an LED shines through them

- Lots of others

- » embedded microprocessor in the mouse

#### **Mouse Interfaces**

cse410-15-input-output © 2004 University of Washington

- Pointing device must provide

- » Status of each button

- » Position in X and Y

- Software must interpret the interface input

- » Double clicks

- » Limits to motion, speed

7

5

6

Screen

position

position

information

position

measurement

Device

driver

Mouse

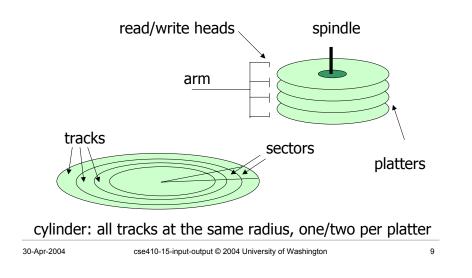

#### Anatomy of a Magnetic Disk

#### Accessing Data from a Disk

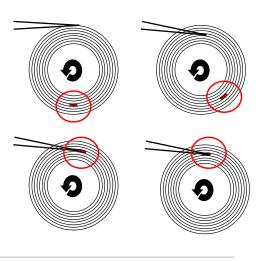

- First, the disk arm moves over the right cylinder: *seek time*

- Next, wait for the data to rotate under the disk arm: *rotational delay*, (on average half the time for one revolution)

- Finally, read the data from the disk: *transfer time*

- At this point, the data is in the *disk controller* and can be transferred to memory

30-Apr-2004

cse410-15-input-output © 2004 University of Washington

10

## Disk Interface

Only two data transfer operations on a disk:

» read block, write block

• Unknown to the disk:

Hidden behind the interface:

» block ↔ sector mappings

» contents of the blocks/sectors

File system interface Blocks Disk interface Sectors

- Disk Specifications

- Consider the disk in my (old) laptop

» 5GB IBM DJSA-205 (from device manager)

- Specifications (from IBM data sheet) » rotation speed 4200 RPM

- rotational delay = 60 \* 1/4200 \* 0.5 = 7.1 ms

- » seek times

- avg: 12.0 ms, 1 track: 2.5 ms, full stroke: 23.0 ms

- » layout

- heads: 1, cylinders: 22784 (user), 10336 (actual)

- sectors per track: 293-560

#### Networks Data Transfer Specifications • The device that lets a system connect to a • Data buffer network: network interface card » 512 Kbytes on board the disk • Listens for data on the network important to • Media Transfer rate this system » 108.8 to 202.9 Mbits / sec • Bundles the bits into packets and signals the • Interface Transfer rate OS when a packet is complete » Ultra-DMA mode 4: 66.6 Mbytes/sec • Also takes packets from OS and sends them as » PIO mode 4: 16.6 Mbytes/sec bits on the wire 13 30-Apr-2004 30-Apr-2004 cse410-15-input-output © 2004 University of Washington cse410-15-input-output © 2004 University of Washington 14 Networking Interfaces Network Example **CNN** YOU • OS puts extra packets in to define where stream begins and ends Streams GET http://cnn.com/index.html GET http://cnn.com/index.html STREAMS • NIC puts extra bits in to Networking From: YOU To: CNN From: YOU To: CNN protocols define where packets PACKETS Packets GET http://cnn.com/index.html GET http://cnn.com/index.html begin and end NIC interface BITS Bits 10101111010101001 Internet 1010111101010100110101010101010101 15 30-Apr-2004 cse410-15-input-output © 2004 University of Washington 30-Apr-2004 cse410-15-input-output © 2004 University of Washington 16

- » Provides easy access control via the memory system

- Special I/O instructions

#### 30-Apr-2004

19

30-Apr-2004

Depends on:

» time sensitivity of data

» whether data is expected

#### Device to Memory

- *Direct Memory Access (DMA)* allows devices and memory to communicate without involvement of processor

- Processor sets up the transaction

- Device and memory transfer the data

- Device interrupts processor to signal completion

- The processor gets a lot of other work done while transfer is happening

cse410-15-input-output © 2004 University of Washington

#### Performance Issues in I/O

- Processors double in speed every 18 months

- Networks double in speed more slowly, perhaps every 3 years

- Disks improve more slowly, because they are limited by mechanical factors

- » however, bit density has gone up rapidly

#### The I/O Bottleneck

• System A

30-Apr-2004

- » processor speed = 100 MHz (clock cycle 10 ns)

- » disk transfer takes 10 ms

- » How many clock cycles elapse while disk transfer takes place?

- System B

- » processor speed = 1 GHz (clock cycle 1 ns)

- » disk transfer still takes 10 ms

- » How many clock cycles now?

23

21

#### I/O Bus Constraints

cse410-15-input-output © 2004 University of Washington

- Two primary design points that must be met

- High speed

30-Apr-2004

- » processor / memory, bulk devices / memory

- Flexibility

- » many types of I/O devices with widely varying characteristics

- » characteristics of future devices are unknown at design time

#### Designs

- The speed and flexibility constraints lead to designs which are

- » designed for speed

- processor-memory bus

- » designed for flexibility

- I/O bus

- » designed for both

- backplane bus

# Speed? Synchronous Bus

- For highest speed, all devices are designed to work together at the same high rate

- Synchronous buses have a clock signal that all devices on the bus are aware of

- Protocol for accessing the bus is relatively simple

- » control signals at specified clock cycles» data at specified clock cycles

| 30-Apr-2004 | cse410-15-input-output © 2004 University of Washington | 25 | 30- | -Apr-2004 | cse410-15-input-output © 2004 University of Washington | 26 |

|-------------|--------------------------------------------------------|----|-----|-----------|--------------------------------------------------------|----|

|             |                                                        |    |     |           |                                                        |    |

|             |                                                        |    |     |           |                                                        |    |

#### Synchronous Issues

- Runs fast

- but

- » all attached devices must be designed for this particular (probably proprietary) bus

- » must be short so that signals can propagate across the whole bus

- » fast today is slow tomorrow

#### Flexibility? Asynchronous Bus

- Devices access the bus by handshaking to determine who can go next

- No single clock

- » transactions are defined by control signal transitions

- Can accommodate a wide variety of device speeds and device types

#### Asynchronous Issues

- Flexible

- but

30-Apr-2004

- » the handshake adds overhead to each transfer

- » special cases pollute the protocol as it is extended to provide higher speed capabilities

- » extreme network effect: once a bus is popular, it lives long past its expected lifetime because there are so many devices that use it

cse410-15-input-output © 2004 University of Washington

# Bus Bandwidth

- Width of the bus

- » number of data lines can be increased to transfer more bits of data in parallel

- Multiplexing

- » data signals and control signals can be put on the same lines at different times to save hardware

- » or separated to overlap handshake and data transfer

- Multi-word transfers

» block transfers move more data per handshake

cse410-15-input-output © 2004 University of Washington

30-Apr-2004

30

#### Controlling bus access

- With multiple devices on the bus, something must control access

- Bus Master

- » device that is allowed to initiate transfers

- Single bus master

- » simple, because no contention

- » potential bottleneck, because one device is busy for every single transfer on the bus

# Multiple Masters and Arbitration

- Let several devices act as bus masters

- Must decide who is in control for any particular transaction

- Arbitration

- » daisy chain serial decision

- » centralized parallel one decider

- » distributed parallel many deciders

- » distributed with collision detection

31