# Interrupts CSE466

# What is an Interrupt?

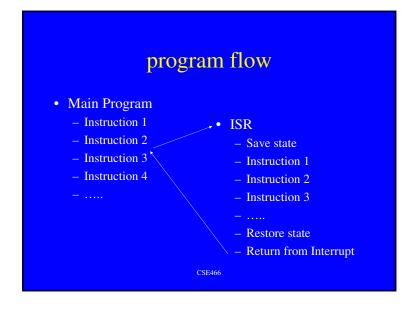

- Reaction to something in I/O

- Asynchronous in nature

- Invokes Interrupt handler, or ISR

CSE46

# Saving and Restoring the context

- Processor and compiler dependant

- Must ensure that registers are saved

- Must save return vector

- Must restore state

CSE466

#### **Disabling Interrupts**

- Disable instruction

- Priority interrupts

- Higher priority can interrupt

- Lower priority can't

- Non-maskable interrupts

- Does the AVR have Priority or non-maskable interrupts?

CSE466

## **More Questions**

- If interrupts happen at the same time, which ISR does the processor execute?

- Can one interrupt request signal interrupt another interrupt routine?

CSE46

## Questions about Interrupts

- How does the processor find the ISR?

- How does it know where the table is?

- Can an ISR be interrupted in the middle of an instruction?

CSE466

## Disabling Questions...

- What happens to interrupts that occur while interrupts are disabled?

- What if I disable interrupts and forget to reenable them?

- Can I disable or enable them twice?

- What about start-up?

CSE466