| Directory Protocol Messages                  |                                                     |                               |                           |  |

|----------------------------------------------|-----------------------------------------------------|-------------------------------|---------------------------|--|

| Message type                                 | Source                                              | Destination                   | Msg Content               |  |

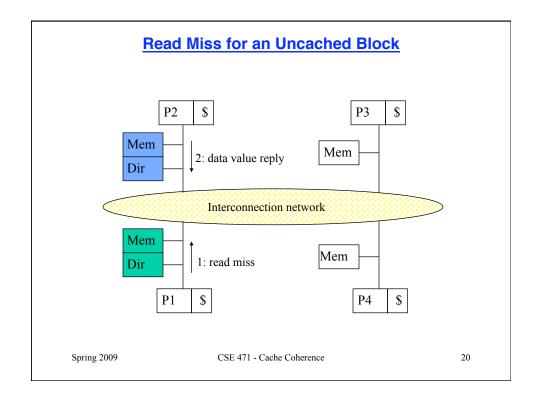

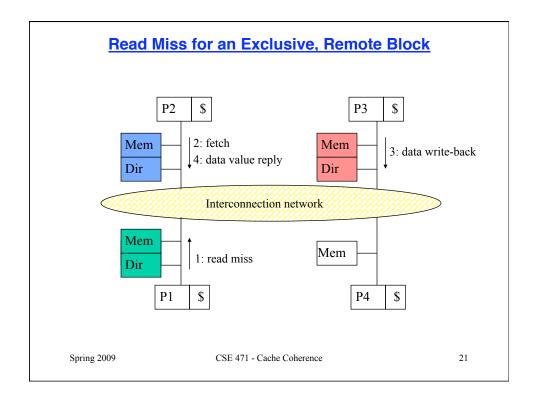

| Read miss                                    | Local cache                                         | Home directory                | P, A                      |  |

|                                              | P reads data at address .<br>ead sharer and arrange | ,                             |                           |  |

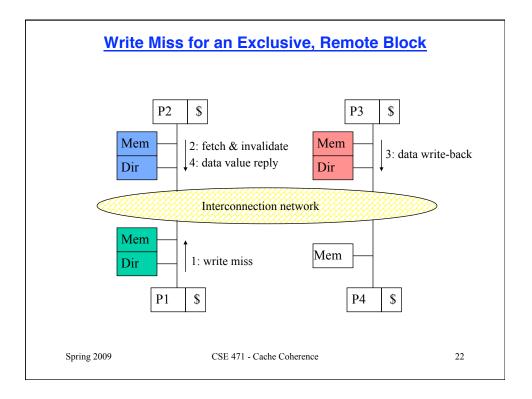

| Write miss                                   | Local cache                                         | Home directory                | P, A                      |  |

|                                              | P writes data at address<br>exclusive owner and ar  | A;<br>range to send data back |                           |  |

| Invalidate                                   | Home directory                                      | Remote caches                 | А                         |  |

| – Invalidate d                               | a shared copy at address                            | s A.                          |                           |  |

| Fetch                                        | Home directory                                      | Remote cache                  | А                         |  |

| - Fetch the b                                | lock at address A and se                            | end it to its home directory  | ,                         |  |

| Fetch/Invalidate                             | Home directory                                      | Remote cache                  | А                         |  |

| <ul> <li>Fetch the back the cache</li> </ul> | lock at address A and se                            | end it to its home directory  | ; invalidate the block in |  |

| Data value reply                             | Home directory                                      | Local cache                   | Data                      |  |

| – Return a da                                | ta value from the home                              | memory (read or write mi      | iss response)             |  |

| Data write-back                              | Remote cache                                        | Home directory                | A, Data                   |  |

| – Write-back                                 | a data value for addres.                            | s A (invalidate response)     |                           |  |

| Spring 2009                                  | CSE 471                                             | 1 - Cache Coherence           | 23                        |  |

| False Sharing                                                                                                                                                                                                                                                                                                                                                                                 |    |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|

| Impact aggravated by:<br>• block size: why?<br>• cache size: why?<br>• large miss penalties: why?                                                                                                                                                                                                                                                                                             |    |  |  |  |

| <ul> <li>Reduced by:</li> <li>coherency protocols (state per subblock) <ul> <li>let cache blocks become incoherent as long as there is only false sharing</li> <li>make them coherent if any processor true shares</li> <li>compiler optimizations (group &amp; transpose, cache block padding)</li> <li>cache-conscious programming wrt initial data structure layout</li> </ul> </li> </ul> |    |  |  |  |

| Spring 2009 CSE 471 - Cache Coherence                                                                                                                                                                                                                                                                                                                                                         | 30 |  |  |  |