| Dynamic Scheduling         |                                                          |                                             |         |  |

|----------------------------|----------------------------------------------------------|---------------------------------------------|---------|--|

| Why come b                 | ack?                                                     |                                             |         |  |

| <ul> <li>higher</li> </ul> | chip densities                                           |                                             |         |  |

| <ul> <li>hardw</li> </ul>  | are design was gen                                       | eralized                                    |         |  |

| • gr                       | eater need to hide o                                     | other kinds of latencies as:                |         |  |

|                            | <ul> <li>discrepancy betw</li> </ul>                     | een CPU & memory speeds in                  | creased |  |

|                            | <ul> <li>branch mispredic<br/>superpipelining</li> </ul> | tion penalty increased from                 |         |  |

| • us<br>inc                | ed a more general<br>cludes loads & bran                 | register renaming mechanism t<br>ches       | that    |  |

| <ul> <li>hardw</li> </ul>  | are design was upd                                       | ated                                        |         |  |

| • ne                       | ed to preserve pred                                      | cise interrupts                             |         |  |

| • th                       | erefore commit inst                                      | uctions in-order                            |         |  |

| more                       | need to expolit ILP                                      |                                             |         |  |

| • pr                       | ocessors now issue                                       | multiple instructions at the sar            | ne time |  |

| 2 styles: lar              | ge physical register                                     | file & reorder buffer                       |         |  |

| (F                         | 10000-style)                                             | (PentiumPro-style)                          |         |  |

| ~                          |                                                          |                                             | -       |  |

| Spring 2012                |                                                          | Out-of-Order Execution<br>Register Renaming | 2       |  |

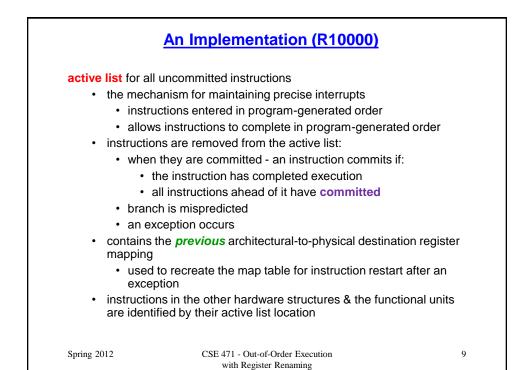

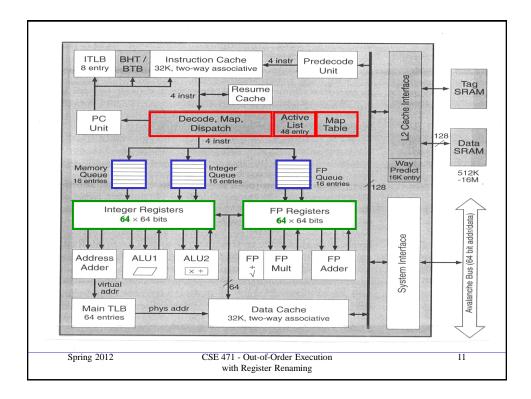

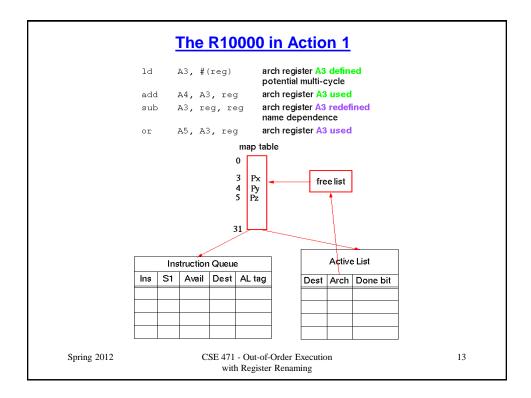

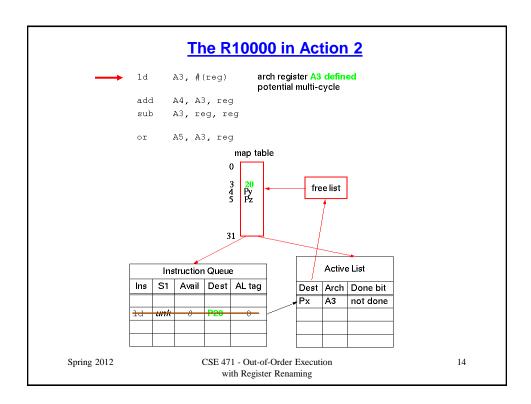

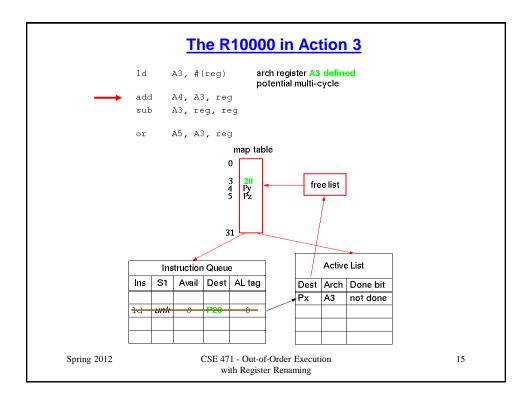

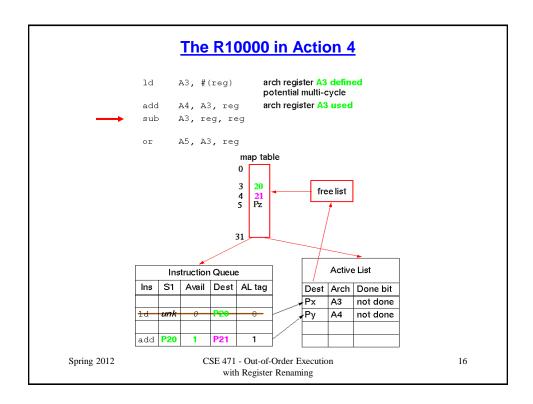

| R10000 Execution                         |                                                                  |           |  |  |

|------------------------------------------|------------------------------------------------------------------|-----------|--|--|

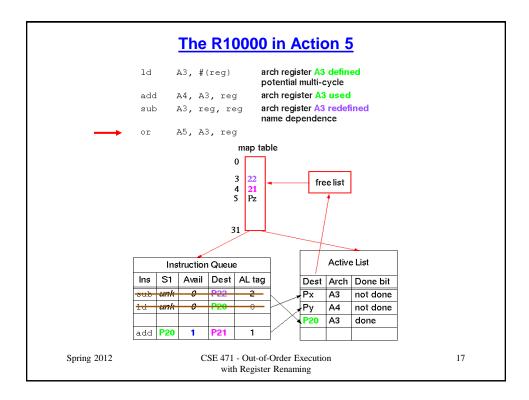

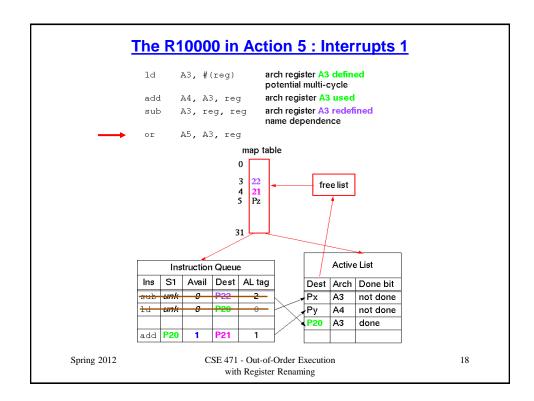

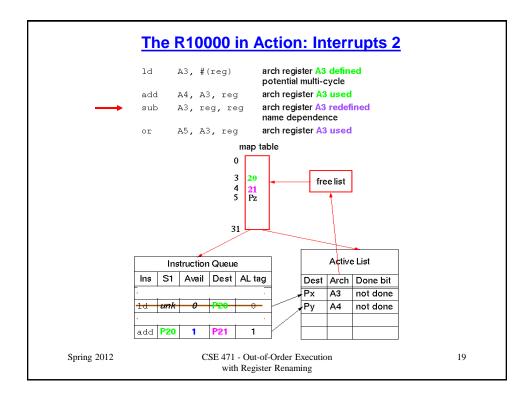

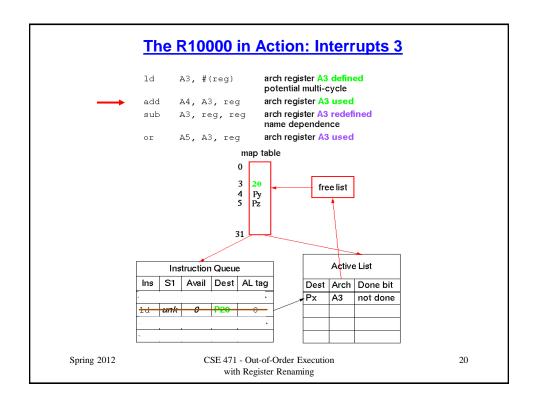

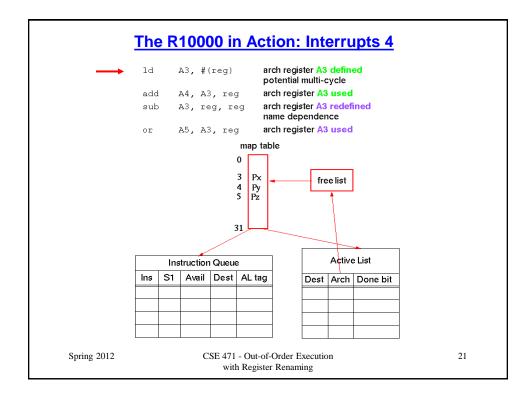

| In-order issue                           | (have already fetched instructions)                              |           |  |  |

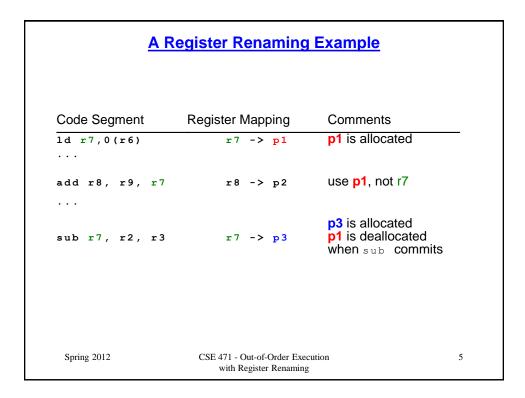

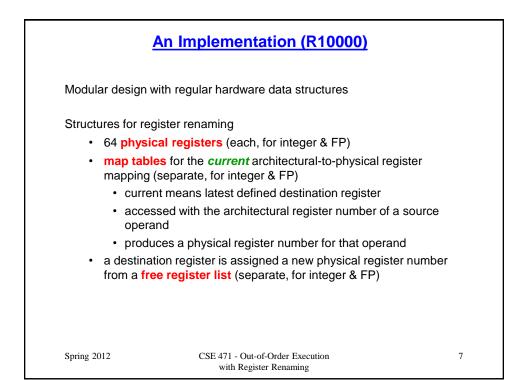

| <ul> <li>rename</li> </ul>               | e architectural registers to physical registers via a m          | nap table |  |  |

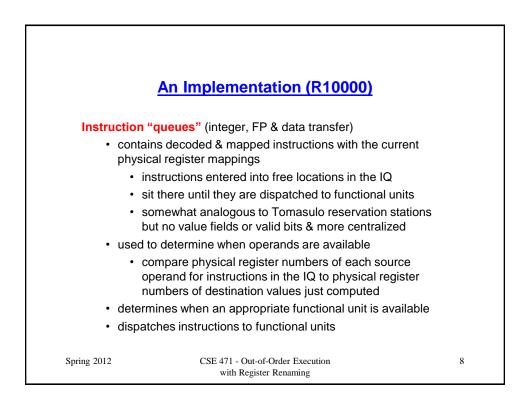

|                                          | structural hazards for instruction queues (integer, mactive list | nemory &  |  |  |

| <ul> <li>issue u</li> </ul>              | p to 4 instructions to the instruction queues                    |           |  |  |

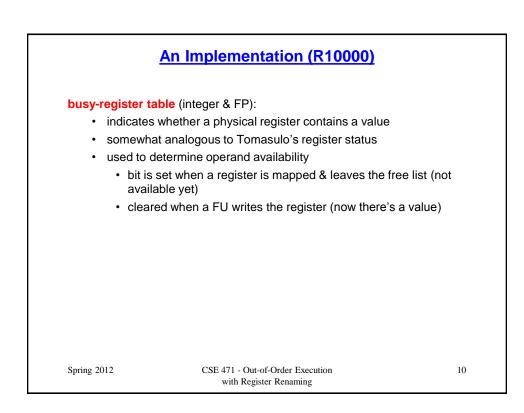

| Out-of-order                             | execution (to increase ILP)                                      |           |  |  |

| <ul> <li>instruct<br/>calcula</li> </ul> | tion queues that indicate when an operand has bee<br>ted         | n         |  |  |

| • ead                                    | ch instruction monitors the setting of the busy-regist           | ter table |  |  |

| <ul> <li>set bus</li> </ul>              | y-register table entry for the destination register              |           |  |  |

| <ul> <li>detect</li> </ul>               | functional unit structural & RAW hazards                         |           |  |  |

| <ul> <li>dispate</li> </ul>              | h instructions to functional units & execute them                |           |  |  |

| In-order com                             | mit (to preserve precise interrupts)                             |           |  |  |

| <ul> <li>this &amp; p</li> </ul>         | previous program-generated instructions have comp                | pleted    |  |  |

| <ul> <li>physica</li> </ul>              | al register in previous mapping returned to free list            |           |  |  |

| <ul> <li>rollbacl</li> </ul>             | k on interrupts                                                  |           |  |  |

| Spring 2012                              | CSE 471 - Out-of-Order Execution<br>with Register Renaming       | 22        |  |  |