## More Embedded Microcontrollers

- Motorola 68HC11

- Microchip PIC

- Motorola 683××

- Motorola 68328

- Intel i960

- Motorola MPC823

- Motorola ColdFire

CSE 477 - Autumn 1999 - Introduction - 1

## Motorola 68HC11

- Motorola 68HC11 (A1 model)

- 8-bit microcontroller with a M6800/M6801 processor core

- I on-board 512-byte EEPROM and 256-byte RAM

- 16-bit timer system with input capture and output compare

- I built-in A/D converter for 8 analog inputs

- I serial communications interfaces

- Development board for 68HC11 (M68HC11EVB)

- I 68HC11A1 system with 8K user EPROM and up to 16K user RAM

- port replacement unit

- to regain I/O ports used for memory addressing

- I two serial communications interfaces

- I on-board monitor program for downloading and debugging programs

- includes basic I/O utilities

## MC68HC11 and EVB

- Review manuals

- I learn how to read documentation

- Instruction set

- I instruction capabilities

- timing

- Special registers and integrated I/O devices

- I input capture

- I output compare

- I analog/digital conversion

- Interrupt organization

- Memory space and its allocation

- Timers

CSE 477 - Autumn 1999 - Introduction - 3

# Small microcontrollers

#### 68HC11

- I basic microcontroller with simple instruction set

- I full-featured (many of the same features as larger microcontrollers)

- I good real-time capabilities

- A/D conversion built-in

- cheap

- I very common (lots of resources available including on web)

- I public domain C compiler available

- I evaluation board with debugging support (BUFFALO ROM)

## PIC (Microchip)

- small footprint (as few as 24 pins)

- I no external system bus

- I lots of members of family differentiated by I/O pin capabilities

- A/D, serial I/O, interrupts, input capture, etc.

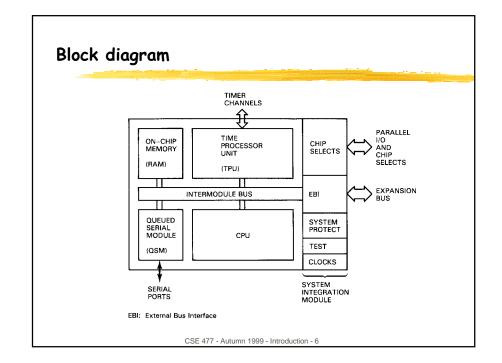

## Motorola MC683xx

- Designed by Motorola for automotive, data acquisition, printers, plotters, cameras, and other consumer products

- Introduced in 1989 (9 years ago)

- General characteristics

- I operate in harsh environment (-40 to 125°C and noise)

- low power (~625mW), low cost ~\$12

- I crunch numbers (execute control loops)

- I clock frequency (up to 78MHz)

#### Functional units

- CPU32 (68020 processor core)

- I SIM (System Integration Module)

- GPT (General Purpose Timer)

- QSM (Queued Serial Module)

- I TPU (Time Processor Unit)

## Functional blocks

- CPU32

- 32-bit processor based on 68020

- System Integration Module

- I controls external bus, I/O functions and system clock

- Time Processor Unit

- I 16-channel timer/counter unit

- I controls internal/external events

- Memory Module

- I on-chip RAM with stand-by power feature

- A/D

- 16 channel queued

- CAN protocol

- I Controller Area Network (automative bus, protocol)

# Time Processor Unit

- A microcontroller dedicated to timing control

- Two 16-bit timers/registers

- I free running based on system clock

- I can be controlled with external clock

- 16 independent channels (input or output)

- Functions

- I input capture

- I period or pulse width accumulation

- I output compare

- pulse width modulation

- stepper motor control

- automotive functions (fire spark plugs, determine engine rotation)

# Clocks and Timers

- System clock

- Periodic interrupt timer

- Software watchdog timer

- Bus monitor

- Synchronous communication

- I baud rate, delay, min idle

- Asynchronous communication baud rate

- TPU timers

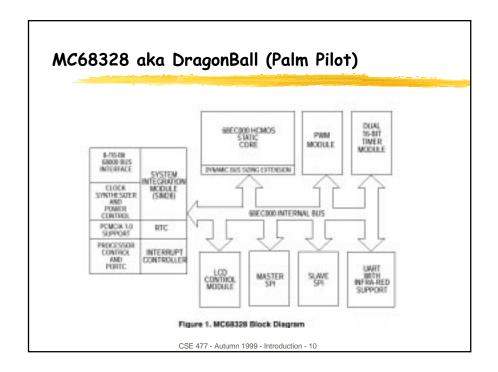

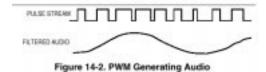

# PWM on DragonBall

- PWM transforms duty cycle into an average analog value

- In addition to controlling motor velocity, can synthesize music

CSE 477 - Autumn 1999 - Introduction - 11

# I/O Bottleneck

- Off-chip communication very slow relative to processing speeds

- I processor generating lots of memory requests

- I multiple devices competing for system bus

- Technology wave increasing the gap in performance

- I processors running faster

- interconnect bandwidth increasing at slower rate

- How do local area networks handle this problem?

- I restrict communication

- I hubs, gateways

- Solution

- I off load communication to a communication processor

# Intel's Approach

## A two-pronged attack

- I hardware: communication processor

- software: device-drivers

## Use a RISC processor to handle communication for the main processor

- I isolate main processor from slower peripherals

- I reduce interrupts to CPU

- support for system busses running at different clock rates

## Define a new standard: Intelligent I/O

- I standardize device-drivers

- I minimize OS dependencies

- I increase system throughput

CSE 477 - Autumn 1999 - Introduction - 13

# System w/ Communication Processor

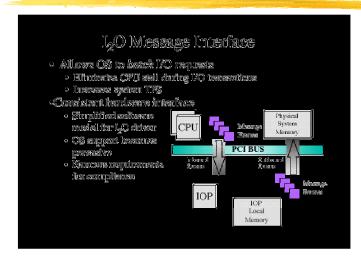

# $I_2O$

## Goals

- abstract the I/O subsystem

- I improve system throughput

- I enable rapid deployment of new I/O technology

## Message-passing paradigm

- supports peer communication

- simplifies device-drivers

CSE 477 - Autumn 1999 - Introduction - 15

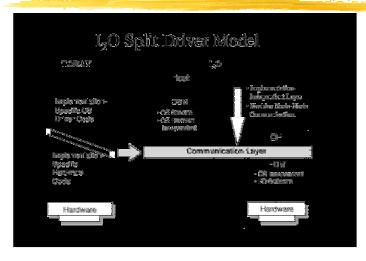

# I<sub>2</sub>O Device-Drivers

# I20 Message Passing

CSE 477 - Autumn 1999 - Introduction - 17

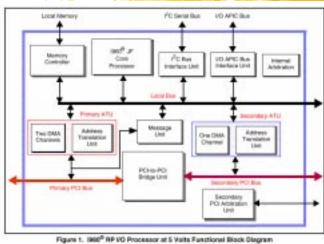

# Intel i960-RP Processor

## Main features

- PCI to PCI bridge

- messaging unit

- mechanism to transfer data between the PCI system and 80960

- I DMA access to both PCI busses

- I address translation units

- 64-byte input and output queues

- queues allow transactions to complete on initiating bus before they complete on target bus

- 7 to 150 MIPS

# i960 Block Diagram

#### CSE 477 - Autumn 1999 - Introduction - 19

# i960 Messaging Unit

## Message registers

- i 960 sends and receives messages via special registers

- when written an interrupt generated to i960 or PCI

## Doorbell registers

- I inbound and outbound doorbells

- either hardware or software can generate doorbell interrupts

- I contain interrupt status from other message unit mechanisms

## Circular queues

- I two inbound and two outbound queues

- I posted messages contain orders

- I free messages indicate operation completed and message can be reused

# Motorola's Approach

- Use 2 RISC processors

- 1 32-bit PowerPC core for application code

- 1 32-bit customized RISC for imaging and communication

- Put communication processor on same die as main processor

- system on a chip

- I incorporate features common in portable devices

- I single-chip solution for consumer electronics

- signal processing functions

CSE 477 - Autumn 1999 - Introduction - 21

# Research Deal Institution Deal Instituti

## MPC 823 Features

- Performance of 66 MIPS @ 50MHz

- Low power

- consumes less than 180mW @ 25MHz

- 1 2.2V internal, 3.3V I/O boundary

- I doze functional units disabled except

- PLL, mem-controller, real-time clock, LCD, comm. proc in standby

- I sleep all units disabled except

- real-time clock, periodic interrupt timer, PLL active for fast wakeup

- I deep sleep all units disabled except

- real-time clock, periodic interrupt timer

- 1K data cache and 2K instruction cache

- PCMCIA support

CSE 477 - Autumn 1999 - Introduction - 23

# Communication Module Features

- Interfaces to PPC core via on-chip dual ported RAM

- Protocols supported include

- Ethernet/IEEE 802.3

- Universal Serial Bus (USB), AppleTalk, UART/USART, I2C

- IrDA 1.1

- ISDN

- 16x16 bit multiply accumulate (MAC)

- DSP functions

- V.32bis/V.34bis datapump filter

- I JPEG compression

- Four independent baud rate generators

# More Communication Module Features

## ■ Video/LCD controller

- supports passive LCD and NTSC/PAL encoders

- end of frame interrupt generation

- I programmable display active area

- I programmable background color for inactive area

- I 1,2,4-bit per pixel grayscale

- I built-in color RAM with 256 12-bit entries

- I programmable polarity for all LCD interface signals

CSE 477 - Autumn 1999 - Introduction - 25

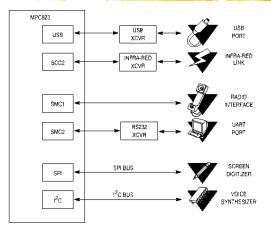

# PDA Based on MPC823

Figure 16-2. Example of a PDA Application

CSE 477 - Autumn 1999 - Introduction - 27

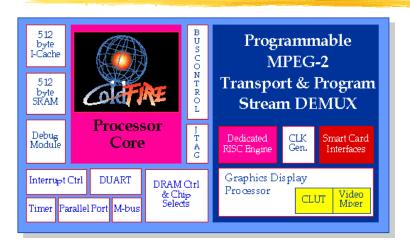

## ColdFire Features

- Variable instruction length RISC 68K processor

- I subset of 68K instruction set

- 16, 32, 48-bit instruction sizes

- single-cycle instruction execution

- tighter code density than 32 or 64-bit processors

- Completely synthesizable

- I core can be used in system on a chip designs

- Performance: 36 MIPS

- Price: ~\$25