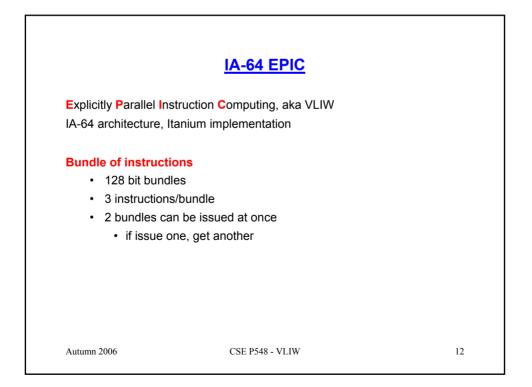

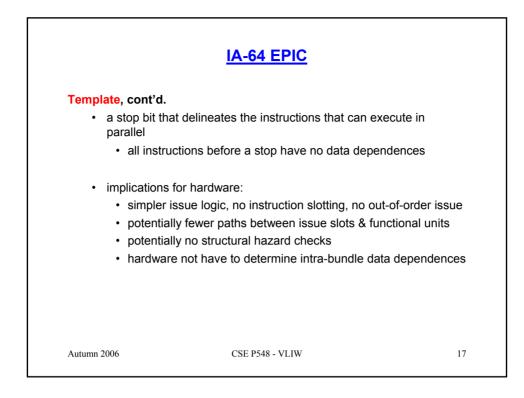

| <ul><li>type of c</li><li>instruction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                    | <b>IA-64 EPIC</b><br>the bundle that indicates:<br>operation for each instruction<br>on order in bundle<br>es (2 of 24) |    |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|----|--|--|

| <ul> <li>examples (2 of 24)</li> <li>M I I</li> <li>M F B</li> <li>M: load &amp; manipulate the address (e.g., increment an index)</li> <li>I: integer ALU op</li> <li>F: FP op</li> <li>B: transfer of control</li> <li>other, e.g., stop (see below)</li> <li>restrictions on which instructions can be in which slots</li> <li>schedule code for functional unit availability (i.e., template types) &amp; latencies</li> </ul> |                                                                                                                         |    |  |  |

| Autumn 2006                                                                                                                                                                                                                                                                                                                                                                                                                        | CSE P548 - VLIW                                                                                                         | 16 |  |  |

| IA-64 EPIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                 |    |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----|--|--|

| <ul> <li>More complication</li> <li>don't want to store speculative values to memory <ul> <li>special instructions check integer register poison bits to detect whether value is speculative (for nonspeculative code or exceptions)</li> <li>OS can override the ban on storing (e.g., for a context switch)</li> <li>different mechanism for speculative floating point values</li> </ul> </li> <li>backwards compatibility <ul> <li>x86 (IA-32)</li> <li>PA-RISC compatible memory model (segments)</li> </ul> </li> </ul> |                 |    |  |  |

| Autumn 2006                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CSE P548 - VLIW | 20 |  |  |