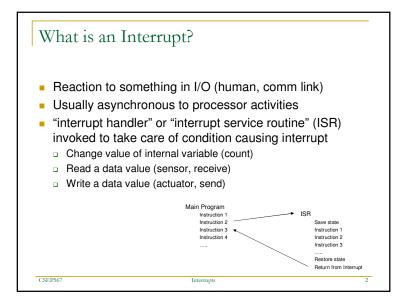

- Fundamental concept in computation

- Interrupt execution of a program to "handle" an event

- Don't have to rely on program relinquishing control

- Can code program without worrying about others

- Issues

CSEP567

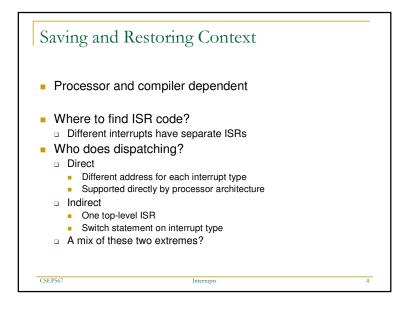

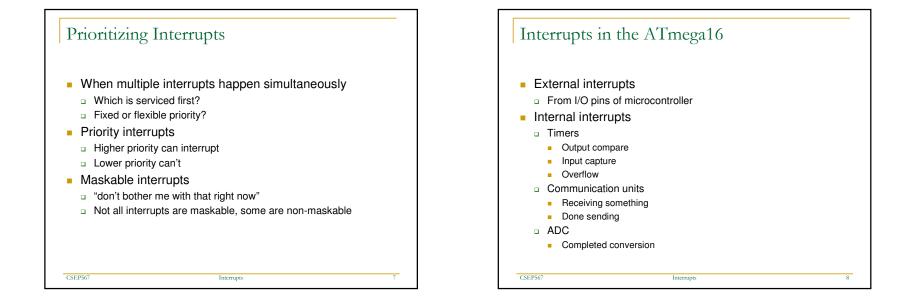

- What can interrupt and when?

- Where is the code that knows what to do?

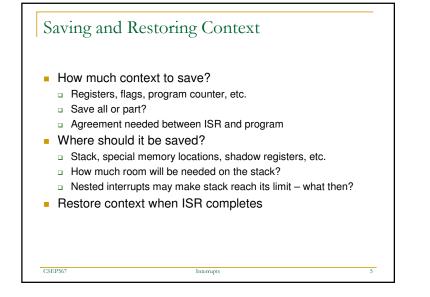

- How long does it take to handle interruption?

- Can an interruption be, in turn, interrupted?

- How does the interrupt handling code communicate its results?

- How is data shared between interrupt handlers and programs?

Interrupts

1

## Ignoring Interrupts Can interrupts be ignored? It depends on the cause of the interrupt No, for nuclear power plant temperature warning Yes, for keypad on cell phone (human timescale is long) When servicing another interrupt Ignore others until done Can't take too long – keep ISRs as short as possible Just do a quick count, or read, or write – not a long computation Interrupt disabling Will ignored interrupt "stick"? Rising edge sets a flip-flop . Or will it be gone when you get to it? Level changes again and its as if it never happened Don't forget to re-enable

| Interrupt Jump V      | ect            | 01 1    | Lai                                              | JIC                            |                                                                  |

|-----------------------|----------------|---------|--------------------------------------------------|--------------------------------|------------------------------------------------------------------|

|                       | Address        | Labels  | Code                                             |                                | Conments                                                         |

|                       | \$000          |         | jmp                                              | RESET                          | ; Reset Handler                                                  |

|                       | \$002          |         | jmp                                              | EXT_INT 0                      | ; IRQO Handler                                                   |

|                       | \$004          |         | jmp                                              | EXT_INT1                       | ; IRQ1 Handler                                                   |

| Fixed location        | \$006<br>\$008 |         | jmp                                              | TIM2_COMP                      | ; Timer2 Compare Handler                                         |

|                       | \$008<br>\$008 |         | jmp<br>1mp                                       | TIM2_OVF<br>TIM1 CAPT          | ; Timer2 Overflow Handler<br>; Timer1 Capture Handler            |

| in memory to find     | SOOC           |         | 1002                                             | TIM1_COMPA                     | ; Timeri Capture Mandler<br>; Timeri CompareA Handler            |

|                       | SOOR           |         | 1000                                             | TIM1 COMPB                     | ; Timerl Compares Handler                                        |

| first instruction for | \$010          |         | jmp                                              | TIM1_OVF                       | 7 Timer1 Overflow Handler                                        |

| and the terms of the  | \$012          |         | jmp                                              | TIM0_OVF                       | ; TimerO Overflow Handler                                        |

| each type of          | \$014          |         | jmp                                              | SPI_STC                        | ; SPI Transfer Complete Handler                                  |

| interrunt             | \$016          |         | jmp                                              | USART_RIC                      | ; USART RX Complete Handler                                      |

| interrupt             | \$018          |         | jmp                                              | USART_UDRE                     | ; UDR Empty Handler                                              |

|                       | \$01A<br>\$01C |         | jmp<br>1mp                                       | USART_TIC<br>ADC               | ; USART TX Complete Handler<br>; ADC Conversion Complete Handler |

| Only room for one     | \$01C          |         | 1002                                             | EE RDY                         | ; REPROM Ready Handler                                           |

| instruction           | \$020          |         | 1000                                             | ANA COMP                       | / Analog Comparator Handler                                      |

| Instruction           | \$022          |         | jmp                                              | TWSI                           | ; Two-wire Serial Interface Handler                              |

| JMP to location       | \$0.24         |         | jmp                                              | EXT_INT 2                      | ; IRQ2 Handler                                                   |

|                       | \$0.26         |         | jmp                                              | TIM0_COMP                      | ; TimerO Compare Handler                                         |

| of complete ISR       | \$028          |         | jmp                                              | SPM_RDY                        | ; Store Program Memory Ready Handler                             |

| 1                     | ,              |         |                                                  |                                |                                                                  |

|                       | \$02A<br>\$02B | RESET : | 1di<br>out                                       | r16, high (RAMEND)<br>SPH, r16 | ; Main program start<br>; Set Stack Pointer to top of RAM        |

|                       | \$028<br>\$02C |         | 141                                              | r16.low(RAMEND)                | , see search remeat to top of har                                |

|                       | \$02D          |         | out                                              | SPL, r16                       |                                                                  |

|                       | \$02E          |         | sei                                              |                                | ; Enable interrupts                                              |

|                       | \$02F          |         | <inst< td=""><td>r&gt; xxx</td><td></td></inst<> | r> xxx                         |                                                                  |

|                       |                |         |                                                  |                                |                                                                  |

| Special FunctionIO Register - |                                                                  |                                 |                                                                     |                                                    |  |  |  |

|-------------------------------|------------------------------------------------------------------|---------------------------------|---------------------------------------------------------------------|----------------------------------------------------|--|--|--|

| SFIOR                         | Bit                                                              | 7 6                             | 5                                                                   | 4 3 2 1 0                                          |  |  |  |

|                               |                                                                  | ADTS2 ADTS                      |                                                                     | <ul> <li>ACME PUD PSR2 PSR10 SFIOR</li> </ul>      |  |  |  |

|                               | Read/Write<br>Initial Value                                      | RAV RAV                         | R/W<br>0                                                            | R R/W R/W R/W R/W<br>0 0 0 0 0                     |  |  |  |

|                               | Bit 7:5 - ADT\$2:0: ADC Auto Triager Source                      |                                 |                                                                     |                                                    |  |  |  |

|                               | Note that swi<br>will generate<br>start a conve<br>ger event, ev | itching from a<br>a positive ed | trigger sourd<br>lge on the trig<br>ng to Free Ru<br>Interrupt Flag |                                                    |  |  |  |

|                               | ADTS2                                                            | ADTS1                           | ADTS0                                                               | Trigger Source                                     |  |  |  |

|                               | 0                                                                | 0                               | 0                                                                   | Free Running mode                                  |  |  |  |

|                               | 0                                                                | 0                               | 1                                                                   | Analog Comparator                                  |  |  |  |

|                               | 0                                                                | 1                               | 0                                                                   | External Interrupt Request 0                       |  |  |  |

|                               | 0                                                                | 1                               | 1                                                                   | Timer/Counter0 Compare Match                       |  |  |  |

|                               | 1                                                                | 0                               | 0                                                                   | Timer/Counter0 Overflow                            |  |  |  |

|                               | 1                                                                | 0                               | 1                                                                   | Timer/Counter Compare Match B                      |  |  |  |

|                               | 1                                                                | 1                               | 0                                                                   | Timer/Counter1 Overflow                            |  |  |  |

|                               | 1                                                                | 1                               | 1                                                                   | Timer/Counter1 Capture Event                       |  |  |  |

|                               | • Bit 4 – Res                                                    | s: Reserved                     |                                                                     | ensure compatibility with future devices, this bit |  |  |  |