©Copyright 2014

Benjamin P. Wood

# Software and Hardware Support for Data-Race Exceptions

Benjamin P. Wood

A dissertation submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

University of Washington

2014

Reading Committee:

Dan Grossman, Chair

Luis Ceze, Chair

Zachary Tatlock

Program Authorized to Offer Degree: Computer Science & Engineering

#### University of Washington

#### Abstract

Software and Hardware Support for Data-Race Exceptions

Benjamin P. Wood

Co-Chairs of the Supervisory Committee: Associate Professor Dan Grossman Computer Science & Engineering

Associate Professor Luis Ceze Computer Science & Engineering

Some researchers have proposed data-race exceptions to mitigate the ill effects of data races in shared-memory multithreaded programs. Data-race exceptions make every data race an explicit fail-stop error at run-time. Implementing data-race exceptions naturally requires accurate dynamic data-race detection with low performance overhead, yet existing data-race detectors compromise either accuracy or performance. Hardware data-race detectors solutions are fast, but inaccurate. Accurate software data-race detectors slow execution by several times. This dissertation presents three new systems to bring accurate and fast language-level data-race exceptions closer to feasibility.

Race Detection in Software and Hardware (RADISH) accelerates an accurate software data-race detection algorithm by mapping common cases to highly-optimized hardware support. By falling back to software support in rare cases, RADISH maintains full accuracy for low-level programs while achieving good performance. We show RADISH's accuracy via its equivalence to a canonical accurate software algorithm for data-race detection.

Low-level Abstractable Race Detection (LARD) virtualizes accurate low-level data-race detectors, such as RADISH, to support accurate data-race detection for high-level languages. Experimental evaluation shows that existing low-level data-race detectors are inaccurate on high-level programs in practice, while our LARD implementation is accurate and preserves the performance of the low-level data-race detector.

Fast Instrumentation Bias (FIB) is a cooperative synchronization protocol designed to reduce the overheads of pure-software accurate dynamic data-race detection. Analysis barriers—the code inserted before each memory access in the program to check and update analysis metadata—may execute concurrently. If barriers are not atomic, they may fail to detect true data races. Existing implementations either allow non-atomic barriers, sacrificing guaranteed accuracy, or employ pessimistic synchronization to ensure barrier atomicity and analysis accuracy. FIB exploits analysis invariants to guarantee barrier atomicity with no synchronization in the common case, at the cost of expensive synchronization in rare cases. Experimental evaluation shows that FIB is faster than a highly optimized conventional implementation of barrier atomicity on several benchmarks and slower on others, varying with the rate of updates to shared data. Conservative dynamic thread-escape analysis can lower overheads of both implementations while maintaining accuracy.

# Table of Contents

|           |         | 1                                                                             | Page |

|-----------|---------|-------------------------------------------------------------------------------|------|

| Table of  | f Conte | nts                                                                           | i    |

| List of I | Figures |                                                                               | vii  |

| List of 7 | Γables  |                                                                               | ix   |

| Acknow    | ledgme  | ents                                                                          | X    |

| Chapter   | 1:      | Introduction                                                                  | 1    |

| 1.1       | Data    | races are exceptional                                                         | 2    |

| 1.2       | Proble  | em: Accurate language-level data-race detection is slow                       | 3    |

|           | 1.2.1   | Fast hardware-supported data-race detection is inaccurate                     | 4    |

|           | 1.2.2   | Low-level data-race detection is inaccurate on high-level languages           | 4    |

|           | 1.2.3   | Software data-race detectors use costly defensive synchronization             | 5    |

| 1.3       | Disser  | tation Goals and Contributions                                                | 6    |

|           | 1.3.1   | RADISH: Accurate and Fast Race Detection in Software and Hardware (Chapter 3) | 6    |

|           | 1.3.2   | LARD: Low-level Abstractable Race Detection (Chapter 4)                       |      |

|           | 1.3.3   | FIB: Fast Instrumentation Bias for Pure-Software Data-Race Detection          |      |

|           |         | (Chapter 5)                                                                   | 8    |

| 1.4       | Public  | cation and Collaboration                                                      | 9    |

| Chapter   | 2:      | Foundations and Related Work                                                  | 10   |

| 2.1       | Data I  | Races                                                                         | 10   |

|           | 2.1.1   | The Happens-Before Relation and Data Races                                    | 11   |

|           | 2.1.2   | Data Races and Higher-Level Properties of Program Executions                  | 12   |

| 2.2       | Accur   | ate Dynamic Data-Race Detection                                               | 12   |

|                   | 2.2.1  | Vector Clocks                                                     | 12 |

|-------------------|--------|-------------------------------------------------------------------|----|

|                   |        | 2.2.1.1 Synchronization tracking                                  | 13 |

|                   |        | 2.2.1.2 Access tracking and checking                              | 16 |

|                   |        | 2.2.1.3 Variants                                                  | 17 |

|                   | 2.2.2  | Alternative Happens-Before Representations                        | 18 |

|                   | 2.2.3  | First-Race Accuracy                                               | 18 |

|                   | 2.2.4  | Data-Race Exceptions                                              | 20 |

|                   | 2.2.5  | Performance                                                       | 20 |

| 2.3               | Conse  | rvative Data-Race Detection                                       | 21 |

|                   | 2.3.1  | Lock Sets                                                         | 22 |

|                   | 2.3.2  | Generalization to Other Executions                                | 22 |

| 2.4               | Precis | e Data-Race Detection                                             | 23 |

|                   | 2.4.1  | Data Races that Violate Sequential Consistency                    | 23 |

|                   | 2.4.2  | Other Precise Techniques                                          | 24 |

| 2.5               | Best-H | Effort Data-Race Detection and Other Tools                        | 25 |

| 2.6               | Static | Data-Race Detection                                               | 26 |

| Charta            | 9.     | RADISH: Accurate and Fast Race Detection in Software and Hardware | 20 |

| Chapte<br>3.1     |        |                                                                   |    |

| $\frac{3.1}{3.2}$ |        | luction                                                           |    |

| 3.2               | 3.2.1  | ADISH System                                                      |    |

|                   | 3.2.1  |                                                                   |    |

|                   | 3.2.3  | The RADISH Architecture                                           |    |

|                   | 3.2.3  | 3.2.3.1 In-Hardware Status                                        |    |

|                   |        | 3.2.3.2 Local Permissions                                         |    |

|                   | 3.2.4  | Maintaining In-Hardware Status and Local Permissions              |    |

|                   | 3.2.4  | 3.2.4.1 Maintaining In-Hardware Status                            |    |

|                   |        |                                                                   |    |

|                   | 205    | 3.2.4.2 Maintaining Local Permissions                             |    |

|                   | 3.2.5  | The RADISH Software Interface                                     |    |

|                   | 3.2.6  |                                                                   |    |

| กก                | 3.2.7  | An Example Trace                                                  |    |

| 3.3               | -      | alence to Canonical Vector-Clock Data-Race Detector               |    |

|                   | 3.3.1  | State                                                             |    |

|                   | 3.3.2  | No Cache Evictions, No Context Switches, No Optimizations         |    |

|                   |        | 3.3.2.1 Synchronization Tracking                                  | 43 |

|         |        | 3.3.2.2 Access Tracking and Checking                        | 43 |

|---------|--------|-------------------------------------------------------------|----|

|         | 3.3.3  | Cache Evictions                                             | 44 |

|         | 3.3.4  | Context Switches                                            | 45 |

|         | 3.3.5  | In-Hardware Status                                          | 45 |

|         | 3.3.6  | Local Permissions                                           | 46 |

|         |        | 3.3.6.1 Proof: Local Checks Suffice for Permitted Accesses  | 47 |

|         |        | 3.3.6.2 Proof: Local Updates Suffice for Permitted Accesses | 48 |

| 3.4     | Relate | d Work                                                      | 49 |

| 3.5     | Conclu | asions                                                      | 5  |

| Chapter | 4:     | LARD: Low-Level Abstractable Race Detection                 | 52 |

| 4.1     |        | uction                                                      | 52 |

|         | 4.1.1  | Low-Level Data Races $\neq$ Language-Level Data Races       | 53 |

|         | 4.1.2  | Low-Level Detection of Language-Level Data Races            |    |

|         | 4.1.3  | LARD Implementation and Evaluation                          | 55 |

|         | 4.1.4  | Contributions and Outline                                   | 55 |

| 4.2     | Low-L  | evel Abstractable Race Detection                            | 56 |

|         | 4.2.1  | Memory Access                                               | 57 |

|         | 4.2.2  | Synchronization                                             | 59 |

|         | 4.2.3  | Memory Allocation                                           | 59 |

|         | 4.2.4  | Memory Movement                                             | 6  |

|         | 4.2.5  | Thread Identity                                             | 62 |

|         | 4.2.6  | Sufficiency                                                 | 63 |

|         | 4.2.7  | Generality                                                  | 64 |

| 4.3     | Impler | mentation                                                   | 65 |

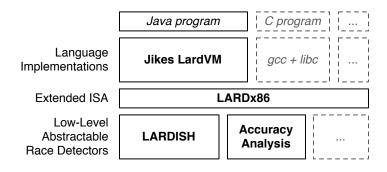

|         | 4.3.1  | The LARDx86 ISA                                             | 65 |

|         | 4.3.2  | The LARDISH Hardware Data-Race Detector                     | 67 |

|         | 4.3.3  | The Jikes LARDVM Java Virtual Machine                       | 69 |

|         |        | 4.3.3.1 Memory Tracking                                     | 69 |

|         |        | 4.3.3.2 Thread Identity and Synchronization                 | 70 |

|         |        | 4.3.3.3 Memory Management and Mapping                       | 70 |

|         |        | 4.3.3.4 Extent of Changes to Jikes RVM                      | 7  |

|         | 4.3.4  | Extensions for Accuracy Analysis                            | 7  |

| 4.4     | Evalua | ation                                                       | 72 |

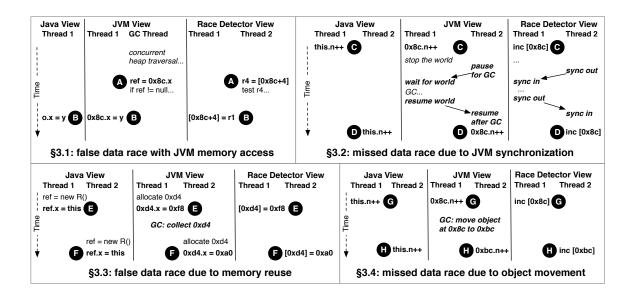

|         | 4.4.1  | False Data Races and Missed Data Races                      | 73 |

|         | 4.4.2  | Impacts of LARD Extensions                         |

|---------|--------|----------------------------------------------------|

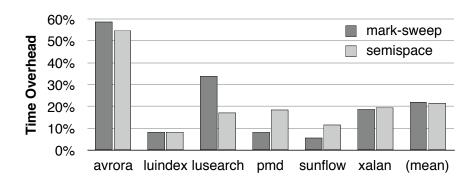

|         | 4.4.3  | Jikes LARDVM Performance on LARDISH                |

|         | 4.4.4  | Jikes LARDVM Performance on x86                    |

| 4.5     | Relate | d Work                                             |

|         | 4.5.1  | Virtualization and Language Semantics              |

|         | 4.5.2  | Compensation for Translation Artifacts             |

| 4.6     | Conclu | sions                                              |

| Chapter | 5:     | Fib: Fast Instrumentation Bias                     |

| 5.1     | Introd | uction                                             |

|         | 5.1.1  | Barrier Atomicity and Barrier-Access Ordering 85   |

|         | 5.1.2  | Pessimistic Barrier Atomicity                      |

|         | 5.1.3  | Cooperative Barrier Atomicity with Fib             |

|         | 5.1.4  | Contributions and Outline                          |

| 5.2     | FastTr | ack                                                |

|         | 5.2.1  | Access History                                     |

|         | 5.2.2  | Invariants                                         |

|         | 5.2.3  | Barriers                                           |

|         |        | 5.2.3.1 Write Barrier                              |

|         |        | 5.2.3.2 Read Barrier                               |

| 5.3     | The F  | IB Protocol                                        |

|         | 5.3.1  | Notation                                           |

|         | 5.3.2  | Ownership States                                   |

|         | 5.3.3  | State Transition Overview                          |

|         | 5.3.4  | Local Transitions                                  |

|         |        | 5.3.4.1 Exclusive Writes and Reads                 |

|         |        | 5.3.4.2 Shared Reads                               |

|         |        | 5.3.4.3 Optimizations                              |

|         | 5.3.5  | Single-Conflict Transitions                        |

|         |        | 5.3.5.1 Request Dispatch and Response Handling 107 |

|         |        | 5.3.5.2 Check and Transfer                         |

|         |        | 5.3.5.3 Queue Processing and Response              |

|         | 5.3.6  | Multiple-Conflict Transitions                      |

|         |        | 5.3.6.1 Interaction with Fence Transitions         |

|         |        | 5 3 6 9 Alternatives 120                           |

|     | 5.3.7  | Progress Guarantee                                                                                       |

|-----|--------|----------------------------------------------------------------------------------------------------------|

| 5.4 | Extens | sions                                                                                                    |

|     | 5.4.1  | Dynamic Thread-Escape Analysis                                                                           |

|     |        | $5.4.1.1  \text{Filtering Access Barriers}  \dots  \dots  \dots  122$                                    |

|     |        | 5.4.1.2 Filtering Synchronization Instrumentation $\dots \dots 125$                                      |

|     | 5.4.2  | Ownership State Initialization                                                                           |

|     |        | 5.4.2.1 CAS for Initial Ownership                                                                        |

|     |        | 5.4.2.2 $$ Indirect Initial Ownership via Thread-Escape Analysis $$ 126                                  |

| 5.5 | Implen | nentation                                                                                                |

|     | 5.5.1  | Common Metadata and Instrumentation                                                                      |

|     |        | 5.5.1.1 Metadata                                                                                         |

|     |        | 5.5.1.2  Instrumentation  .  .  .  .  .  .  .  .  .                                                      |

|     | 5.5.2  | FastTrack Implementations                                                                                |

|     | 5.5.3  | Fib Communication Infrastructure                                                                         |

|     | 5.5.4  | Dynamic Thread-Escape Analysis                                                                           |

| 5.6 | Evalua | tion                                                                                                     |

|     | 5.6.1  | Environment                                                                                              |

|     | 5.6.2  | Performance and Profiling Results $\ \ldots \ 133$ |

|     | 5.6.3  | Discussion                                                                                               |

|     |        | 5.6.3.1 Fib versus Cas                                                                                   |

|     |        | 5.6.3.2 Dynamic Thread-Escape Analysis                                                                   |

|     |        | 5.6.3.3 Scalability and Other Pessimistic Implementations 140                                            |

| 5.7 | Relate | d Work                                                                                                   |

|     | 5.7.1  | Biased Locking                                                                                           |

|     | 5.7.2  | Coherence, Permissions, and Protections                                                                  |

|     | 5.7.3  | Object Race Detection and Octet                                                                          |

|     | 5.7.4  | Dynamic Thread-Escape Analysis                                                                           |

| 5.8 | Limita | tions                                                                                                    |

|     | 5.8.1  | Sensitivity to Serialized Sharing                                                                        |

|     |        | 5.8.1.1 Fib versus Octet                                                                                 |

|     | 5.8.2  | Starvation of Atomic Lookup-and-Enqueue                                                                  |

|     | 5.8.3  | Dynamic Thread-Escape Analysis                                                                           |

| 5.9 | Future | Work                                                                                                     |

|     | 5.9.1  | Refined Ownership States                                                                                 |

|     |        | 5.9.1.1 Write- and Read-Exclusive States                                                                 |

|           |        | 5.9.1.2    | Independent or Bulk Transitions | 150 |

|-----------|--------|------------|---------------------------------|-----|

|           | 5.9.2  | Adaptive   | e Synchronization Selection     | 151 |

|           | 5.9.3  | Reprivati  | ization for Data-Race Detection | 151 |

|           |        | 5.9.3.1    | Unsound Reprivatization         | 152 |

|           |        | 5.9.3.2    | Sound Reprivatization           | 153 |

| 5.10      | Conclu | sions      |                                 | 154 |

| Chapter   | 6:     | Conclusio  | ons and Next Steps              | 155 |

| 6.1       | Summa  | ary of Cor | nclusions                       | 155 |

| 6.2       | Racing | Onward:    | Limitations and Future Work     | 157 |

| Reference | •AC    |            |                                 | 150 |

# List of Figures

| Fig | gure 1 | Number                                                                                                                                                                                                                               | Pa  | age |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|

|     | 2.1    | Syntax of execution traces                                                                                                                                                                                                           |     | 11  |

|     | 2.2    | Vector-clock data-race detector metadata                                                                                                                                                                                             |     | 13  |

|     | 2.3    | Vector-clock data-race detector                                                                                                                                                                                                      |     | 14  |

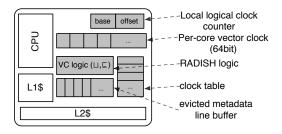

|     | 3.1    | Overview of the RADISH processor core. State added by RADISH is shaded.                                                                                                                                                              |     | 31  |

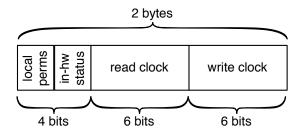

|     | 3.2    | RADISH's in-cache metadata format. Local permissions have 3 possible values, and in-hardware status 4 values, so we use 4 bits to represent the 12 combinations. 6 bits are left for each clock; we discuss rollover issues in [38]. |     | 32  |

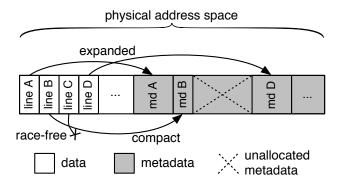

|     | 3.3    | Mapping from data to metadata addresses for a single processor. Each processor uses a distinct portion of the physical address space                                                                                                 |     | 33  |

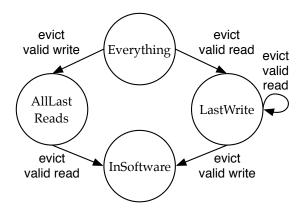

|     | 3.4    | In-hardware status is downgraded when metadata is evicted from the last-level cache                                                                                                                                                  |     | 35  |

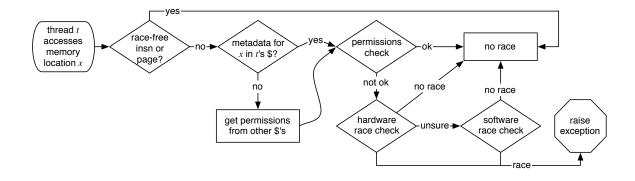

|     | 3.5    | Flowchart describing when and how RADISH performs data-race checks for each memory access                                                                                                                                            | •   | 37  |

|     | 4.1    | A naïve low-level data-race detector reports false data races and misses true data races in Java programs. Solid arrows are happens-before edges observed by the data-race detector. Each example contains three views of the same   |     |     |

|     |        | execution                                                                                                                                                                                                                            |     | 58  |

|     | 4.2    | The LARD environment                                                                                                                                                                                                                 |     | 65  |

|     | 4.3    | Execution time overhead of Jikes LARDVM normalized to unmodified Jikes RVM, both run on native x86                                                                                                                                   |     | 79  |

|     | 5.1    | Lost access history updates lead to a missed data race in an unsynchronized software data-race detector                                                                                                                              | ·   | 84  |

|     | 5.2    | FastTrack metadata                                                                                                                                                                                                                   |     | 92  |

|     | 5.3    | High-level view of modified FastTrack barriers                                                                                                                                                                                       |     | 93  |

|     | 5.4    | FIB analysis metadata                                                                                                                                                                                                                |     | 97  |

|     | 5.5    | FIB write barrier.                                                                                                                                                                                                                   | . 1 | 103 |

| 5.6  | FIB read barrier                                                          |

|------|---------------------------------------------------------------------------|

| 5.7  | Specializations of the Exclusive cases of local FIB barriers              |

| 5.8  | FIB request dispatch and response handling in communicating barriers 108  |

| 5.9  | FIB check-and-transfer handling                                           |

| 5.10 | FIB request processing at yield points                                    |

| 5.11 | FIB write barrier case for Shared state                                   |

| 5.12 | A missed data race due to escape-filtering must be preceded by a detected |

|      | race on escape                                                            |

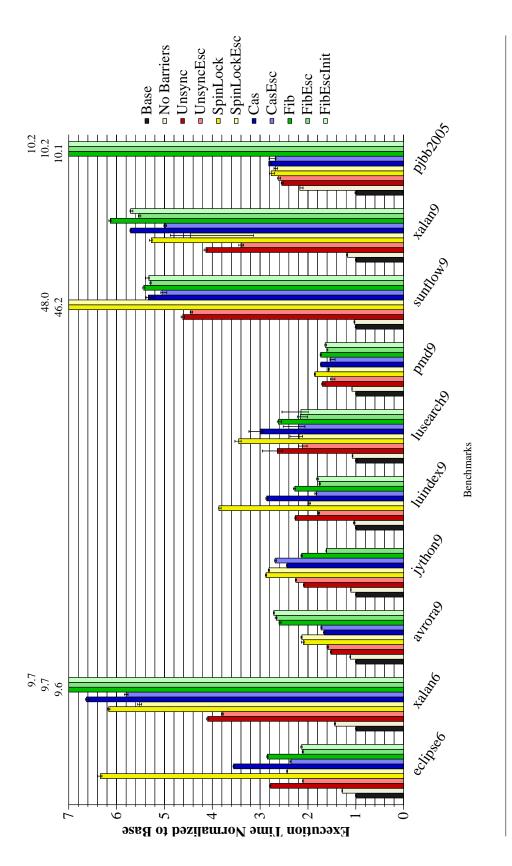

| 5.13 | Execution times of data-race detector implementations normalized to Base  |

|      | Jikes RVM                                                                 |

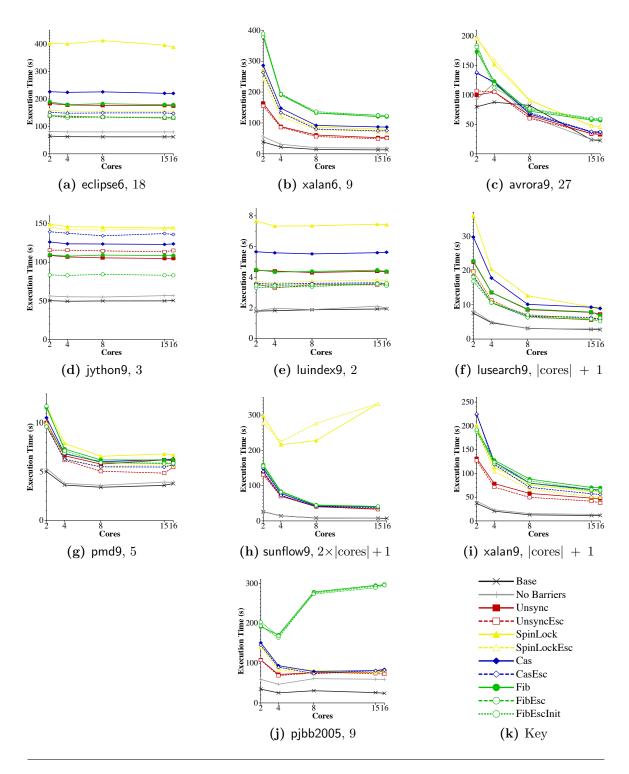

| 5.14 | Scalability of Base Jikes RVM and FastTrack implementations               |

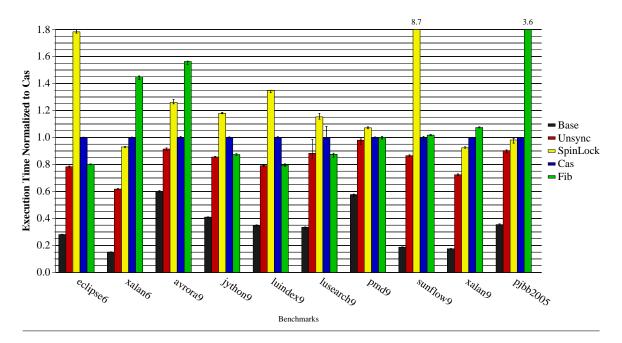

| 5.15 | Execution times of Base, Unsync, Cas, and Fib, normalized to Cas $138$    |

| 5.16 | Unsound reprivatization in TRaDe may miss true data races                 |

# List of Tables

| Table Number      |                                                                                                                                                                                         | Р | age |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|

| 3.1               | An example trace showing how RADISH metadata is updated. Empty cells indicate the value is the same as in the cell above. The local component of each core's vector clock is underlined | • | 41  |

| 4.1<br>4.2<br>4.3 | The LARD interface                                                                                                                                                                      |   | 74  |

| 5.1<br>5.2        | Summary of FIB ownership state transitions                                                                                                                                              |   |     |

# Acknowledgments<sup>1</sup>

The work described in this dissertation was undertaken with several collaborators. Joe Devietti led the RADISH project, where he and I enjoyed a 2-to-1 adviser-to-student ratio working with Karin Strauss, our advisers Luis Ceze and Dan Grossman, and Shaz Qadeer. The breadth of experience and insight represented in this group was exciting, as was publishing a paper at a computer architecture conference that referred to a companion technical report with *proofs*, sketchy as they may have been. On the LARD project, Dan and Luis offered great support, repeatedly championing an idea I worried was too obvious. On the FIB project, Dan and I have benefited from the insights and experience of collaborators Man Cao and Mike Bond, who designed and engineered OCTET, the most related prior work.

More broadly, in six years at UW CSE, I have interacted with a host of insightful individuals who made me the computer scientist I am today.

My advisers Dan Grossman and Luis Ceze brought complementary perspectives to their co-advising that helped build the signature SAMPA culture of cross-stack thinking while supporting the goals of the individual students they advised. They proved patient in their attempts to focus a student perpetually distracted by unrelated pursuits, and reacted with easygoing laughter (and occasional delight) when said student poked fun at them and the grad school experience. Dan, with his knack for the right mix of rigor, clarity, and a little humor, influenced the way I think and communicate (even if I still wave my hands a bit too often), whether for research or teaching. Luis, with his seemingly unbounded and unbridled enthusiasm, threw more inspired and zany ideas at me than I could dodge, eventually turning

<sup>&</sup>lt;sup>1</sup>The section's title is an acronym describing the peculiar genre known as dissertation acknowledgments:  $\mathbf{A}$  wkwardly cooing key names or  $\mathbf{w}(e)$  arily listing each due gratitude makes effusive notes turn sappy.

me from ignoring hardware to dabbling occasionally in computer architecture. I must also thank Dan for an ancillary benefit of his advising: His foresight in taking a couple "long walks" in his college days ensured that he and Luis were not only on board when I decided to disappear to walk for a few months, but piloted a version of the LARD paper through author response and resubmission so I could keep walking.

I also benefited from mentorship by other faculty during my time at UW. Gaetano Borriello offered mentorship and support in my steps from CSE 351 TA to instructor to faculty job applicant and beyond. At my talks at UW, Mark Oskin always asked big questions that I never quite understood, but that have later deepened my own understanding of my research. Zach Tatlock offered enthusiastic support and fresh insights on presentation, especially in hasty preparation for job talks. I somehow conned him into serving on my committee during his first year as a professor. Scott Hauck served as graduate school representative at my general exam despite the peculiar proposed completion schedule and Nick Boechler stepped in for my final exam on short notice to help solve a difficult set of schedule constraints. Hal Perkins shared candid discussions on teaching careers.

Sebastian Burckhardt, along with Daan Leijen and Manuel Fähndrich, exposed me to new perspectives, insights, and values in research, during a brief stint at Microsoft Research.

Steve Freund played a major role in my entry into computer science research and grad school. My first research project was on dynamic data-race detection with him seven years ago. (Apparently my fascination by this topic remains.) Steve's relaxed mentorship on points from academic life balance to research detail has been invaluable ever since.

Lindsay Michimoto was a source of wisdom, administrative magic, and encouragement throughout grad school. I remained blissfully ignorant of grad school finance due to Lindsay, Mel Kadenko, Julie Svendsen, Lisa Merlin, Joel Cohn, Jan Harrison, and others, while enjoying the support of a departmental Anne Dinning and Michael Wolfe Fellowship and an ARCS Foundation Fellowship.

The students of SAMPA made collaboration a blast. Joe Devietti and I had a knack for

writing papers that took program committees at least a few tries to appreciate. Maybe this is because we consistently omitted our best ideas, like representing 9 states in 3 bits via an enchanting theory of half-bits, or deploying the title, DR. DISH TOWEL: Data-Race Detection In Software and Hardware That's always On With Excellent Latency. Brandon Lucia's creative enthusiasm and shared enjoyment of terrible puns kept me on my toes. Without Adrian Sampson's level-headed and insightful assistance, my first conference paper would not have happened so smoothly. I later learned a lot from Adrian's ability to deliver compelling and clear presentations. Jacob Nelson's masterful management of our group infrastructure saved me countless headaches. Discussions with Jacob and Nick Hunt revealed reassuring shared perspectives on some peculiarities of the value systems of academia. Hadi Esmaeilzadeh demonstrated that a brilliant researcher could be downright friendly. Finally, post-SAMPA-meeting afternoon diversions with Brandon, Adrian, Joe, Jacob, Tom Bergan, Emily Fortuna, Brandon Myers, and Brandon Holt made possible our finest and most impactful publications, appearing at the prestigious UW CSE Potentially Computer Science Conference, along with other shenanigans.

I enjoyed formative interactions with UW undergraduates. Cody Schroeder and Kristian Lieberg provided an enjoyable summer lesson in advising undergraduate research. Working with my CSE 351 class in summer 2013 reminded me how much I enjoy teaching.

Outside the department, Tom and Fran were consistent adventure companions, great friends, and providers of balanced perspective on the relative importance of grad school and life. Trips with Nick opened up new modes of self-powered travel in the mountains.

Finally, the constant support of my family played an enormous role in bringing me to graduate school in the first place and encouraging me to succeed on my own terms.

<sup>&</sup>lt;sup>2</sup>Technically, we have not yet established an upper bound.

#### Chapter 1

## Introduction

Software is used to solve inherently concurrent problems at all scales, from power grid control to finance and from vehicle control to medical devices. Building reliable software demands programming models and tools that support transparent reasoning and strong guarantees about the execution of programs. Shared-memory multithreading is a programming model for concurrency and parallelism that has seen heavy use in mainstream programming languages, despite suffering several pitfalls arising from the implicit sharing of memory. The rapid adoption of multicore processors in machines from servers to phones has increased the use of shared-memory multithreading while simultaneously exacerbating its problems. Threads can interact through shared memory in subtle, timing-dependent ways that lead to errors, such as data races, whose unpredictable outcomes make them difficult to find, understand, and eliminate.

Despite great strides over the past few decades in research to improve the reliability of shared-memory multithreaded programs, a number of factors have deterred solutions from reaching real-world success: problems of scale and precision have defeated some static program analysis tools; the inertia of mainstream languages or incompatibility with legacy code has slowed adoption of new programming models and language advances; high execution time overheads have discouraged the use of run-time error-detection tools. This dissertation focuses on challenges impeding widely-deployed, accurate, and automatic detection of data races in shared-memory multithreaded programs at run-time.

#### 1.1 Data races are exceptional.

A data race in a shared-memory multithreaded program is a pair of memory accesses to the same shared-memory location by different threads, where at least one of the two accesses is a write and no synchronization orders the two accesses. The accesses may execute in either order, yielding unpredictable program state. Intuitively: a read racing with a write may return the location's old or newly written value; the final value stored in a location when two writes race may be either of the newly written values. Data races notoriously result in problematic and confusing errors. The silent, unpredictable resolution of data races hurts reproducibility when testing and debugging and can play a part in other more complex shared-memory errors such as violations of atomicity or determinism. Furthermore, while the memory consistency models of modern mainstream programming languages [20, 76] guarantee that programs free of data races execute with the intuitive semantics of sequential consistency [3, 69], they make weak or no guarantees about the execution of programs with data races. Optimizations in modern compilers and multiprocessor architectures can interact with data races to result in unintuitive, program executions where in-order interleavings of the operations of multiple threads are insufficient to reason about all possible executions.

Some researchers have proposed data-race exceptions to mitigate the ill effects of data races by making every data race an explicit fail-stop error at run-time [2, 27, 46, 73, 78]: on at least one access in a pair of racing accesses, raise an exception instead of executing the access. Under this model, data races become obvious at run-time and execution never reaches a racing access nor its ill effects. Early and explicit failure is arguably more useful to programmers than silently continuing execution. Data-race exceptions thus aid debugging and promote the treatment of data races as errors that must be fixed, rather than low-priority issues to ignore until obviously problematic. Furthermore, many analyses of higher-level properties of multithreaded programs, such as determinism [94] and atomicity checking [56], rely on data-race freedom or must perform data-race detection as part of the analysis. Data-race exceptions also simplify semantics in programming languages. In a semantics where data races are the only source of sequential consistency violations, raising an exception instead of allowing a data race suffices to avoid violations of sequential consistency.

### 1.2 Problem: Accurate language-level data-race detection is slow.

Implementing data-race exceptions naturally requires accurate dynamic data-race detection. An accurate dynamic data-race detector admits an execution (or a single access within that execution) if and only if it is data-race-free; it reports a data race if and only if a data race truly occurs in that execution. Much of the data-race detection literature uses the terms sound and complete to describe the two conditions for what we term accuracy, although application of these terms in the literature differs based on the perceived purpose of a data-race detector. This dissertation takes the positive purpose to verify that executions are data-race-free, and thus admit executions if and only if they are data-race-free, analogous to a type checker whose purpose is to admit only type-safe programs. A sound dynamic data-race detector admits an execution only if it is data-race-free. A complete dynamic data-race detector admits an execution if it is data-race-free.

We use data-race detection to refer to dynamic data-race detection throughout this dissertation unless otherwise noted. We also assume synchronous (or on-the-fly) dynamic data-race detection, with data races reported immediately before one of the two racing accesses, as opposed to asynchronous or post-mortem data-race detectors which may report data races later or analyze a log to identify data-races after program execution is complete.

Implementing accurate dynamic data-race detection is challenging. Most techniques sacrifice guarantees of accuracy, potentially missing true data races or reporting false data races, or they incur heavy performance overhead. Previous hardware data-race detectors (e.g., [83, 103, 143]) are inaccurate and unsuitable for data-race exceptions. While recent advances have made significant improvements to the performance of accurate dynamic software data-race detection, data-race exception support does not yet have performance suitable for production settings. FastTrack, the state of the art algorithm for pure-software dynamic data-race detection, is accurate on high-level programs, but may cause programs to run roughly an order of magnitude slower than under native execution [52, 55]. As is,

<sup>&</sup>lt;sup>1</sup>Some other work aims to *find executions that contain data races*, where *sound* means reporting an execution only if it contains a data race and *complete* means reporting an execution if it contains a data race. We do not use these definitions.

neither hardware support nor pure-software dynamic data-race detection suffices to support accurate and fast data-race exceptions. This dissertation addresses three specific accuracy and performance problems that make data-race exceptions infeasible to date.

#### 1.2.1 Fast hardware-supported data-race detection is inaccurate.

Hardware-supported data-race detectors are attractive for being fast and general, especially when applied to support data-race exceptions. Hardware can optimize common cases of an analysis to achieve much faster performance than pure software data-race detection implementations. Furthermore, by building in data-race detection at a low level in the system implementation stack, a hardware data-race detector can be reused across many software systems. The core performance- and correctness-critical components can be designed and implemented once and reused across systems. Unfortunately, previous work on hardware data-race detectors has produced only best-effort implementations whose accuracy is limited by fixed-size hardware resources or fundamentally inaccurate detection algorithms [73, 78, 82, 83, 103, 104, 143]. While many of these hardware-supported data-race detector designs have achieved very low performance overheads, none has achieved fast and fully accurate data-race detection prior to the work described in this dissertation. Fast, hardware-supported data-race exceptions have thus remained infeasible.

#### 1.2.2 Low-level data-race detection is inaccurate on high-level languages.

Recent proposals for low-level dynamic data-race detection, including our work in Chapter 3 to address the problem of §1.2.1, have full accuracy for low-level programs and improved performance. An accurate low-level data-race detector analyzes virtual memory accesses in the instruction set architecture (ISA) and stores access history for virtual memory locations, reporting data races in this abstraction accurately. Low-level implementation allows for (1) hardware optimization of common cases and (2) reuse of fast data-race detection mechanisms by many software systems.

Naïvely, one might run a high-level language implementation like a Java virtual machine (JVM) on hardware with low-level data-race detection support to implement *language-level*

data-race exceptions in the Java program. By language-level data race, we mean a data race between accesses in the high-level language memory abstraction. Unfortunately, neither low-level data races nor language-level data races subsumes the other. Thus a low-level race detector can report false data races and miss true data races for programs written in high-level languages.

Current hardware data-race detectors are designed to reason only about ISA-level programs and their data races. They cannot reason about data races in higher-level execution abstractions when non-trivial translation is involved. The mismatch between modern sophisticated language implementations and naïve hardware data-race detectors bars a large population of high-level language programs from the benefits of fast, accurate, and general hardware-supported data-race detection.

#### 1.2.3 Software data-race detectors use costly defensive synchronization.

A dynamic data-race detector must protect its analysis metadata against data races in the analysis target. A software dynamic data-race detector stores its analysis metadata in shared memory. In general, the data-race detector may read and write metadata for memory location x as part of a barrier immediately before every program access to location x. If two program accesses to x are concurrent, even if they do not conflict (i.e., even if both accesses are reads), metadata accesses will also be concurrent. The data-race detector must avoid ill effects of potential metadata races to ensure consistent and correct analysis results.

Pessimistic enforcement of analysis metadata consistency can be quite expensive. Profiling experiments in [38] suggest that synchronization to ensure metadata consistency accounts for 20%-90% of the overhead of the FastTrack [52] data-race detector on a suite of multithreaded benchmarks. The literature has generally assumed this problematic detail away as a mere artifact of implementation and not an interesting algorithmic feature. In fact, some real data-race detector implementations make no guarantee to avoid metadata races. When using data-race detection for debugging, this is often sufficient, as metadata consistency is rarely compromised in practice. This approach clearly does not suffice for data-race exceptions, where absolute accuracy guarantees are needed, but it does suggest an opportunity to exploit

the rareness of problematic conflicts.

#### 1.3 Dissertation Goals and Contributions

The goal of this dissertation is to design and evaluate techniques that reduce the overheads of accurate and fast data-race exceptions for high-level shared-memory multithreaded languages. Towards that goal, this dissertation offers three primary contributions in three areas of dynamic data-race detection: race detection in software and hardware, low-level abstractable race detection, and fast instrumentation bias.

# 1.3.1 RADISH: Accurate and Fast Race Detection in Software and Hardware (Chapter 3)

Race Detection in Software and Hardware (RADISH) is a hybrid software-hardware data-race detector that is both accurate on ISA-level programs and fast.

**Hypothesis:** A hybrid software-hardware system can exploit the accuracy of software data-race detectors and the performance of hardware support to build a hybrid data-race detector that is both accurate and fast. The flexible bounds of software implementation can maintain accuracy in all cases of analysis, while hardware support can reduce or eliminate latency for common cases.

#### Contributions

- We present the design of RADISH, a hybrid software-hardware data-race detector that

retains the full accuracy of a software data-race detector while optimizing its common

cases with fast hardware support. RADISH is the first hardware-supported data-race

detector that is fully accurate on ISA-level programs.

- We show the accuracy of RADISH by its equivalence to a canonical vector-clock data-race detection algorithm.

#### 1.3.2 LARD: Low-level Abstractable Race Detection (Chapter 4)

Low-level Abstractable Race Detection (LARD) virtualizes low-level dynamic data-race detection support to detect language-level data races in high-level programming languages.

**Hypothesis:** Hardware or other low-level implementations can enable fast and general support for accurate language-level data-race detection in high-level languages, yet current low-level solutions are accurate for ISA-level programs at best, and inaccurate for programs written in high-level languages.

#### **Contributions:**

- We present the first full explanation of how translation of a program from a high-level language to a low-level machine abstraction affects the primitives involved in the definition of a data race, and why low-level data-race detectors are incorrect for high-level programs as a result. We synthesize various issues encountered in earlier data-race detector implementations as well as issues not previously considered.

- We design low-level abstractable race detection (LARD), a simple interface for low-level data-race detectors and language implementations that virtualizes accurate low-level data-race detectors, allowing the construction of an accurate language-level data-race detector using a low-level data-race detector. We compare our approach to earlier systems that have addressed individual issues with low-level data-race detection.

- We implement our approach for Java, coupling a simulated hardware-supported ISA-level dynamic data-race detector and a modified Jikes RVM [8] Java virtual machine through a version of the x86 ISA extended with LARD primitives.

- We evaluate our implementation's accuracy, comparing against FastTrack [52], a naïve low-level data-race detector similar to our RADISH hybrid software-hardware data-race detector [38], and various partial implementations of LARD. We find that, in practice, naïve ISA-level data-race detectors suffer from false and missed data-races for Java programs, but LARD does not.

We present cursory evaluation of our implementation's performance via simulation and

via execution of the software component alone on real conventional hardware, finding

that hardware support for language-level data-race detection is likely to provide good

performance, similar to the performance of hardware-supported accurate ISA-level

data-race detection.

# 1.3.3 FIB: Fast Instrumentation Bias for Pure-Software Data-Race Detection (Chapter 5)

Fast Instrumentation Bias (FIB) aims to reduce the cost of data-race checks in pure-software dynamic data-race detectors by using cooperative synchronization to protect metadata.

**Hypothesis:** Performance overheads of pure-software accurate dynamic data-race detection can be reduced by replacing pessimistic metadata synchronization with *instrumentation bias*, a form of cooperative metadata synchronization based on thread ownership information already implicitly encoded by data-race detection metadata.

#### Contributions:

- We present Fast Instrumentation Bias (FIB), an algorithm for accurate data-race detection that avoids harmful metadata races with no synchronization in common cases, at the cost of expensive synchronization in rare cases.

- We apply conservative dynamic thread-escape analysis as a pre-filter for data-race detection and show how it maintains accuracy.

- We implement Fib for Java programs in the Jikes RVM [8] Java virtual machine.

- We evaluate the overall performance of multithreaded Java applications on our prototype implementation as well as unsynchronized and pessimistically synchronized implementations of FastTrack [52], finding that FIB is 13-21% faster than the fastest conventionally synchronized implementation on 4 benchmarks, 0-7% slower on three benchmarks, and 45-260% slower on three benchmarks. We profile the distribution of

intended common and rare cases in practice, finding that poor performance in FiB is linked to relatively high rates of FiB's expensive slow paths.

We discuss limitations of Fib as described in this dissertation, and propose future improvements.

#### 1.4 Publication and Collaboration

Chapter 3 covers the design and accuracy of the RADISH data-race detector, published in the proceedings of the 39th International Symposium on Computer Architecture [38] with an accompanying technical report [39]. Joe Devietti led the RADISH project, in collaboration with this author, Karin Strauss, Luis Ceze, and Dan Grossman. Joe is responsible for a majority of the design and the full evaluation in [38]. Chapter 3 focuses on the accuracy guarantees of RADISH's optimizations, where the author's contributions were focused, and reproduces enough of the design of RADISH from [38] to support this discussion. System detail, simulation, and evaluation are covered in [38]. The correctness discussion in this chapter supersedes previously published versions.

Chapter 4 was published in the proceedings of the 19th International Conference on Architectural Support for Programming Languages and Operating Systems [137]. The LARD project was led by the author, in collaboration with Dan Grossman and Luis Ceze. This dissertation makes minor changes to the original paper to consolidate some background and related work.

Chapter 5 covers unpublished work led by the author in collaboration with Man Cao, Mike Bond, and Dan Grossman. We plan to extend and publish this work in a future paper to supersede this presentation. Implementation of the base dynamic thread-escape analysis used in §5.4.1 and some related insights are due to Man and Mike. Specifically, the author's original proposal for accurately filtering data-race checks to non-escaped objects required the current epoch to be recorded as the last read and last write for all access histories in an object when that object is about to escape, which is sound and complete under the first-race guarantee. Man and Mike observed that it is also sound under the first-race guarantee to make no updates to an access history upon escape, as described in §5.4.1.1.

#### Chapter 2

## Foundations and Related Work

In this chapter, we first present foundations of data races (§2.1) and techniques for accurate dynamic data race detection (§2.2). Then, we discuss other approaches to data-race detection that are not suited for data-race exceptions because they may report false data races (§2.3), miss true data races (§2.4), or both (§2.5), as well other issues in data-race detection. We briefly survey static techniques for data-race detection (§2.6). Previous work related specifically to RADISH, LARD, and FIB is presented in §3.4, §4.5, and §5.7, respectively.

#### 2.1 Data Races

We consider program execution traces (T) expressed as sequences of operations (a,b) of threads (t,u), using syntax shown in Figure 2.1. Reads  $(\operatorname{rd}(t,x,v))$  and writes  $(\operatorname{wr}(t,x,v))$  by a thread, t, load and store values, v, in memory locations, x. Synchronization operations, include thread t forking a new thread u (fork(t,u)), thread t joining an existing thread u by blocking until thread u's final operation has completed  $(\operatorname{join}(t,u))$ , and thread t acquiring  $(\operatorname{acq}(t,l))$  or releasing  $(\operatorname{rel}(t,l))$  a lock. We omit the standard formal semantics of the execution of traces and additional types of synchronization. Previous work [46, 52] covers these omissions using similar syntax.

<sup>&</sup>lt;sup>1</sup>We assume sequential consistency. Although this breaks down in the presence of a data race, it does so only after the first race [5]. We discuss sequential consistency in §2.1.2, data-race detectors focused on sequential consistency violations in §2.4.1, and the first-race guarantee in §2.2.3.

```

Memory Location x Lock m Thread ID t,u Value v Operation a,b ::= \mathsf{wr}(t,x,v) \mid \mathsf{rd}(t,x,v) \mid \mathsf{acq}(t,l) \mid \mathsf{rel}(t,l) \mid \mathsf{fork}(t,u) \mid \mathsf{join}(t,u) Trace T ::= \cdot \mid T,a

```

Figure 2.1: Syntax of execution traces

## 2.1.1 The Happens-Before Relation and Data Races

The happens-before relation  $(\stackrel{hb}{\longrightarrow}_T)$  is a strict partial order over operations in trace T, composed of the transitive closure over program order  $(\stackrel{po}{\longrightarrow}_T)$ , the order of operations within each thread in the, and synchronization order  $(\stackrel{so}{\longrightarrow}_T)$ , the ordering between synchronization operations in different threads [68]. Program order is straightforward: if operation a of thread t precedes operation b of thread t in trace T, then  $a \stackrel{po}{\longrightarrow}_T b$ . Synchronization order is defined as follows:

- If thread t forks thread u at operation a in T and operation b is the first operation of thread u in T, then  $a \xrightarrow{so}_T b$ .<sup>2</sup>

- If operation a is the last operation of thread u in T and thread t joins thread u at operation b later in T, then  $a \xrightarrow{so}_T b$ .

- If thread t releases lock l at operation a in T and thread u acquires lock l at operation b later in T, then  $a \xrightarrow{so}_T b$ .

A data race is a pair of concurrent, conflicting memory accesses [91]. Two distinct operations a and b are concurrent in trace T if and only if they are not ordered by the happens-before relation (neither  $a \xrightarrow{hb}_T b$  nor  $b \xrightarrow{hb}_T a$ ). Two accesses conflict if they access the same

<sup>&</sup>lt;sup>2</sup>We assume b follows a in T. The execution semantics of traces get stuck at operation b if it does not follow operation a in T.

location and at least one of the accesses is a write. More detailed characterizations of data races may be found in [88, 91].

#### 2.1.2 Data Races and Higher-Level Properties of Program Executions

Data races are a fundamental type of error in shared-memory multithreaded programs. Data races are closely linked to several other properties of such programs. Relaxed memory consistency models for programming languages [20, 21, 76] and hardware [3–5] generally guarantee sequential consistency [69] given data-race-freedom, but in executions with data races, a weaker (or undefined) semantics applies. Thus programmers cannot reason about data races in terms of simple in-order interleavings of the operations of threads in general. Data races and data-race-freedom also factor in other higher-level properties (and their analyses) such as atomicity (e.g., [56, 119]) and determinism (e.g., [11, 37, 94]).

### 2.2 Accurate Dynamic Data-Race Detection

All accurate data-race detectors track the happens-before relation to check if pairs of conflicting accesses are concurrent, and thus racing.

#### 2.2.1 Vector Clocks

This dissertation considers data-race detectors derived from a canonical algorithm using vector clocks [49, 80] to track the happens-before order induced by synchronization and recording a history of accesses to each location to determine if a current access is concurrent with any previous conflicting accesses. We present the base algorithm (formalized in more detail in [10]), followed by discussion of many variants in the literature.

A vector clock, v, contains an integer logical clock, c, for each thread, indexed by thread. Vector clocks represent frontiers in logical time. Under the formulation of the happens-before relation as a directed acyclic graph, vector clocks summarize information about a vertex representing an operation by a thread and this vertex's most recent predecessors from each other thread.

Figure 2.2 shows the canonical vector-clock data-race detection algorithm as a judgment

```

\begin{array}{ccccc} \text{Clock} & c & \in & \mathbb{N} \\ \text{Vector Clock} & \text{v} & ::= & \cdot \mid \text{v}, t \mapsto c \\ \text{Thread VCs} & C & ::= & \cdot \mid C, t \mapsto \text{v} \\ \text{Lock VCs} & L & ::= & \cdot \mid L, m \mapsto \text{v} \\ \text{Last Reads} & R & ::= & \cdot \mid R, x \mapsto \text{v} \\ \text{Last Writes} & W & ::= & \cdot \mid W, x \mapsto \text{v} \\ \text{Detector State} & (C; L; R; W) \end{array}

```

Figure 2.2: Vector-clock data-race detector metadata

$(C; L; R; W) \stackrel{a}{\Longrightarrow}_{\mathsf{VC}} (C'; L'; R'; W')$  on the data-race detector state, shown in Figure 2.2, and a program operation. Program and heap constraints are imposed by an external judgment (not shown here) that uses this judgment for data-race detection over traces. Stuck-ness indicates a data race. We describe synchronization tracking in §2.2.1.1 and access tracking and checking in §2.2.1.2.

#### 2.2.1.1 Synchronization tracking

To track the happens-before order, the vector-clock data-race detector maintains:

- a vector clock,  $C_t$ , for each thread t, representing the last logical time in each thread that happens before the current logical time in this thread. The tth entry in thread t's vector clock is its *local time*:  $C_t(t)$ .

- a vector clock,  $L_l$ , for each lock l, representing the last logical time in each thread that happens before the last release of the lock l.

The main thread's vector clock starts with a local time of 1 and all other vector clocks initially hold exclusively zero entries:  $C_t(t) = 1 \land \forall u \neq t, C_t(u) = 0$ . Vector clocks are updated on the execution of synchronization operations in a program trace as follows:

• VC FORK: When thread t forks thread u, thread u's vector clock is initialized with a copy of thread t's current vector clock. Afterwards, both threads' local clocks are incremented.

$$(C; L; R; W) \stackrel{a}{\Longrightarrow}_{\mathsf{VC}} (C'; L'; R'; W')$$

#### Synchronization tracking:

VC FORK

$$v = C_t, t \mapsto C_t(t) + 1 \qquad v' = C_t, u \mapsto 1$$

$$(C; L; R; W) \xrightarrow{\text{fork}(t,u)} \bigvee_{\text{VC}} (C, t \mapsto v, u \mapsto v'; L; R; W)$$

$$v = C_t \sqcup C_u$$

$$(C; L; R; W) \xrightarrow{\text{join}(t,u)} \bigvee_{\text{VC}} (C, t \mapsto v; L; R; W)$$

$$v = C_t \sqcup C_u$$

$$(C; L; R; W) \xrightarrow{\text{join}(t,u)} \bigvee_{\text{VC}} (C, t \mapsto v; L; R; W)$$

$$v = C_t \sqcup L_m$$

$$(C; L; R; W) \xrightarrow{\text{rel}(t,l)} \bigvee_{\text{VC}} (C, t \mapsto v; L, m \mapsto v'; R; W)$$

$$v = C_t \sqcup L_m$$

$$(C; L; R; W) \xrightarrow{\text{acq}(t,l)} \bigvee_{\text{VC}} (C, t \mapsto v; L; R; W)$$

#### Access checking:

$$\frac{W_x \sqsubseteq C_t \quad \mathbf{v} = R_x, t \mapsto C_t(t)}{(C; L; R; W) \xrightarrow{\mathsf{rd}(t, x, v)} \mathsf{VC} (C; L; R, x \mapsto \mathbf{v}; W)}$$

$$\frac{\mathsf{VC} \text{ WRITE}}{W_x \sqsubseteq C_t} \quad R_x \sqsubseteq C_t \quad \mathbf{v} = W_x, t \mapsto C_t(t)}{(C; L; R; W) \xrightarrow{\mathsf{wr}(t, x, v)} \mathsf{VC} (C; L; R; W, x \mapsto \mathbf{v})}$$

Figure 2.3: Vector-clock data-race detector

This represents the fact that the fork operation, and all operations that happen before it, happen before all operations in thread u, but later operations of the two threads are concurrent with each other unless more synchronization is performed.

• VC JOIN: When thread t joins on thread u, thread t's vector clock is updated to be the entry-wise maximum ( $\sqcup$ ) of the current vector clocks of threads t and u.

This represents the fact that all operations in thread u happen before all operations in thread t at and after the join.

• VC RELEASE: When thread t releases lock l, lock l's vector clock is updated to the entry-wise maximum of the vector clocks of thread t and lock l. (Note this maximum is always equivalent to thread t's vector clock, since lock l's vector clock was merged into thread t's vector clock on the preceding acquire, and no other thread may have released the lock since.)

This represents the fact that all operations that happen before the thread t's release of lock l will also happen before any later acquisitions of lock l.

VC ACQUIRE: When thread t acquires lock l, thread t's vector clock is updated to be

the pairwise maximum of the current vector clocks of thread t and lock l.

This represents the fact that all operations that happen before the last release of lock l also happen before thread t's acquisition of the lock and all of thread t's later operations.

Other types of synchronization are handled similarly. Outgoing synchronization (e.g., lock release) merges from the performing thread's vector clock into some other vector clock, representing the source of some happens-before edge that may later be completed when a thread performs incoming synchronization on the same target (analogous to a message sent in Lamport's formalism [68]), and then advances the thread's local time to show that later operations did not happen before this outgoing synchronization. Incoming synchronization (e.g., lock acquire) merges some other vector clock into the performing thread's vector clock,

representing the destination of a happens-before edge (analogous to a message received in Lamport's formalism).

#### 2.2.1.2 Access tracking and checking

For each memory location, an *access history* records the logical times of accesses to that location. The logical time of each subsequent access is checked against these previous accesses to determine whether they are conflicting and concurrent, thus racing. More specifically, for a location, x, the access history records:

- a set of last reads,  $R_x$ , encoded as a vector clock, where each thread's entry records the local time of that thread's last read access to the associated location.

- a set of *last writes*,  $W_x$ , encoded as a vector clock, where each thread's entry records the local time of that thread's last write access to the associated location.

Initially, all last writes and reads are set to 0. When a memory access is executed, it is first checked against the access history. If it does not race with previous accesses, it is recorded. The check and access history update for an access are assumed to happen atomically with the access itself. The checks are as follows:

- VC READ: On a read access, rd(t, x, v), to x by thread t, for any thread  $u \neq t$ , if thread t has not synchronized with thread u since thread u's last write to x ( $W_x(u) > C_t(u)$ ) then this access races with thread u's last write to x. We express this in Figure 2.3 with the element-wise vector-clock happens-before operator  $\sqsubseteq$ . If no race is detected, then replace thread t's last read for x with thread t's current local time and allow the access.

- VC WRITE: On a write access,  $\operatorname{wr}(t, x, v)$ , to x by thread t, perform the same check as for the read case. Additionally, for any thread  $u \neq t$ , if thread t has not synchronized with thread u since thread u's last read of x ( $R_x(u) > C_t(u)$ ) then this access races with thread u's last read of x. We express these checks in Figure 2.3 with the element-wise vector-clock happens-before operator  $\sqsubseteq$ . If no race is detected, then replace thread t's last write for x with thread t's current local time and allow the access.

#### 2.2.1.3 Variants

Similar algorithms have appeared in much work on data-race (or *access-anomaly*) detection [40, 41, 63, 93, 101, 111, 116].

An important optimization of the vector-clock algorithm for data-race detection is to store information about only a *single* last write instead of a vector clock recording information about the last write from each thread [40]. Write accesses to a location must be totally ordered by the happens-before relation in data-race-free executions, thus the set of last writes encoded by the vector clock is redundant. By exploiting the guarantee that accuracy survives until the first data race (or the assumption that an access that races with previous accesses is never recorded in an access history), it is safe to store only the globally most recent write (§2.2.3). Since the single recorded last write therefore must happen after all previous writes to be recorded, an access that happens after this last write also transitively happens after these previous writes. This optimization lowers the space requirements for last-writes storage from linear in the number of threads to constant, for a single last write. It also reduces the cost of a checks for read accesses from linear in the number of threads to constant, since read checks compare against only a single last write. The complexity of checks for writes remains linear in the number of threads due to the last reads vector clock, but reads are more common than writes.

TRaDe [33] optimizes the vector-clock data-race detection algorithm with accordion clocks [35], an alternative vector clock representation that elides unused entries. Our RADISH data-race detector, described in Chapter 3 and in [38], is an optimized hybrid software-hardware implementation of the vector-clock algorithm. FastTrack [52] also optimizes the vector-clock algorithm. It employs the single last-write optimization and a similar optimization that allows storage of a single last read in the common case when reads to a location by different threads happens-before ordered. Although such ordering is not guaranteed, it occurs, for example, whenever there exists a lock l that is always held when accessing a memory location x. The use of such locking disciplines is common in practice. Storing a single last read instead of a vector clock of last reads when possible saves space and allows write checks to execute in constant time in the common case and time linear in

the number of threads in the rare case. We discuss FastTrack further in §5.2.

## 2.2.2 Alternative Happens-Before Representations

Goldilocks [46] is an accurate dynamic data-race detector that uses an extended lockset<sup>3</sup> for each memory location. After an access, this set initially holds the thread responsible for that access. When a thread in the set performs outgoing synchronization on some target (e.g., releases a lock), that target is added to the set. When a thread performs incoming synchronization on a target in the set (e.g., acquires a lock in the set), that thread is added to the set. A thread is allowed to access the location if that thread is in the location's set. Goldilocks keeps separate sets for reads and writes, analogous to the last reads and last writes in the canonical algorithm above. These extended locksets encode the subset of the happens-before relation that is descended from the last access to the memory location they track—in other words, the nodes in the happens-before graph that are reachable from the last access. To support this analysis, which potentially requires updating all sets on every synchronization operation, the Goldilocks implementation does lazy processing of synchronization operations, maintaining a history of synchronization operations and only forcing the update of the set for a location upon a new access to that location.

### 2.2.3 First-Race Accuracy

The accurate algorithms for dynamic data-race detection described above are technically accurate for a given memory location only through the first data race on that location or the first race in the execution, a consideration discussed starting with earlier work on dynamic data-race detection and throughout the literature [10, 32, 52, 82, 90, 91].

The first-race rule is necessitated by the fact that none of these algorithms stores the complete history of accesses. Instead, they store a set of accesses with the invariant that all earlier accesses not in the set happen before at least one of the accesses in the set.<sup>4</sup>

<sup>&</sup>lt;sup>3</sup>The meaning of Goldilocks' locksets is different than that of those in the lockset algorithm for data-race detection, discussed in §2.3.1.

<sup>&</sup>lt;sup>4</sup>The actual invariant is stronger, as is its use: all earlier writes not represented in the write set happen before all writes represented in the write set and all reads represented in the read set; all earlier reads not represented in the read set happen before at least one read represented in the read set and are not

Thus by the transitivity of happens-before, if all accesses in the set happen before some new access, then all earlier accesses happen before the new access. Real implementations, like the algorithms above, bound the size of the set based on the number threads (or a constant: 1). On data-race-free accesses, replacing an old access in the set with a new access that dominates it is safe: the invariant is maintained. However, replacing an access in the set with a racing access can break that invariant. Even though this first race has been reported, later racing accesses may appear to be data-race-free under the assumption that the invariant holds. An alternative for racing accesses is to report the race and let execution continue, but do not store the racing access. This clearly breaks the invariant as well, as the access is never recorded and future accesses that race with it will appear not to race. However, if the racing access is neither executed nor recorded, as with data-race exceptions, the invariant is maintained.

There are a few reasons why the first-race rule—and an even weaker guarantee to catch only the first race in the entire execution (not the first race per location in the execution)—is acceptable. For example, later data races may occur as a result of earlier data races. General dynamic data-race detection, the problem of finding all data races in an execution that are feasible independent of other data races in the execution, has been shown to be NP-hard [88, 91]. Choi and Min built a system to detect race frontiers, the first race in each process, in the context of reproducing data races [32]. In most relaxed memory models, the first race in an execution indicates the first possible end to the sequentially consistent execution prefix; reasoning beyond the first data race also requires consideration of non-sequentially consistent traces, not supported by most data-race detectors [5]. This is the foundation for a variation on data-race exceptions that raises an exception on all data races that violate sequential consistency (and potentially on more data races), but not necessarily on all data races [73, 78].

Most importantly for this dissertation, data-race exceptions make the first-race distinction moot: racing accesses are never actually executed, so there is never a first race or the accompanying compromise of accuracy, only races that would have been and accurate reports thereof. In fact, the first data race exception in each thread should correspond to Choi and Min's race frontiers [32].

### 2.2.4 Data-Race Exceptions

Data-race exceptions prevent data races and their effects from occurring by guaranteeing to raise an exception immediately before (*i.e.*, instead of) at least one of the two accesses in a data race. Typically, we think of raising an exception on exactly the second in time of the two accesses. However, allowing the exception to be raised on either or both of the accesses affords greater implementation flexibility and does not necessarily force serialization of concurrent accesses for analysis. Additional relaxations of the timing of exception delivery may offer more implementation alternatives. Regardless, we assume precise exception delivery.

Elmas, et al. [46], were the first to propose data-race exceptions and their benefits for mitigating the ill effects of data races. Other researchers have proposed or supported this idea and variants thereof [2, 27, 73, 78]. Specifically, exceptions for the subset of data races that induce sequential consistency violations are sufficient to simplify the memory consistency model in a way that avoids reasoning about non-sequentially consistent executions [73, 78]. A memory model with accurate data-race exceptions is stronger than the Java and C/C++ memory models, guaranteeing data-race freedom, or an exception, on each memory access. Data-race freedom still guarantees sequential consistency, and data-race-free programs never generate data-race exceptions. Full data-race exceptions provide this benefit, along with additional debugging benefits and support for other analyses that depend on data-race detection as a sub-analysis (e.g., [56]) or require data-race freedom (e.g., [94]). We have previously examined potential uses of recoverable data-race exceptions in designing new algorithms for synchronization or run-time systems [136].

#### 2.2.5 Performance

Dynamic data-race detectors developed in industry have integrated lockset (§2.3.1) and happens-before algorithms, although they are generally heavyweight, running tens or hundreds of times slower than normal execution without data-race detection [61, 62, 84, 117, 125].

We do not discuss performance of inaccurate data-race detectors in depth as they are not suitable for our needs. Accurate data-race detectors have long had heavy performance overhead, but recent innovations have driven it down. Nonetheless, performance remains infeasible for always-on deployment.

The original Goldilocks implementation reports normalized run-times of 1-18× those of native execution, with most benchmarks under 5 or  $6\times$  in an interpreting JVM [46]. Using static data-race detection to elide checks helps reduce the overheads further. Results from [52] largely corroborate these results for the same implementation, but show that this implementation does have pathologically bad performance on some additional benchmarks (likely due to accommodations for its lazy updates of access histories). Slowdowns for an implementation of Goldilocks in the RoadRunner [54] dynamic analysis framework (via bytecode instrumentation on a JIT-compiling JVM) range from a few times to  $77\times$  [52]. An implementation of the DJIT+ algorithm [63] (an optimization of the vector-clock algorithm described in §2.2.1) in the same framework averages overheads of  $20\times$ , and FastTrack averages  $8.5\times$  [52]. Newer results for FastTrack show overheads averaging  $7.5\times$  alone and  $5.7\times$  after removal of redundant checks with RedCard [55].