© Copyright 2012

Joseph Devietti

Deterministic Execution for Arbitrary Multithreaded Programs

Joseph Devietti

A dissertation

submitted in partial fulfillment of the

requirements for the degree of

Doctor of Philosophy

University of Washington

2012

Reading Committee:

Luis Ceze, Chair

Daniel Grossman

Henry Levy

Program Authorized to Offer Degree:

Department of Computer Science and Engineering

University of Washington

### Abstract

Deterministic Execution for Arbitrary Multithreaded Programs

Joseph Devietti

Chair of the Supervisory Committee: Associate Professor Luis Ceze Computer Science and Engineering

Nondeterminism is one of the main reasons that parallel programming is so difficult. Bugs can vanish when programs are rerun or run under a debugger, thwarting attempts at their removal. Stress-testing is a common practice to flush out rare defects though it consumes extensive processing power and offers no real guarantees of discovering bugs. Deployment can similarly expose new issues that are difficult to reproduce. Finally, nondeterminism frustrates replicating multithreaded programs for fault-tolerance or performance as the replicas can diverge silently. Determinism eliminates these problems, making debugging and replication possible and making testing more valuable and efficient.

Previous efforts at providing determinism required programs to be (re-)written in restrictive languages. In contrast to these language-level determinism schemes, this dissertation shows how execution-level determinism can be provided for arbitrary parallel programs, even programs that contain concurrency errors. First, we employ a hardware-based approach to provide determinism for unmodified binaries running on a deterministic multiprocessor system. Second, we show that memory consistency relaxations both enable a pure software-based implementation of executionlevel determinism for arbitrary programs and also admit a simpler deterministic multiprocessor design. Finally, we describe a hybrid mechanism that integrates execution-level and language-level determinism techniques to provide determinism for arbitrary programs with higher performance than an execution-level approach alone.

| List of Figures                                                    | v   |

|--------------------------------------------------------------------|-----|

| List of Tables                                                     | vii |

| Chapter 1 Introduction                                             | 1   |

| 1.1 The Challenges of Parallelism                                  | 2   |

| 1.2 The Benefits of Reproducibility and Determinism                |     |

| 1.3 Previous Work on Deterministic Parallelism                     | 5   |

| 1.4 Dissertation Goals and Contributions                           | 6   |

| 1.4.1 DMP: A Deterministic MultiProcessor                          | 7   |

| 1.4.2 RCDC: A Relaxed Consistency Deterministic Computer           | 7   |

| 1.4.3 MELD: Merging Execution-level and Language-level Determinism |     |

| 1.5 Reading Guide                                                  | 10  |

| Chapter 2 Related Work                                             | 11  |

| 2.1 Concurrency Bug Detection and Survival                         | 11  |

| 2.1.1 Data Races                                                   | 12  |

| 2.1.2 Atomicity Violations                                         | 15  |

| 2.1.3 General Concurrency Bug Detection                            | 17  |

| 2.1.4 Simplifying Memory Consistency Models                        |     |

| 2.2 Programming Models for Parallelism                             | 21  |

| 2.2.1 Task Parallel Frameworks                                     | 21  |

| 2.2.2 Transactional Memory                                         | 23  |

| 2.3 Thread-level Speculation                                       | 24  |

| 2.4 Multithreaded Record and Replay                                | 25  |

| 2.4.1 Hardware Record and Replay                                   | 25  |

| 2.4.2 Software Record and Replay Techniques                        |     |

| 2.5 Deterministic Parallelism                                      | 29  |

| 2.5.1 Determinism Verification                                     | 29  |

| 2.5.2 Deterministic Parallel Languages                             | 30  |

| 2.5.3 Execution-level Determinism Systems                          | 31  |

| Chapter 3 A Deterministic MultiProcessor Architecture              | 35  |

# TABLE OF CONTENTS

| 3.1 Enforcing Deterministic Shared Memory Multiprocessing                         | 36 |

|-----------------------------------------------------------------------------------|----|

| 3.1.1 Basic Idea – Det-Serial                                                     | 36 |

| 3.1.2 Handling Application-Level Synchronization                                  | 37 |

| 3.1.3 Recovering Parallelism                                                      | 37 |

| 3.1.4 Exploiting the Critical Path – QB-SYNCFOLLOW, QB-SHARING and QB-SYNCSHARING | 41 |

| 3.2 Implementation Issues                                                         | 43 |

| 3.2.1 Hardware-Only Implementation                                                | 43 |

| 3.2.2 Software-Only Implementation                                                | 45 |

| 3.2.3 Leveraging Commercial Hardware Transactional Memory                         | 46 |

| 3.3 Experimental Setup                                                            | 47 |

| 3.3.1 Hardware Implementation                                                     | 48 |

| 3.3.2 Software Implementation                                                     | 48 |

| 3.4 Evaluation                                                                    | 49 |

| 3.4.1 Performance and Scalability                                                 | 49 |

| 3.4.2 Sensitivity Analysis                                                        | 50 |

| 3.4.3 Characterization                                                            | 52 |

| 3.4.4 CoreDet: Performance and Scalability                                        | 53 |

| 3.5 Discussion                                                                    | 53 |

| 3.6 Conclusions                                                                   | 56 |

| Chapter 4 Trading Strong Memory Consistency for Simpler Determinism               | 58 |

| 4.1 Relaxed-Consistency Deterministic Execution                                   | 59 |

| 4.1.1 DET-TSO: Store Buffering                                                    | 59 |

| 4.1.2 DET-HB: Leveraging Data-Race-Free Memory Models                             | 60 |

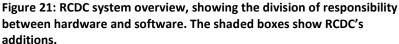

| 4.2 RCDC System Overview                                                          | 64 |

| 4.3 Implementation                                                                | 66 |

| 4.3.1 Quantum Formation                                                           | 66 |

| 4.3.2 Buffering                                                                   | 67 |

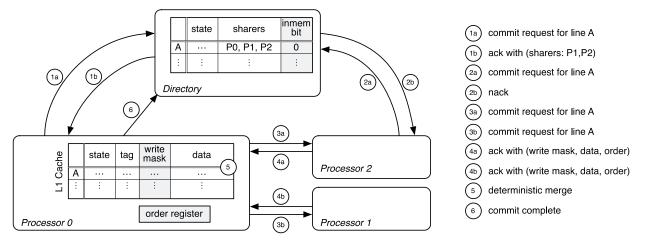

| 4.3.3 Committing Buffered Data                                                    | 69 |

| 4.3.4 Synchronization Library                                                     | 74 |

| 4.4 System Issues                                                                 | 75 |

| 4.4.1 Support for nondeterministic execution                                      | 76 |

| 4.4.2 Processes                                                                   | 76 |

| 4.4.3 Context Switches                                                            | 76 |

| 4.4.4 Paging                                                               | 77  |

|----------------------------------------------------------------------------|-----|

| 4.4.5 Memory Errors                                                        | 77  |

| 4.4.6 Store Buffer Parameters and Determinism                              | 77  |

| 4.5 Evaluation                                                             | 78  |

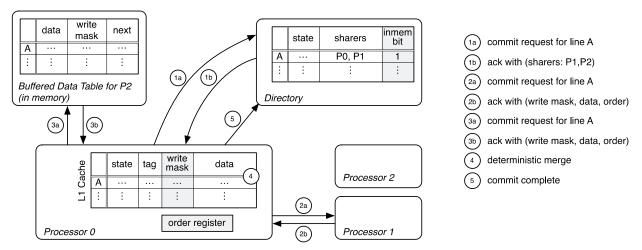

| 4.5.1 Performance and Scalability                                          | 79  |

| 4.5.2 Characterization                                                     | 80  |

| 4.5.3 Sensitivity to Quantum Size                                          | 81  |

| 4.5.4 Compiler-Runtime Implementation                                      | 81  |

| 4.6 Conclusions                                                            | 82  |

| Chapter 5 Merging Execution-level and Language-level Determinism           | 83  |

| 5.1 Pitfalls of Integrating Execution-Level and Language-Level Determinism | 83  |

| 5.2 Background                                                             | 84  |

| 5.3 Combining Execution-level and Language-Level Determinism               | 87  |

| 5.3.1 Starting Simple: Pure Language-Level Determinism                     | 87  |

| 5.3.2 Supporting Concurrent Conflicting Tasks                              |     |

| 5.3.3 Supporting Arbitrary Parallelism Constructs                          | 89  |

| 5.3.4 Supporting Casts and Modularity                                      | 90  |

| 5.4 The MELD Type System                                                   | 95  |

| 5.4.1 Type Qualifiers                                                      | 95  |

| 5.4.2 Defaults                                                             | 96  |

| 5.4.3 Type Rules                                                           | 97  |

| 5.5 Implementation                                                         | 97  |

| 5.5.1 Type Qualifier System                                                | 98  |

| 5.5.2 DPJ Compiler                                                         | 98  |

| 5.5.3 MELD Compiler and Runtime System                                     | 98  |

| 5.5.4 Handling thread fork/join                                            | 99  |

| 5.6 Extensions                                                             | 100 |

| 5.6.1 Incorporating Nondeterminism                                         | 100 |

| 5.6.2 Qualifier Polymorphism                                               | 101 |

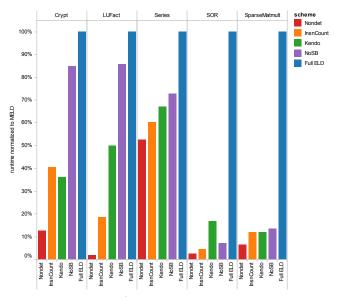

| 5.7 Limit Study                                                            | 101 |

| 5.7.1 Experimental Setup                                                   | 102 |

| 5.7.2 Results                                                              | 102 |

| 5.8 Conclusions                                                            |     |

| Chapter 6 Conclusions     | 105 |

|---------------------------|-----|

| 6.1 Summary of Techniques |     |

| 6.2 Limitations           |     |

| 6.3 Looking Forward       |     |

| References                |     |

## LIST OF FIGURES

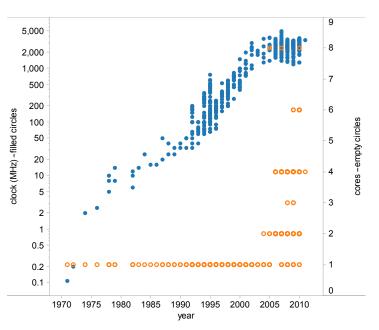

| Figure 1: CPU frequency and core count of desktop/server microprocessors from 1971-2011       | 1  |

|-----------------------------------------------------------------------------------------------|----|

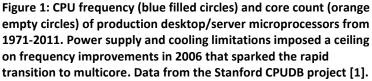

| Figure 2: The value of reproducibility throughout the software development cycle              | 3  |

| Figure 3: Our basic approach to determinism                                                   | 6  |

| Figure 4: The overlapping definitions of different classes of concurrency errors              | 11 |

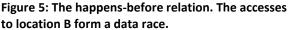

| Figure 5: The happens-before relation                                                         | 12 |

| Figure 6: An assembly code example of a single-variable atomicity violation                   | 15 |

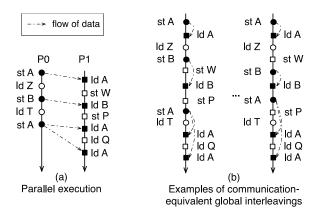

| Figure 7: A parallel execution and two of its multiple communication-equivalent interleavings | 35 |

| Figure 8: Deterministic serialization of memory operations                                    | 36 |

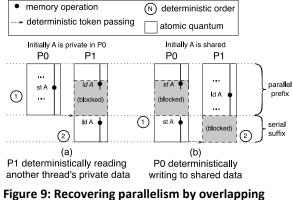

| Figure 9: Recovering parallelism by overlapping communication-free execution                  | 38 |

| Figure 10: Deterministic serialization of shared memory communication only                    | 39 |

| Figure 11: Recovering parallelism by executing quanta as memory transactions                  | 40 |

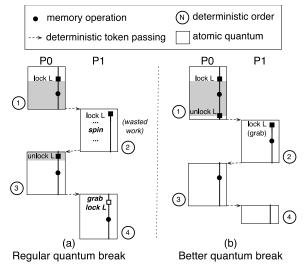

| Figure 12: When better quantum breaking policies lead to better performance                   | 42 |

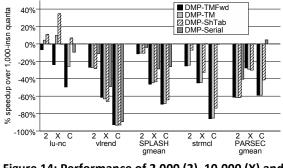

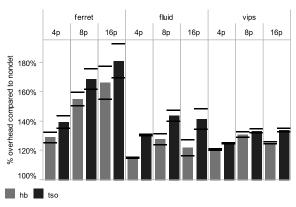

| Figure 13: DMP performance with 4, 8 and 16 threads                                           | 49 |

| Figure 14: DMP performance with different quantum sizes                                       | 50 |

| Figure 15: DMP performance with page-granularity conflict detection                           | 51 |

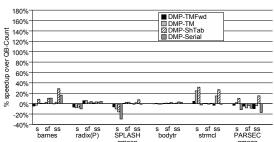

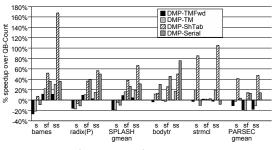

| Figure 16: DMP quantum building schemes' performance with 1,000-insn quanta                   | 51 |

| Figure 17: DMP quantum building schemes' performance with 10,000-insn quanta                  | 51 |

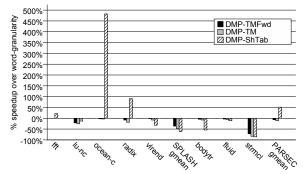

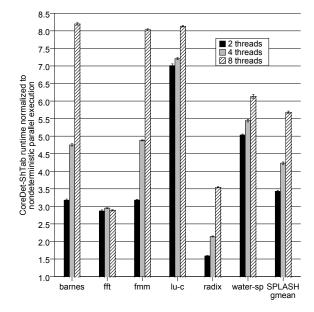

| Figure 18: Runtime of COREDET-SHTAB relative to nondeterministic execution                    | 53 |

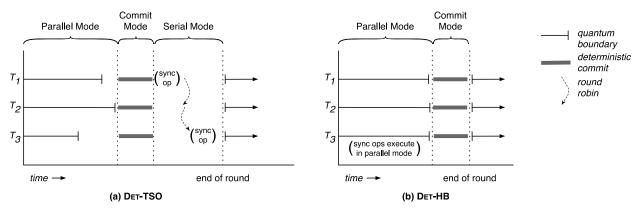

| Figure 19: Timeline of a quantum round in DET-TSO and DET-HB                                  | 59 |

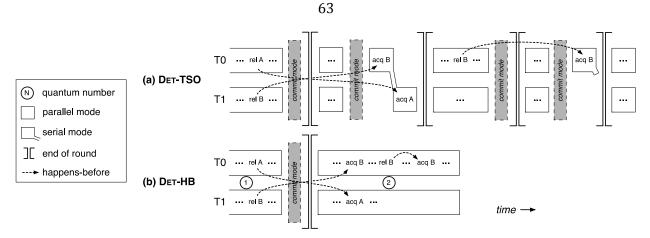

| Figure 20: A comparison of execution under DET-HB and under DET-TSO                           | 63 |

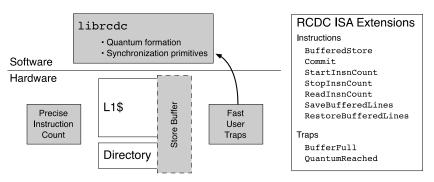

| Figure 21: RCDC system overview                                                               | 64 |

| Figure 22: RCDC commit process when all application threads are scheduled                     | 71 |

| Figure 23: RCDC commit process when an application thread is switched out                     | 73 |

| Figure 24: Deterministic locking for DET-HB                                                   | 74 |

| Figure 25: RCDC performance normalized to NONDET                                              | 79 |

| Figure 26: Performance of RCDC-HB and RCDC-TSO                                                | 80 |

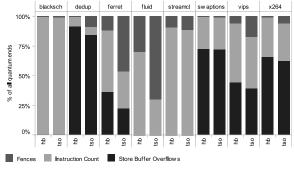

| Figure 27: Reasons why quanta end for RCDC-HB and RCDC-TSO                                    | 80 |

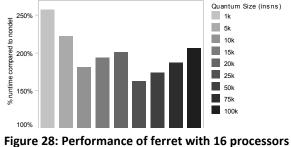

| Figure 28: Performance of ferret with 16 processors using different quantum sizes             | 81 |

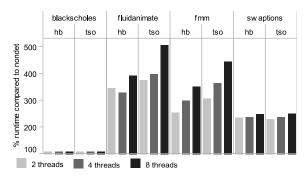

| Figure 29: Performance of CoreDet -HB and CoreDet-TSO                                         | 81 |

| Figure 30: A simple DPJ program with regions and effects                                      | 86 |

| Figure 31: A simple DPJ program with concurrent conflicting tasks                             | 88 |

| Figure 32: Aliasing between exdet and langdet locations results in nondeterminism             | 89 |

| Figure 33: An internally-parallel, in-place sort function that we can easily write in DPJ | 90  |

|-------------------------------------------------------------------------------------------|-----|

| Figure 34: After casting from langdet to exdet, existing langdet aliases must not be used | 92  |

| Figure 35: Assignments between xldet different scopes can introduce nondeterminism        | 93  |

| Figure 36: An updated version of the program from Figure 35                               | 94  |

| Figure 37: Runtime of Java Grande kernels with MELD                                       | 102 |

## LIST OF TABLES

| Table 1: Terminology used in previous conference papers and in this dissertation. | 10 |

|-----------------------------------------------------------------------------------|----|

| Table 2: Characterization of hardware DMP results                                 | 52 |

#### ACKNOWLEDGMENTS

Getting a PhD is not a solo sport. Over the past five years I have benefited from the love and support of an amazing team of people. Two pages are not enough to describe the immense impact they have had on my life and on this work, but I shall try.

Let me start by thanking my advisers Luis Ceze and Dan Grossman. Your complementary backgrounds and research perspectives combine to form an environment that I, and many others in our group, have found incredibly fruitful. Luis, thank you for your energy and for always pushing me to achieve my full potential. Dan, thank you for your diligence and clear thinking that has helped me better understand so many of my own ideas. A special thanks is also due to you both for putting up with my incessant dabbling in new technologies from simulators to presentation software to revision control systems, often at the expense of forward progress. Without your guidance I would surely still be polishing my first simulator to a brilliant but useless sheen.

I owe a tremendous debt of gratitude to my parents for supporting me through college and encouraging me to add a second major that turned out to be a defining event in my life. Throughout grad school their unwavering support and advice have helped me grow, as a researcher and as a person. I am also indebted to my sister for her support and for a steady supply of silliness and amazing baked goods. Many a critical deadline push has been fueled by her amazing éclairs.

At Microsoft Research I had the opportunity to work with Karin Strauss and Shaz Qadeer. I am grateful for their insights, patience in working with me to find a successful project, and for continuing our collaboration long after my internship ended. At UW I had the opportunity to work with many great faculty members. I am grateful to Mark Oskin for helping me get started with research at UW and for career advice as I finished. I also deeply appreciated Susan Eggers' encouragement and honesty throughout my time at UW.

During my time at UW, my fellow graduate students in the SAMPA group have made my life technically, intellectually and socially rewarding. I and the other lab members deeply benefited

viii

from Jacob Nelson's friendship, grace under pressure, and ability to order the chaos of shared computing infrastructure. Brandon Lucia brought a creativity and energy to everything he worked on that I wish I could emulate; the many late-night breaks we took from debugging to laser his cat were also very useful. I am grateful for Tom Bergan's rigorous thinking and incredible coding abilities; the scope of our projects would have been much less without Tom's help. Ben Wood was always great fun to work with, though, given that almost none of our collaborations resulted in publications, perhaps too much so. Ben's skills at creative acronyming are second-to-none. In addition to their friendship and humor, I must also recognize Hadi Esmaeilzadeh for bringing real microarchitecture research to our group, Adrian Sampson for an impeccable presentation style and always ensuring the vegetarians had something to eat, and Owen Anderson for his incredible knowledge of LLVM.

My time in grad school wouldn't have been nearly as rich without the amazing friendship of Kayur, Mike, Tomas, John, Yaw and Ben. From early morning workouts to all-day LOTRO to late-night conversations, with an endless stream of nerdy humor throughout, you guys made me feel at home at UW and in Seattle, and kept me from taking grad school too seriously.

And finally, to my wife Sylvia, a few private words addressed to you in public. You have been a constant source of love, vitality and great cooking throughout my degree. Your honesty and openness have indelibly improved my life, even more than your reliable stream of song parodies. You have additionally contributed to my research in many ways, from helping clarify my presentations and visualizations to many parts of this document as well. I feel so lucky to have you as a partner, and I look forward to all the joys of life we'll share together.

ix

## DEDICATION

To my parents, for their love, generosity and support throughout my life. I would never have made it here without you.

# **Chapter 1 Introduction**

tablets as well. It is already

Over the last several years, multicore processors have steadily displaced their single-core counterparts: first in server rooms, then in desktops and laptops, and most recently in phones and

impossible to buy a new machine with only one core in many market segments. Multicores' swift invasion of the general-purpose processor market has been spurred by the need to meet three simultaneous constraints: high performance, energy efficiency, and limited cooling capacity. Increasing processor frequency has been one of the traditional approaches to improving single-threaded performance, but higher frequencies require higher

processor voltages, driving total chip power usage up per Power =

Capacitance × Voltage<sup>2</sup> × Frequency. Higher power usage also generates more heat that places more stress on cooling. Ultimately, higher power usage and limited cooling capacity defined a "power wall" that placed a practical limit on CPU frequency, reached in 2006 for desktop and server processors (Figure 1, left axis, blue filled circles).

Multicore processors offered a solution to the power wall, as two cores running at N GHz provide the same aggregate performance as one core running at 2N GHz, but with substantial power and cooling savings over the single-core processor. These efficiencies have driven the popularity of multicore hardware (Figure 1, right axis, orange empty circles). Unfortunately, the spread of parallel software has not kept pace with that of parallel hardware. Efficient use of now-ubiquitous multicore processors requires that software be parallelized to take advantage of extra computing resources. Manually parallelizing code requires substantial engineering effort, and automatic parallelization remains an open research challenge.

## 1.1 The Challenges of Parallelism

Like all software, parallel software must satisfy criteria like correctness, performance, usability and cost. Parallelism presents special challenges in terms of performance and correctness since parallelism inherits all of sequential programming's difficulties and adds many new ones. The focus of this dissertation will be on techniques to improve the correctness of parallel programs. However, even if it were trivial to write correct parallel programs, many open challenges would remain in ensuring those programs ran efficiently. Much recent research has examined the difficulties of scheduling [2], automatically tuning [3] and performance debugging [4] parallel applications. The work presented in this dissertation strives to improve correctness while having a minimal negative impact on performance.

Parallelism poses many correctness challenges, from dealing with concurrency errors like data races [5,6], atomicity violations [7] and ordering violations [8], to reasoning about the complexities of memory consistency models [9,10], to coping with the nondeterminism inherent in most parallel systems. Nondeterminism is orthogonal to these other challenges – a deterministic system does not eliminate concurrency bugs, nor does eliminating all concurrency bugs eliminate nondeterminism. Nevertheless, we believe that nondeterminism is a more fundamental challenge because the presence of nondeterminism exacerbates parallelism's other challenges. Nondeterminism destroys reproducibility, introducing a host of issues throughout the software development process. Bugs can appear or disappear from run to run, defeating attempts to understand and remove them. Testing's guarantees are weakened in the presence of nondeterminism, because a passing test says little about future behavior. Deployed software can similarly expose new issues that are difficult to reproduce. Finally, nondeterminism frustrates attempts at replicating multithreaded programs as the replicas can easily diverge, nullifying the reliability or availability benefits of replication.

**1.2 The Benefits of Reproducibility and Determinism**

Reproducibility does not directly improve the correctness of a parallel program, but it is a key enabler of correctness. Figure 2 shows the benefits reproducibility brings to the process of developing multithreaded software, from debugging through testing and deployment. We

distinguish between two flavors of reproducibility: a weak flavor achievable via either determinism or record and replay mechanisms that improves the debugging process, and a strong flavor possible only via determinism (the shaded region in Figure 2) that improves testing and deployed code as well.

Reproducibility is crucial for improving the process of **debugging** parallel software. Nondeterminism is the source of timing-sensitive "heisenbugs" which can disappear when run under a debugger or manifest only infrequently when run natively. Nondeterminism also thwarts any use of reverse debugging [11], a technique that helps to triage bugs. In contrast, deterministic execution allows buggy executions to be replayed, both forwards and backwards, in the same straightforward manner in which single-threaded programs can be.

**Testing** a multithreaded program often relies on stress testing: running a program with the same input many times to haphazardly exercise a variety of timing conditions, some of which might expose bugs. Determinism eliminates the need to perform stress testing since program execution is guided solely by its input.

Determinism can amplify the power of static analysis tools like model checkers [12] by reducing the size of the state space they must explore. Determinism can also assist dynamic tools (e.g., data race

detectors [13,14]) that focus on verifying a single execution with lower overhead, but suffer acutely from nondeterminism that makes detected errors hard to reproduce and guarantees about future executions impossible to provide. Deterministic execution acts as a powerful lever for dynamic analysis, by providing repeatability, and also ensuring that once a given input has been verified as safe, all future executions of that input will be safe as well. Such a guarantee about future executions can also be leveraged to enable new forms of incremental re-verification in response to code changes.

Code tested and then **deployed** on a deterministic platform has two significant advantages over code running on a nondeterministic platform. First, any tested inputs used in production are guaranteed to have the same behavior in both environments. This allows developers to have high confidence in their software; nondeterminism can no longer introduce a dramatically new set of behaviors once their software is deployed. Second, bugs manifesting on a machine in the field can be reproduced back in a development environment.

Finally, deterministic execution makes it simple to **replicate** multithreaded programs for faulttolerance: broadcasting inputs to all replicas ensures they remain synchronized.

Weak reproducibility makes reverse debugging possible, and allows bugs that appear during testing or in production to be reproduced. Determinism, however, brings the benefits of reproducibility full circle by 1) eliminating the need to stress test, since a parallel program always behaves the same way for a given input, 2) ensuring that no new behaviors for a given input are possible in production, increasing the assurance provided by testing, ultimately 3) making deployed code more reliable. The value of even weak reproducibility can be seen in the commercial support for tools that make single-threaded executions repeatable, such as VMWare's replay debugger [15] and gdb's recent support for reverse execution [16]. Support for multithreaded execution is less common; one example is Corensic's Jinx tool [17] that offers limited amounts of reproducibility in testing environments. Next-generation tools that offer deterministic execution would be of even

5

### **1.3 Previous Work on Deterministic Parallelism**

Prior to our work on execution-level determinism, a language-based approach was required to achieve deterministic parallelism. We briefly outline the most relevant language-based work here, and defer a fuller discussion of other related work in deterministic parallelism to Section 2.5.

Currently-proposed **deterministic languages** favor reduced expressiveness over runtime instrumentation. StreamIt [18] is a deterministic stream processing language that restricts programmers to a non-Turing-complete language without loops in exchange for static guarantees about the buffer sizes needed to implement a stream pipeline. NESL [19] and Deterministic Parallel Java (DPJ) [20] offer a similar bargain in supporting only fork-join parallelism. NESL is a purely functional language, and its lack of mutability avoids issues with interference – when concurrent threads read and write the same data. DPJ adds a sophisticated type-and-effect system to Java to statically prove non-interference for concurrent threads, while still supporting Java's fully mutable semantics. NESL and DPJ's static approaches provide determinism with zero runtime overhead, running programs as efficiently as nondeterministic languages. In addition to performance, deterministic languages provide strong safety guarantees in the form of sequential semantics: because the operations of concurrent threads have been proved non-interfering, parallelism does not affect the program's outcome. Deterministic languages are a safe and performant approach to parallelism for programs that fit within their restrictions.

Other approaches to deterministic parallelism have embraced existing languages but support only restricted **programming models**, such as requiring data race freedom or forbidding the use of complex synchronization mechanisms like locks. Task parallel frameworks like Cilk [21] (see Section 2.2.1) have exactly these restrictions. Writing a data race or resorting to the use of richer synchronization primitives can silently result in nondeterministic execution. Grace [22] is a notable exception: it explores support for a C/C++ nested fork-join programming model with isolation enforced via virtual memory protection. Isolation, plus the lack of synchronization idioms other than fork and join, guarantees the determinism of Grace programs. Concurrently with our initial

work on determinism, Kendo [23] proposed deterministic execution for data-race-free C/C++ programs that use arbitrary synchronization. Kendo exploits data race freedom to avoid the need for expensive thread isolation. Kendo also takes advantage of hardware performance counters to provide very reasonable overheads, at roughly 20% slowdown with 4 threads.

### **1.4 Dissertation Goals and Contributions**

The goal of this dissertation is to evaluate the feasibility and efficiency of techniques that provide determinism for arbitrary parallel programs. Toward this goal we furnish three specific contributions, in the design and evaluation of three deterministic execution systems. The first, DMP or Deterministic MultiProcessor [24,25], is a pure-hardware design that leverages hardware's ability to perform low-overhead speculative execution. The second, RCDC or Relaxed Consistency Deterministic Computer [26], proposes a hybrid hardware-software design for reduced complexity with equivalent performance to DMP. The final system is MELD [27], a pure-software approach for Merging Execution-level and Language-level Determinism that reduces the runtime overhead of execution-level determinism by integrating static, language-based techniques.

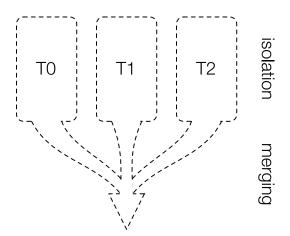

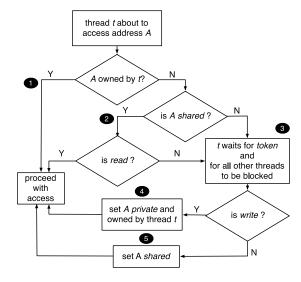

Despite the variety of implementation technologies used in these three systems – from hardware transactional memory to type systems – DMP, RCDC and MELD share a common approach to providing determinism (Figure 3). Initially, each thread of a multithreaded program is placed in an *isolated* memory space, wherein an update to shared memory is visible only to the thread that performed the update. Effectively, the original multithreaded program is converted into a

Figure 3: Our basic approach to determinism is precise control of thread communication, with alternating periods of isolated execution and deterministic merging of accumulated outputs.

collection of single-threaded programs. Single-threaded programs naturally execute in a deterministic fashion; thus the determinism of the entire program is ensured. The mechanism used to ensure thread isolation varies depending on the deterministic execution system, from processor-

private hardware caches to runtime instrumentation to static analysis that proves isolation at compile-time.

Of course, threads must periodically *communicate* with one another in order for the program to execute correctly. Thus, inter-thread communication is allowed at regular intervals, subject to two restrictions. First, these communication points must arise at deterministic places in the execution. Second, the communication itself, i.e., *merging* updates that have been performed by remote threads, must be performed deterministically. Again, the mechanisms used to implement deterministic communication differ by system. Counting fixed numbers of machine or bytecode instructions is a persistent approach for identifying deterministic points in an execution. Mechanisms for merging updates deterministically range from hardware techniques for thread-level speculation [28] to order-independent geometry rendering algorithms [29] from computer graphics.

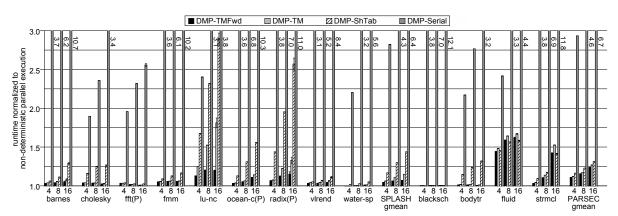

### 1.4.1 DMP: A Deterministic MultiProcessor

DMP ([24] and Chapter 3) is a novel hardware architecture that runs programs deterministically, even if they use arbitrary synchronization constructs or contain data races. The DMP design built upon existing proposals for hardware transactional memory [30], a vibrant research area that has made the transition into shipping products from IBM [31,32] and Intel [33] (see Section 3.2.3). DMP divides the execution of each thread into a series of transactions and ensures that these transactions commit in a deterministic order. The size of transactions can be adjusted to match the limitations of a hardware transactional memory system, eliminating the need for unbounded transactions. To evaluate DMP, we built an architecture simulator demonstrating that DMP incurs approximately 20% overhead compared to nondeterministic execution.

### 1.4.2 RCDC: A Relaxed Consistency Deterministic Computer

To bring the benefits of deterministic execution to today's systems, we then designed the CoreDet algorithm [34] for deterministic execution. The main insight behind CoreDet was that DMP's need for always-on speculation could be exchanged for a non-speculative approach coupled with a more

relaxed memory consistency model based on Total Store Order [35,36]. This new design admitted a realizable software implementation of execution-level determinism. The CoreDet deterministic compiler [34] provides determinism for arbitrary C/C++ programs. The CoreDet compiler is open-source and has been downloaded by researchers at over 20 institutions worldwide. Our experiments show that CoreDet exacts a 5x slowdown on average, but brings the benefits of determinism to existing programs running on today's hardware.

To maintain determinism, CoreDet required that synchronization operations be serialized – a clear scalability bottleneck for programs that use frequent synchronization. The RCDC deterministic execution algorithm ([26] and Chapter 4) eliminates this bottleneck via additional consistency relaxations coupled with a more scalable deterministic synchronization algorithm from prior work [23]. RCDC affords a natural hardware-software implementation, leveraging private caches to cheaply enforce thread isolation while leaving software in control of making updates visible. To show the generality of the RCDC approach, we built a hardware simulator to evaluate our hybrid hardware-software design and extended the CoreDet compiler to evaluate a pure-software design as well. Both in simulation and in software, RCDC significantly improves the performance of programs with fine-grained synchronization. Moreover, RCDC's hybrid hardware-software implementation provides fully deterministic execution with performance comparable to that of the original DMP hardware proposal, without the need for always-on speculation.

The source code of our implementations of CoreDet and RCDC, as well as the raw data presented in the RCDC paper, are available from <a href="http://sampa.cs.washington.edu">http://sampa.cs.washington.edu</a>.

#### 1.4.3 MELD: Merging Execution-level and Language-level Determinism

MELD leverages both our experience building execution-level determinism systems and the rich and deeply complementary body of work on deterministic parallel languages. On the one hand, execution-level determinism enforces determinism *dynamically* for arbitrary programs but with runtime costs. On the other hand, deterministic languages enforce determinism *statically* without

runtime overhead and with sequential semantics but only support fork-join programs expressible in sophisticated but limiting static type systems.

To combine the generality of dynamic determinism with the performance of static determinism, we designed the MELD system ([27] and Chapter 5) that merges execution-level and language-level determinism in a sound, i.e., determinism-preserving, manner. To maintain generality, MELD sacrifices the sequential semantics guarantee typical of deterministic languages, as general parallel programs have no natural sequential semantics. MELD uses a simple qualifier-based type system for Java to partition a program's data into regions operated on by either execution-level or language-level determinism. MELD also supports a dynamic privatization mechanism to transition data from one region to the other during program execution. To evaluate MELD, we have built a Java-based execution-level determinism compiler and runtime system, and are working on integrating this with the Deterministic Parallel Java [20] language. Our initial results suggest that static determinism can substantially accelerate deterministic execution's performance, while retaining generality for the remainder of the program.

### 1.5 Reading Guide

Chapter 3 and Chapter 4 are updated versions of the DMP [24] and RCDC [26] conference papers, respectively. These chapters have been revised to include a unified nomenclature, distinguishing between system implementations (DMP, CoreDet and RCDC) and deterministic execution algorithms (DET-\*) which are typically implemented both in a hardware and a software system. Table 1 translates from the terminology of the conference papers to that of this dissertation. We also consistently refer to software implementations of deterministic algorithms as CoreDet, though this results in a slight anachronism in Section 3.4.4 as the original DMP paper [24] proposed a compiler-based implementation before the term CoreDet was later introduced in [34]. For completeness, Table 1's shaded cells translate the terms used in the

| Paper        | Paper Term      | Dissertation<br>Term |

|--------------|-----------------|----------------------|

| DMP [24]     | DMP             | DMP                  |

|              | DMP-Serial      | Det-Serial           |

|              | DMP-ShTab       | <b>Det-ShT</b> ав    |

|              | DMP-TM          | Det-TM               |

|              | DMP-TMFwd       | DET-TMFwd            |

|              | Hw-DMP          | DMP                  |

|              | Hw-DMP-Serial   | DMP-SERIAL           |

|              | Hw-DMP-ShTab    | DMP-SHTAB            |

|              | Hw-DMP-TM       | DMP-TM               |

|              | Hw-DMP-TMFwd    | DMP-TMFwd            |

|              | Sw-DMP          | COREDET              |

|              | Sw-DMP-ShTab    | COREDET-SHTAB        |

| RCDC [31]    | RCDC            | RCDC                 |

|              | DMP-TSO         | Det-TSO              |

|              | DMP-HB          | Det-HB               |

|              | RCDC-DMP-TSO    | RCDC-TSO             |

|              | RCDC-DMP-HB     | RCDC-HB              |

|              | CoreDet DMP-TSO | COREDET-TSO          |

|              | CoreDet DMP-HB  | COREDET-HB           |

| CoreDet [34] | DMP-O           | <b>Det-ShT</b> ав    |

|              | DMP-TM          | Det-TM               |

|              | DMP-B           | Det-TSO              |

|              | DMP-PB          | -                    |

| Table 1: Terminology used in previous conference |

|--------------------------------------------------|

| papers and in this dissertation.                 |

CoreDet paper [34], though the CoreDet system is not discussed at length in this dissertation. Section 3.2.3 includes a new discussion about using upcoming hardware transactional memory support to accelerate the DMP-TM proposal.

Chapter 5 represents a more developed version of the MELD workshop paper [27]. Though the results presented are still preliminary, we envision a subsequent publication to include these and further revisions.

# **Chapter 2 Related Work**

The ideas behind execution-level determinism draw inspiration from a large body of research in making parallelism simpler to express and safer to use. This research ranges from automatically identifying and repairing concurrency defects, to enabling simpler memory consistency models, to providing alternative programming models for parallelism. Directly related to our work on determinism is previous work on managing parallelism implicitly, either via automatically extracting parallelism from sequential programs or via deterministic and implicitly-parallel languages. Also directly related are techniques for record and replay of multithreaded programs, and execution-level determinism systems from other researchers inspired by our systems.

## 2.1 Concurrency Bug Detection and Survival

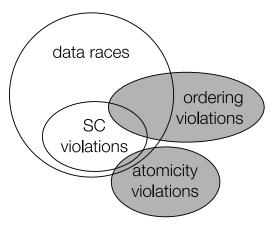

There have been many proposals for automatically detecting, and in some cases avoiding, bugs in parallel programs. So-called concurrency bugs come in many different classes with overlapping definitions, as shown in Figure 4. Additionally, some classes of errors, e.g., data races and sequential consistency violations, have precise definitions and detectors can be built that will identify all such violations that arise during an

execution. Richer classes of concurrency errors have also been identified, such as atomicity violations [7] and ordering violations [8], that do not have such precise definitions. Atomicity and ordering violations are not axiomatic – they are defined only with respect to some programmer-provided specification that says what operations should be atomic or how operations should be ordered.

#### 2.1.1 Data Races

Data-race-freedom (DRF) has emerged as a safety property that can be usefully applied to general parallel programs. A variety of schemes have been proposed to verify or enforce DRF with a spectrum of performance/precision trade-offs. The gold standard for enforcing DRF is a race detector that is both sound (misses no races) and complete (reports no false races). The core algorithm for fully precise data race detection is the vector-clock

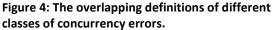

algorithm [5,6,37]. Vector-clock data race detection uses the happens-before relation to order events within and between threads in a parallel program. The happens-before relation is a partial order, and thus two events from different threads may or may not be ordered with respect to one another: events that are not ordered are said to be concurrent. For events occurring in a single thread, the happens-before relation includes program order. Figure 5 gives an example of an interthread happens-before edge, which arises between release and acquire operations of the same lock (the dashed arrow); the operations on location A are ordered by the happens-before edge (plus program order in each thread) while the operations on location B are not. A data race arises if two memory accesses from different threads are concurrent and access the same memory location in a conflicting way, i.e., at least one of the accesses is a write. In Figure 5, the operations on location B form a data race. Programs that are DRF provide three important properties. First, they execute in a sequentially-consistent manner [9,10]. Second, synchronization-free regions of code execute atomically and in isolation [38]. Third, for an access A to a variable V, the value of V cannot change due to remote operations within A's interference-free region – the region of code from A's immediately preceding lock acquire to A's immediately subsequent lock release [39,40]. Taken together, these properties make DRF programs much easier to write and to reason about than non-DRF programs.

In order to verify DRF, researchers have proposed techniques to detect data races. Many static race detection algorithms have been explored (e.g., [41]) though they are invariably unsound or incomplete due to undecidability. Dynamic race detection algorithms have been proposed as early as 1989 [42], and since then researchers have steadily improved the time and space performance of race detection while exploring the trade-offs of various soundness and completeness guarantees. Eraser [43] proposed **lockset** violation detection, an approximation of race detection which assumes that a consistent set of locks are used to protect each shared variable. Eraser automatically infers the association between locks and variables, and then checks for violations of this inferred locking discipline. As not all programs hold a consistent set of locks when protecting a given variable – e.g., the set of locks can change when a variable is privatized by different threads – Eraser can report spurious races where none exist, though it never misses races. HARD [44] is a hardwarebased implementation of the lockset algorithm that uses bloom-filters per cache line to encode which locks should be held when accessing the corresponding data. Goldilocks [14] is a locksethappens-before hybrid race detection algorithm that uses locksets to accelerate race detection while maintaining precision. Goldilocks uses sound (but incomplete) static race detectors [45,46] to reduce runtime overheads further, and also proposed throwing a language-level exception when a race is detected, an idea that would be subsequently explored in [38,47]. While the lockset algorithm is imprecise, it remains useful because, until recently [13], it held a significant performance advantage over precise forms of race detection.

The latest advance in fully precise race detection is the FastTrack race detector [13], which reduces the per-shared-variable space needs of a traditional vector-clock algorithm from O(n), where n is the number of threads in the program, to O(1) in many cases. FastTrack leverages the observation that programs typically protect all accesses of a location x – both reads and writes – with a single lock. Thus, there is typically only 1 previous reader for a given location, and there is no need to store information for each of n potential readers. For correctness, FastTrack can dynamically transition to a O(n) representation when necessary to support more complicated sharing patterns from, e.g., reader-writer locks. These space savings translate into time savings as well, as race

checks need to examine fewer vector clock entries. The intuition behind FastTrack's optimization is the same as that which motivated lockset race detectors, which assume that programs adhere to a one-lock-per-location invariant and report violations thereof. Lockset race detection was originally proposed as a faster, though incomplete, alternative to vector-clock race detection [43]. Leveraging lockset's key idea allows FastTrack to provide performance comparable to that of lockset-based race detection, without the latter's tendency to detect false races. However, even with FastTrack the cost of fully sound and complete race detection remains high, incurring a roughly 8x runtime overhead.

Other researchers have improved the performance of data race detection via sampling: turning data race detection off for most of the program to avoid its runtime overheads. In theory, a samplingbased approach can miss arbitrary numbers of races, completely invalidating soundness guarantees. In practice, principled approaches to sampling can perform quite well. LiteRace [48] proposes detecting races based on the frequency with which code paths execute: hot code paths are rarely subject to analysis while cold paths are regularly analyzed. Since the race detection analysis is expensive, but run infrequently, overall performance overhead is around 50%. The consequence is that on average only 70% of races are detected. PACER [49] proposes a different sampling strategy that guarantees that races will be detected in proportion to the sampling rate. PACER divides an execution into time windows, and performs race detection within these windows at a specified rate. To uphold the probabilistic detection guarantee, a limited form of race detection is enabled during non-sampled windows, catching all races where one of the racing accesses is inside a sample and the other access is outside. For a 1% sampling rate, PACER adds runtime overhead of around 50%, and PACER's sampling strategy allows space and time overheads, as well as detection probabilities, to scale up and down with the sampling rate.

While DRF is a useful safety property for multithreaded programs, techniques to fully enforce DRF are too expensive for production use. Sampling strategies decrease runtime overhead substantially, at the cost of reducing DRF to a bug-finding heuristic, instead of a safety property a programmer can rely upon.

#### 2.1.2 Atomicity Violations

Atomicity violations were first described in [7], where they were called "high-level data races" and defined as the following situation: two threads access a

| 0                                                          |                                                                                                                                                  | <b>m</b> 4                    |

|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| shared variable, and while the accesses should have been   | <u>T0</u>                                                                                                                                        | <u>T1</u>                     |

| performed atomically one of the threads performs a series  | load r $0 \leftarrow V$                                                                                                                          |                               |

| of non-atomic accesses to the shared variables due to      | add r $0 \leftarrow$ r $0$ , 1                                                                                                                   | load r $0 \leftarrow V$       |

| programmer error. Figure 6 illustrates an atomicity        | store $r0 \rightarrow V$                                                                                                                         | add r $0 \leftarrow$ r $0, 1$ |

| violation: the load-increment-store operations on V should |                                                                                                                                                  | store $r0 \rightarrow V$      |

| occur atomically but due to a lack of synchronization each | Figure 6: An assembly code example of<br>a single-variable atomicity violation.<br>The lack of atomicity causes TO's<br>increment to be dropped. |                               |

| thread performs them non-atomically. This results in TO's  |                                                                                                                                                  |                               |

|                                                            |                                                                                                                                                  |                               |

update being lost, so that after both threads attempt to increment V only one increment is recorded.

One important property of atomicity violations is that they violate an *atomicity specification* that states which accesses need to be performed atomically. This atomicity specification is, unfortunately, often unavailable and is only implicitly represented by the program's code. While there is no way to know for certain what accesses should be performed atomically in the absence of the actual specification, a number of useful heuristics have been identified. These heuristics inevitably entail both false positives, when an atomicity violation is detected but the program is in fact abiding by its (missing) atomicity specification, and false negatives, when the program's (missing) atomicity specification is deviated from but no atomicity violation is detected.

[7] also generalizes the definition of atomicity violations to accesses of a set of shared variables. This has resulted in two sub-classes of atomicity violations: *single-variable* atomicity violations and *multi-variable* atomicity violations. Figure 6 shows an example of a single-variable atomicity violation involving just the shared variable V. A multi-variable atomicity violation arises when accesses to a *set* of variables should be performed atomically, e.g., when updating the real and imaginary components of a complex number, but due to a programming error the variables are not updated atomically. Detecting multi-variable atomicity violations is inherently more complicated as it requires grouping variables into meaningful sets whose atomicity can then be examined. This grouping process is again driven by heuristics and can be another source of both false positive and false negative atomicity violation reports.

Several atomicity violation detection schemes sidestep false positive/false negative issues by requiring the programmer to provide an atomicity specification. Atomizer [50] requires such a specification, and then dynamically verifies that the specification is adhered to during execution. Atomizer's dynamic analysis is based on lockset race detection, and lockset's intrinsic false positives make Atomizer's atomicity analysis imprecise as well. Velodrome [51] improves upon Atomizer by providing sound and complete atomicity violation detection, again with respect to a programmer-provided specification. In the absence of a provided atomicity specification, e.g., when dealing with legacy programs, both Atomizer and Velodrome evaluate the implicit specification that assumes all functions should execute atomically. While clearly leading to false positives, both schemes report no more than a few dozen warnings per program, making these heuristics tractable.

The Serializability Violation Detector [52] proposed a more sophisticated heuristic for discovering atomicity violations, effective enough to be used in the absence of an actual atomicity specification. Starting from a read access A to a shared variable, SVD infers an atomic region for subsequent accesses that are data- or control-dependent on A. SVD can thus discover some forms of single- and multi-variable atomicity violations automatically. AVIO [53] generalizes the SVD result, proposing a comprehensive framework for single-variable atomicity violations. Using this framework, AVIO uses training runs to infer the atomicity specification of the program: pairs of accesses that are atomic during training runs, but non-atomic during production runs, are likely atomicity violations. AVIO is able to automatically identify four real atomicity violation bugs in Apace and MySQL, with only five false positive reports on average for each program. The AtomAid system [54] automatically repairs atomicity violations by coupling AVIO's techniques for identifying single-variable atomicity violations with the BulkSC architecture [55]. BulkSC groups the dynamic instruction stream into chunks that execute atomically, as a low-overhead way of providing sequential consistency (Section 2.1.4 below). AtomAid adjusts chunk boundaries such that pairs of

accesses representing likely atomicity violations are placed in the same chunk, and, since chunks execute atomically, the atomicity violation will be repaired.

CTrigger [56] is a system that increases the manifestation probability of atomicity violations, making bug detection and other testing tools more effective. CTrigger collects a set of potential unserializable access interleavings (based on the AVIO [53] framework) and uses dynamic analysis to prune away those interleavings that are unreachable due to the program's synchronization. The remaining interleavings are ranked by their likelihood of being an actual bug, and small delays are inserted into the program's execution to make the unserializable interleavings more likely to occur. Using CTrigger makes atomicity violation bugs manifest orders of magnitude more quickly than with regular stress testing.

As researchers made steady progress finding and fixing single-variable atomicity violations, attention turned toward the more challenging problem of multi-variable atomicity violations. While SVD detected some kinds of multi-variable atomicity violations with its data- and controldependence analysis, MUVI [57] pioneered a more general analysis that learns correlations among sets of variables from a series of training runs, and uses these correlations to automatically detect multi-variable atomicity violations. MUVI was able to identify five real-world multi-variable atomicity violations and discovered four new such bugs in Firefox. ColorSafe [58] is another proposal for multi-variable atomicity bug detection and survival. ColorSafe uses memory allocation information to correlate variables, and then uses this information to identify and also proactively avoid likely multi-variable atomicity violations.

#### 2.1.3 General Concurrency Bug Detection

More recent work on concurrency bug detection has focused on new classes of concurrency bugs such as *order violations* [8] and on building concurrency bug detectors that work for many classes of errors. Order violations arise when a program relies on two events, e.g., two critical sections, always occurring in a particular order when the events can occur in either order. Order violations are distinct from both data races and atomicity violations. Unlike data races, the two events in an

order violation may be individually well-synchronized. Unlike atomicity violations, which are inherently unordered, order violations arise due to an expected (but unenforced) ordering. Order violations represent a detection challenge as the presence of an order violation depends on the (often missing) ordering specification of a program.

To cope with rich classes of errors like atomicity and order violations, many researchers have focused on properties common to all concurrency bugs and started building general concurrency bug detectors. These tools focus on detecting problematic patterns among communicating load and store instructions. For example, Bugaboo [59] records the context surrounding inter-thread communication events and uses the context to help differentiate correct from buggy communication patterns. The Interleaving-Constrained Multiprocessor [60] uses testing runs to learn ordering invariants among instructions. During production runs these invariants are enforced by the processor, automatically avoiding problematic interleavings. DefUse [61] learns invariants about which definition each use of a variable should read from, and reports violations of these invariants as errors. The errors uncovered by DefUse can be indicative of concurrency bugs and also sequential bugs like memory errors. Recon [62] focuses on making concurrency bug detection more useful to programmers by automatically identifying the root cause of a bug. Recon's bug reconstructions demonstrate to the programmer not just that a likely error occurred, but also how the program entered the problematic state.

#### 2.1.4 Simplifying Memory Consistency Models

The memory consistency models of modern languages and architectures [9,10,63] are notoriously complex. Despite years of scrutiny, subtle errors have been found in both the Java Memory Model and its JVM implementations [64]. Even assuming the correctness of the model and its implementation, the sequentially consistent (SC) semantics [65] offered by these languages for DRF programs is often void in practice as the DRF precondition is not verified (see Section 2.1.1). Thus, programmers cannot rely on SC behavior. Furthermore, others have noted that DRF implies much stronger properties than SC, e.g., interference-freedom [40]. The resulting "gap" between SC and DRF can be exploited to provide SC much more cheaply than DRF. Motivated by the high overheads

of fully sound and complete race detection, researchers have proposed variations on race detection that enforce SC or detect SC violations. These SC-based schemes have proven to be substantially more performant than full data race detection.

Many have proposed using speculation to increase the scope for memory reordering [66–70]. We focus on contemporary approaches, which support relaxing all instruction reorderings across a wider window than previous work. BulkSC [55] and ASO [71] are pioneering architectures that provide high-performance sequential consistency instead of the weaker consistency models common in modern multiprocessors. BulkSC extends the Bulk [72] architecture to provide sequential consistency. The original Bulk architecture offered a mechanism to atomically execute chunks of thousands of instructions, using Bloom filter-based [73] signatures to efficiently encode read and write sets. Bulk's chunk mechanism was used to implement both transactional memory (also called TM, see Section 2.2.2) and thread-level speculation (also called TLS, see Section 2.3) in a unified way. Building on Bulk, BulkSC groups a program's entire dynamic instruction stream, instead of just TM or TLS accesses, into chunks. Speculative execution of each chunk allows processors to execute chunks in parallel for high performance, and the ability to aggressively reorder instructions within a chunk eliminates many potential consistency-related processor stalls. Pipelined chunk execution reduces the latency of cross-chunk consistency stalls as well so that BulkSC incurs negligible overhead despite providing strong memory ordering. The Atomic Sequence Ordering (ASO) processor [71] also performs memory ordering speculation at coarse granularity, using a scalable FIFO store buffer to guarantee memory ordering and to enable speculation across a large window of instructions. Much like BulkSC, ASO breaks up execution into a series of atomic sequences and guarantees memory ordering only across, not within, sequences. Speculative state is buffered in the L1 cache, avoiding the need for associative search during storeload forwarding. Pristine store values are held in the FIFO store buffer and are accessed only during infrequent commit operations or rarer abort operations. Similarly to BulkSC, ASO provides SC yet outperforms a conventional relaxed-consistency RMO [35] machine. Finally, InvisiFence [74] provides high-performance sequential consistency in the context of a conventional multiprocessor,

unlike BulkSC's dependence on the Bulk architecture, and without the need for a large FIFO store buffer as in ASO. InvisiFence uses the L1 cache for speculative state, and the L2 cache for pristine state, and ensures fast, atomic commit/abort operations via flash-clearing speculative/valid bits, respectively, in the L1 cache. As with BulkSC and ASO, InvisiFence provides SC memory ordering with better performance than a conventional RMO machine.

Subsequent work has looked at exporting sequential consistency farther up the programming stack. Conflict Exceptions [38] verifies the atomicity and isolation of all synchronization-free regions, a weaker property than DRF but one that can be enforced more cheaply using a simplified version of unbounded hardware transactional memory. Conflict Exceptions guarantees both SC and that all synchronization-free regions execute serializably; otherwise an eponymous "conflict exception" is thrown that terminates the program.

DRFx [47,75] weakens Conflict Exceptions' guarantee in exchange for reduced hardware requirements and better performance. DRFx verifies atomicity and isolation of short compilerdefined regions that are guaranteed not to exceed the resources of a best-effort hardware TM system. Similarly to Conflict Exceptions, DRFx verifies that these regions execute serializably or raises a runtime exception. By allowing only intra-region compiler reorderings, an exception-free DRFx execution is guaranteed to be sequentially consistent. However, the boundaries of these smaller regions are completely governed by the compiler, providing no source-level atomicity guarantees to the programmer.

The primary use of the sequential-consistency-else-exception guarantees of Conflict Exceptions and DRFx is simplifying the memory models of modern languages like Java [9] and C++ [10]. In the absence of these hardware mechanisms, a sequential consistency guarantee is obtainable only for programs that satisfy the stringent DRF requirement, and in conventional systems there is no checking of whether programs have in fact satisfied it. The stronger atomicity and isolation guarantees of Conflict Exceptions may be useful to compiler writers or even application programmers, though the performance implications of the need to support unbounded

synchronization-free regions have not been clearly evaluated. A recent in-depth performance evaluation of the DRFx architecture [75] found that its runtime overheads were quite modest – less than 25% for a simulated 16-core machine – showing that supporting SC throughout the execution stack can be done affordably.

Other work on memory consistency has focused on extracting maximum performance from weak consistency models. The Conditional Memory Ordering (CMO) system [76], which observes that the fence semantics offered by modern processors are frequently stronger than is needed to correctly implement language memory models like the JMM. CMO elides memory fences at runtime when they are dynamically unnecessary, and a pure-software implementation of CMO improved the performance of many Java applications by 5-10%. In a similar vein, [39] exploits the full flexibility of the C++ memory model [10] to expand the scope for compiler optimizations across lock acquires and releases (see Section 2.1.1). The extra flexibility allows the compiler to elide many memory instructions that a conventional compiler cannot, and though the resulting performance impact is negligible many optimization opportunities remain unexplored. The RCDC system (Chapter 4) takes similar advantage of language memory models' relaxations to reduce the cost of deterministic memory ordering, which is even more expensive than its nondeterministic counterpart. RCDC's consistency optimizations in particular are modeled heavily on CMO's design.

### 2.2 Programming Models for Parallelism

Parallel programming models have a long history both in theory and in practice, dating back nearly as long as computing itself. This section examines select recent developments in parallel programming models that are most relevant for understanding the deterministic systems described in Chapters 3-5.

### 2.2.1 Task Parallel Frameworks

Tasks are an increasingly popular programming abstraction for parallel architectures. Many major hardware and software vendors have produced task parallelism frameworks, from Intel's Cilk [21] and Threading Building Blocks [77] to Apple's Grand Central Dispatch [78], Microsoft's Task

Parallel Library [79] and Java's ForkJoin framework [80]. These task parallel frameworks abstract away notions of processors and threads, requiring programmers to think only in terms of tasks and the dependences between tasks. Task dependences are often specified via control flow, instead of via locks and shared memory, resulting in a simplified programming model. The runtime system manages the scheduling of tasks onto actual processing resources, honoring dependences and preventing the hardware from being over- or underutilized.

Task systems answer many of parallel computing's performance challenges, but their correctness benefits are less clear. Data races are still possible if a programmer specifies task dependences incorrectly. The Cell Superscalar (CellSs) task system [81] offers the potential for increased safety by requiring that inter-task communication occur only via function arguments, instead of shared memory. Such a limited interface is likely amenable to automatic dependence verification. Many task systems additionally have very strong repeatability guarantees, providing sequential semantics for race-free programs [21,81]. That is, if a program uses data-race-free task parallelism, it can be debugged and replayed in exactly the same manner as a single-threaded program. However, data races can introduce nondeterminism that voids this guarantee [82]. Overall, current task systems focus on providing performance portability and provide no significant safety benefits over parallel programming with general-purpose languages.

Tasks are also the primary parallelism construct in GPU programming models such as CUDA [83], OpenCL [84] and DirectCompute [85]. Historically, GPUs were programmed for computer graphics in a fork-join style where communication between concurrently-executing tasks was impossible to express in the programming model. More recently, GPUs have begun supporting atomic operations that allow communication between concurrent tasks. These atomic operations can be used to build mutexes, allowing arbitrary parallelism constructs to be expressed [86]. As GPUs adopt more of CPUs' generality, they also inherit the latter's programmability challenges. GPU architecture researchers have adopted many CPU techniques to cope with these challenges, such as race detectors [87,88] and transactional memory [89] (see Section 2.2.2 below).

#### 2.2.2 Transactional Memory

Transactional memory (TM) is similar in spirit to, and borrows its name from, database transactions [90], though TM was first proposed as a hardware accelerator for lock-free data structures [30]. In the original TM proposal, a processor speculatively executes a *transaction* – a series of updates to shared memory that execute atomically and in isolation. The updates are buffered in the processor's L1 cache and so are invisible to remote processors. Cache coherence is used to detect conflicting operations by remote processors. If the local transaction completes without any conflicts, the operation is committed to memory by allowing the buffered cache lines to become globally visible. If a conflict is encountered, the local transaction can be rolled back and the original data fetched again from elsewhere in the memory hierarchy. Transactions, as first proposed, provide an elegant and performant mechanism for implementing multiword CAS operations which simplify many lock-free algorithms.

After this initial hardware TM (or HTM) proposal, the idea of using transactions more broadly as a synchronization mechanism gained tremendous momentum [91]. Transactions offer a compelling alternative to lock-based synchronization, as transactions are 1) a simple, declarative synchronization primitive, 2) amenable to a highly-concurrent implementation whose complexity can be hidden from the programmer, and 3) inherently deadlock-free.<sup>1</sup> Researchers have investigated many aspects of TM, such as support for transactions that overflow the resources of the L1 cache [92], the semantics of transactions and non-transactional code [93], different buffering and conflict detection strategies [94], partial transaction commit to avoid wasted work [95], partial re-execution to avoid the need to perform rollback on conflicts [96], and hybrid hardware-software support for transactions [97]. HTM techniques have also been repurposed to accelerate lock-based critical sections by speculatively eliding lock acquisition [70], to sandbox speculative compiler optimizations [98], and to protect against atomicity violations [99].

<sup>&</sup>lt;sup>1</sup> Application-level progress is not guaranteed, however, as conflicting transactions may continually trigger rollbacks.

Many software TM (or STM) systems have been built as well, in academia [100,101] and also by Microsoft [102], Intel [103], and the GCC team [104]. STM systems have brought to the surface many real-world implementation issues such as interoperating with legacy, lock-based code and handling I/O operations that cannot be rolled back [105]. HTM support was also integrated into some production microprocessors, starting with Azul's formerly-available Vega 3 chip [106] that offered a form of speculative lock elision [70]. Today, IBM's BlueGene/Q processor [32] and zEnterprise EC12 mainframe [31] offer HTM support, and Intel will integrate TM support into the x86 ISA starting with the 2013 Haswell architecture [33].

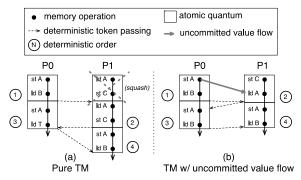

Transactional memory plays an important role in the design of the Deterministic MultiProcessor architecture (Chapter 3). DMP divides the execution of an arbitrary parallel program into a series of transactions. Building on TM's serializable execution semantics, DMP then ensures that the transactions logically execute in a fixed serial order. The underlying TM facility ensures that transactions execute in parallel to recover performance.

## 2.3 Thread-level Speculation

Thread-level speculation (TLS) [28] is a set of techniques to extract parallelism from legacy sequential programs automatically. TLS was originally proposed as a hardware design analogous to out-of-order execution, but at coarser granularity: entire loop iterations or function calls are speculatively executed out-of-order on multiple CPU cores. Sophisticated hardware tracks memory dependences to ensure equivalence to the sequential semantics of the original program.

Knight [107] first proposed hardware support for speculative parallelization of LISP programs. The mostly-functional nature of LISP dramatically simplifies dependence tracking between tasks. Later, Multiscalar [28] proposed the first recognizable TLS system, which extracted parallelism from sequential, imperative code running on a conventional microprocessor. Multiscalar inspired a number of subsequent proposals [108–112]. While the initial TLS proposals required hardware support, they inspired many software-only approaches as well. Speculation and dependence tracking are implemented in software, typically via compiler instrumentation. However, despite a

large amount of research, practical TLS techniques to extract parallelism from sequential programs remain elusive. Recently, impressive results have been obtained from using sophisticated profiledriven compilation and programmer-provided annotations to parallelize sequential integer codes across multiple cores [113] and even nodes in a cluster [114]. This semi-automated parallelization approach seems a promising path going forward.

TLS techniques have inspired many of the techniques used in the DMP system (Chapter 3), though to an opposite end. While TLS seeks to parallelize a sequential program, DMP imposes determinism by serializing a (nondeterministic) parallel program to obtain determinism. DMP exploits the TLS observation that the execution of a program can be parallel even if serial semantics are required. Starting from a parallel program, as DMP does, allows speculative parallelization to be more effective than it has been in the context of sequential programs.

## 2.4 Multithreaded Record and Replay

Record and replay systems can be used to replay an execution for debugging or forensic purposes. Record and replay systems have strong repeatability properties but have not as yet been extended to improve safety. The central design trade-off in record and replay systems is between the amount of execution information logged (which impacts runtime overhead and log size) and the extent to which an execution can be replayed. In particular, we divide record and replay schemes into those that can replay executions with data races and those that cannot. There has also been steady progress in lossless recording techniques, mostly in hardware but recently in software-based systems as well, that has reduced time and space overheads without sacrificing repeatability.

## 2.4.1 Hardware Record and Replay