Lab 3: Digital Design using FPGAs

Overview

Now that you know how to develop SystemVerilog designs and load them into the DE1-SoC board, we can now start looking at more complex designs.

Code for this lab

No code provided! Feel free to copy any needed files from previous labs as a starting point.

Instructions

Task 1 – Multi-level Logic on the FPGA

The customer service department at Nordstrom (the department store) wants an electronic detector device for processing returns. Its goal is to both detect discounted items, so that the proper rebates can be calculated, as well as help find shoplifters returning their ill-gotten gains.

There are six products being sold. The following table shows the Universal Product Code (UPC), whether it was ever on sale (i.e., sold at a discounted price), and whether it is expensive for each item.

Nordstrom has a special method for finding shoplifters. Whenever they sell an expensive item, they put a secret mark on it at checkout. Thus, expensive items that are purchased are specially marked, while stolen expensive items will not be so marked (inexpensive items are never marked, since it is too expensive to mark everything sold). When there is a return, we want to make sure someone didn't steal the item, then return the stolen item for money. Therefore, there are the following four cases to consider for whether or not an item was stolen:

- An expensive, marked item is not stolen.

- An expensive, unmarked item is stolen.

- An inexpensive, unmarked item is not stolen.

- An inexpensive, marked item should never occur, so treat it as a Don't Care.

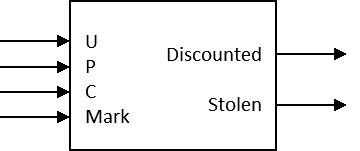

You will be given the UPC of the item under test (signals "U", "P", and "C" for simplicity), and a detector will check for a secret mark ("M"). Your circuit should have one "Discounted" light that lights up whenever a discounted item's UPC is supplied, as well as a "Stolen" light that lights up whenever a theft is detected.

- Create a circuit design by hand for each output. Use K-Maps or Boolean algebra to optimize the design (K-Maps will likely be easiest).

- Write the corresponding SystemVerilog code in Quartus Prime and simulate it, using the available switches and lights on the FPGA as inputs and outputs.

- Download the design to the FPGA and test/debug it.

- Once you have the design working on the FPGA, draw out the finalized schematic for submission.

Lab Requirements

Lab Report

Due before Wednesday section, submitted as a PDF on .

- The K-maps or Boolean simplification you did to create your design (Discounted and Stolen).

- Your circuit diagrams (separate) for Discounted and Stolen.

- A screenshot of the ModelSim simulation with explanation.

- How many hours (estimated) it took to complete this lab in total, including reading, planning, designing, coding, debugging, and testing.

- Separately, upload the SystemVerilog code for your design and related test bench(es).

Lab Demo

Due by the end of the day on Friday, but typically during your assigned demo slot or a scheduled support hour.

- Demonstrate your UPC code circuit working in simulation in ModelSim.

- Demonstrate your UPC code circuit working on the DE1 board.

- Be prepared to answer questions on both the theoretical and practical parts of the lab.

Grading

Working Design

50 points for correctness, style, and testing.

Logic Minimization

Up to 10 points for using as few logic gates as possible.

You are only allowed to use standard gates (AND, OR, NAND, NOR, NOT, XOR, XNOR). Each gate appearing in your hand-drawn circuit diagram counts the same, and gates (other than NOT) can have as many inputs as you want.