#### University of Washington - Computer Science & Engineering

Winter 2024 Instructor: Justin Hsia 2024-03-05

# **CSE 369 QUIZ 3**

| Name:                 | <br>_ |

|-----------------------|-------|

| Student ID<br>Number: |       |

# Please do not turn the page until 11:40.

#### **Instructions**

- This quiz contains 4 pages, including this cover page.

- Show scratch work for partial credit, but put your final answers in the boxes and blanks provided.

- The quiz is closed book and closed notes.

- Please silence and put away all cell phones and other mobile or noise-making devices.

- Remove all hats, headphones, and watches.

- You have 60 (+10) minutes to complete this quiz.

#### Advice

- Read questions carefully before starting. Read *all* questions first and start where you feel the most confident to maximize the use of your time.

- There may be partial credit for incomplete answers; please show your work.

- Relax. You are here to learn.

| Question             |        | Points | Score |

|----------------------|--------|--------|-------|

| (1) Decoders         |        | 13     |       |

| (2) Routing Elements |        | 10     |       |

| (3) Shift Registers  |        | 10     |       |

|                      | Total: | 33     |       |

# **Question 1:** Decoders [13 pts]

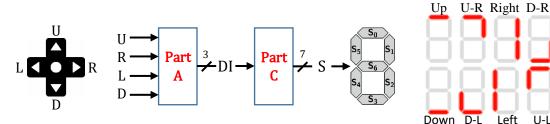

We are building a **7-seg decoder circuit** for a **directional pad** (D-pad), which has a push-button (1 when pushed) for each of the 4 cardinal directions: U(p), R(ight), L(eft), and D(own). There is a physical restriction that at most two neighboring buttons can be pressed simultaneously (*e.g.*,  $UR\overline{L}\overline{D}$  is possible but not  $\overline{U}RL\overline{D}$  or  $URL\overline{D}$ ), leading to 8 possible indicated directions on the 3-bit bus DI, numbered clockwise from Up = 0b000 to Up-Right = 0b001 around to Up-Left = 0b111.

- (A) Complete the truth table. [4 pt]

- (B) In the space below, solve for the minimal logical expression for  $DI_2$ . [4 pt]

| U | R | L | D | DI <sub>2</sub> | DI <sub>1</sub> | DI <sub>0</sub> |

|---|---|---|---|-----------------|-----------------|-----------------|

| 0 | 0 | 0 | 0 | X               |                 |                 |

| 0 | 0 | 0 | 1 | 1               |                 |                 |

| 0 | 0 | 1 | 0 | 1               |                 |                 |

| 0 | 0 | 1 | 1 | 1               |                 |                 |

| 0 | 1 | 0 | 0 | 0               |                 |                 |

| 0 | 1 | 0 | 1 | 0               |                 |                 |

| 0 | 1 | 1 | 0 | X               |                 |                 |

| 0 | 1 | 1 | 1 | X               |                 |                 |

| 1 | 0 | 0 | 0 | 0               |                 |                 |

| 1 | 0 | 0 | 1 | X               |                 |                 |

| 1 | 0 | 1 | 0 | 1               |                 |                 |

| 1 | 0 | 1 | 1 | X               |                 |                 |

| 1 | 1 | 0 | 0 | 0               |                 |                 |

| 1 | 1 | 0 | 1 | X               |                 |                 |

| 1 | 1 | 1 | 0 | X               | _               |                 |

| 1 | 1 | 1 | 1 | Х               |                 |                 |

(C) For the 7-seg signal numbering and outputs shown above (lit/red = 1), draw the minimal logic for  $\mathbf{S_4}$  in terms of DI<sub>2</sub>, DI<sub>1</sub>, and DI<sub>0</sub>. [3 pt]

(D) Briefly describe what's problematic about this D-pad decoder circuit. [2 pts]

| ı |  |  |  |

|---|--|--|--|

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

### **Question 2:** Routing Elements [10 pts]

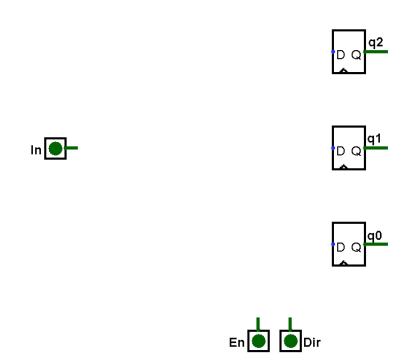

We are creating an *enabled* 3-bit bidirectional shifter (can shift in both directions), which takes input bits **En** (short for Enable), **Dir**, and **In**. When enabled, we shift the current bits either to the right (*i.e.*, into the less significant bit) when  $\mathbf{Dir} = 1$  or to the left when  $\mathbf{Dir} = 0$  and shift in **In**. When not enabled, the state bits remain the same.

(A) Draw the circuit diagram below using *logic gates* and *routing elements* discussed in class. Assume the clock inputs are connected properly for you. You may use multiple copies of a signal name (*e.g.*, q2, q1, q0), which are assumed connected to the same net/wire. [5 pt]

(B) In the Verilog test bench below, fill in the blanks to indicate how the state of our bidirectional shifter updates. [5 pts]

## **Question 3:** Shift Registers [10 pts]

A **boxcar** (or moving average) **filter** computes the average of the last k samples and can be used to smooth out sudden input spikes (*i.e.*, it's a low-pass filter).

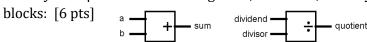

(A) Draw a circuit below that computes the moving average of the last 3 inputs, *i.e.*, k = 3 and  $\mathbf{y_{i}} = (\mathbf{x_{i}} + \mathbf{x_{i-1}} + \mathbf{x_{i-2}})/3$ , for a signal  $\mathbf{x}$ , where  $\mathbf{x_{i-1}}$  is the value of  $\mathbf{x_{i}}$  from the previous clock cycle and so on. The given register is there for synchronization; you should *not* connect anything directly to Input. You can use registers, constants, and any number of the following logic

(B) The time delay portion of the boxcar filter (*i.e.*, computing  $\mathbf{x_i}$ ,  $\mathbf{x_{i-1}}$ , and  $\mathbf{x_{i-2}}$ ) can be considered a shift register! Assuming 1-bit signals and using  $\{\mathbf{x_i}, \mathbf{x_{i-1}}, \mathbf{x_{i-2}}\}$  as our state bits and Input as our input, complete the corresponding Moore machine: the state names correspond to the output state bits, so only the value of Input should be shown on the transition arrows. [4 pts]

-у[i]