# Design of Digital Circuits and Systems Memory I

**Instructor:** Justin Hsia

**Teaching Assistants:**

Colton Harris Deepti Anoop

Gayathri Vadhyan Jared Yoder

Lancelot Wathieu Matthew Hung

## **Relevant Course Information**

- hw1 can still be submitted tonight (1 late day)

- Solution outline will be posted tomorrow (UW login)

- hw2 released today, due next Wednesday (4/10)

- Lab 1 reports due Friday (4/5), demos 4/6-12

- Lab 2 released today, due next Friday (4/12)

- Quiz 1 is Thursday, 4/4 in last 25 min of lecture

- FSM design state diagram, explain design decisions

- 23sp Quiz 1 available for practice on course website

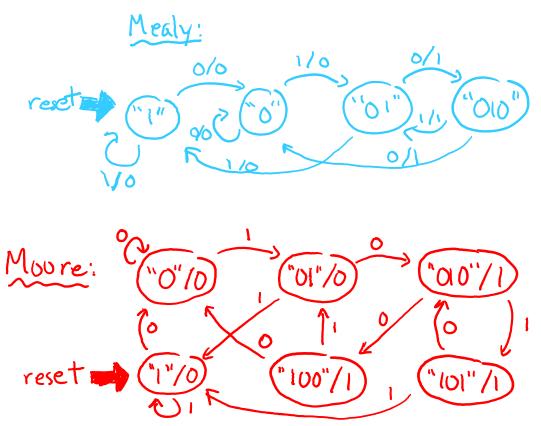

## **Review Question**

- Design a FSM that will output two consecutive 1's any time it sees the string "010" and outputs 0 otherwise

- 1 input bit and 1 output bit

- How many state bits do we need?

- Which state should be your initial/reset state?

- If you have time, design both a Moore machine and Mealy machine "from scratch" (i.e., don't convert between the two)

- Which seems easier to implement? Can you name specific ways that the SystemVerilog implementation will be "easier"?

## **Review Solution**

Design a FSM that will output two consecutive 1's any time it sees the string "010" and outputs 0 otherwise

## **Aside: Powers of 2 and Prefixes**

- Here focusing on large numbers (i.e., exponents > 0)

- SI prefixes are ambiguous if base 10 or 2

- Note that  $10^3 \approx 2^{10}$

- IEC prefixes are unambiguously base 2

#### SIZE PREFIXES (10<sup>x</sup> for Disk, Communication; 2<sup>x</sup> for Memory)

| SI Size         | Prefix | Symbol | IEC Size        | Prefix | Symbol |

|-----------------|--------|--------|-----------------|--------|--------|

| $10^{3}$        | Kilo-  | K      | 2 <sup>10</sup> | Kibi-  | Ki     |

| $10^{6}$        | Mega-  | M      | 2 <sup>20</sup> | Mebi-  | Mi     |

| 10 <sup>9</sup> | Giga-  | G      | 2 <sup>30</sup> | Gibi-  | Gi     |

| $10^{12}$       | Tera-  | T      | 2 <sup>40</sup> | Tebi-  | Ti     |

| $10^{15}$       | Peta-  | P      | 2 <sup>50</sup> | Pebi-  | Pi     |

| $10^{18}$       | Exa-   | Е      | 2 <sup>60</sup> | Exbi-  | Ei     |

| $10^{21}$       | Zetta- | Z      | 2 <sup>70</sup> | Zebi-  | Zi     |

| $10^{24}$       | Yotta- | Y      | 2 <sup>80</sup> | Yobi-  | Yi     |

| 20 =              | 1    |

|-------------------|------|

| 2 <sup>1</sup> =  | 2    |

| 2 <sup>2</sup> =  | 4    |

| 2 <sup>3</sup> =  | 8    |

| 24 =              | 16   |

| 2 <sup>5</sup> =  | 32   |

| 2 <sup>6</sup> =  | 64   |

| 2 <sup>7</sup> =  | 128  |

| 28 =              | 256  |

| 2 <sup>9</sup> =  | 512  |

| 2 <sup>10</sup> = | 1024 |

|                   |      |

## **Large Powers of 2 and Units**

- Because IEC prefixes are powers of 2<sup>10</sup>, we can convert any large power of 2 as follows:

- Note that we are only changing the quantity and the units remain the same

$$2^{XY} \text{ "things"} = - \begin{bmatrix} Y = 0 \to 1 \\ Y = 1 \to 2 \\ Y = 2 \to 4 \\ Y = 3 \to 8 \\ Y = 4 \to 16 \\ Y = 5 \to 32 \\ Y = 6 \to 64 \\ Y = 7 \to 128 \\ Y = 8 \to 256 \\ Y = 9 \to 512 \end{bmatrix} + - \begin{cases} X = 0 \to \\ X = 1 \to \text{Kibi-} \\ X = 2 \to \text{Mebi-} \\ X = 3 \to \text{Gibi-} \\ X = 4 \to \text{Tebi-} \\ X = 5 \to \text{Pebi-} \\ X = 6 \to \text{Exbi-} \\ X = 7 \to \text{Zebi-} \\ X = 8 \to \text{Yobi-} \\ X = 8 \to \text{Yobi-} \end{cases}$$

- Examples:

- 2 GiB of memory? 2 GiB = 21x230 bytes = 231 bytes

- 247 things into IEC: 247 things = 27×240 = 128 Ti-things

## Memory

- Several forms of memory are available, which include:

- Secondary memory (e.g., hard disk, flash drive) not covered in 37/

- Read-only memory (ROM)

- Random-access memory (RAM)

- Register files

- Small, fast, fixed-sized memory that hold CPU data state

- First in, first out (FIFO) buffers

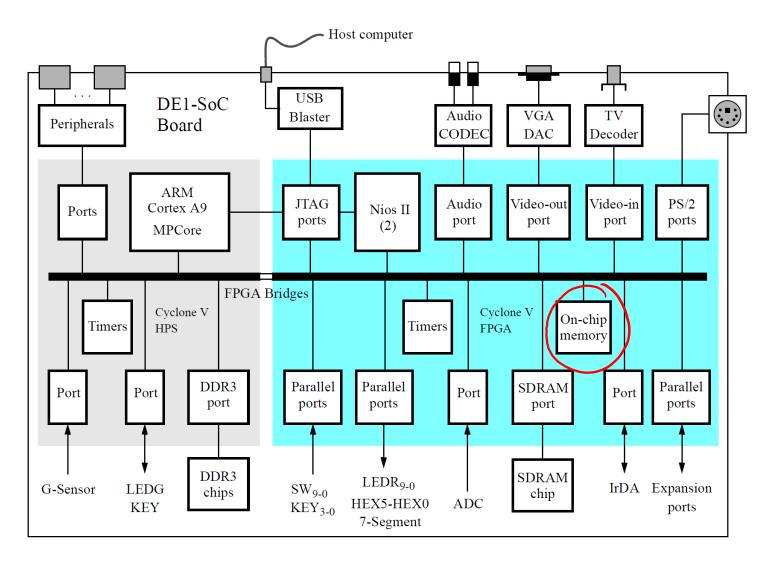

## **Embedded FPGA Memory**

- An FPGA contains prefabricated memory modules

- Intended for small or intermediate-sized storage

- Contents of memory blocks can be configured via memory initialization files (.mif)

- The DE1-SoC's Cyclone V FPGA (Cyclone V SE A5) has:

- 31k Adaptive Logic Modules (ALMs)

- 4.45 Mbits of memory organized as 397 memory blocks, each with 10 kbits of storage (M10K)

- Flexible, configurable memory storage available to the designer

- Each M10K can act as single-port memory, dual-port RAM, shift register, ROM, or a FIFO buffer

- More info on website: DE1-SoC → Cyclone V Handbook

## **DE1-SoC Memory**

Figure 1. Block diagram of the DE1-SoC Computer.

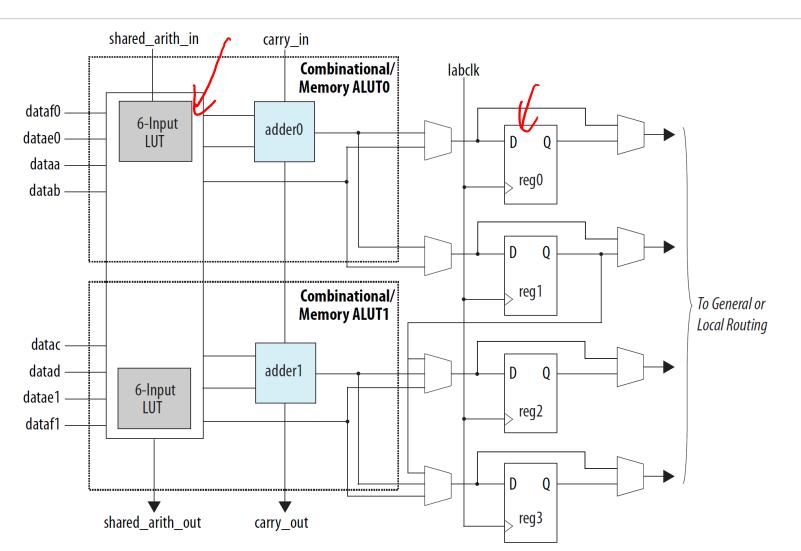

## **Cyclone V Adaptive Logic Modules**

https://www.altera.com/content/dam/altera-www/global/en\_US/pdfs/literature/hb/cyclone-v/cv\_5v2.pdf

Figure 1-5: ALM High-Level Block Diagram for Cyclone V Devices

# **Memory Modules**

- Key characteristics of a simple memory module:

- Width the number of bits in a word

- Depth the number words in the module,

- Number of ports

- Synchronicity of port access whether or not accesses are controlled by a clock signal

- Simultaneous address access can the same address be used for both read and write operations

- \* Example: WriteEnable Address

DataIn

DataOut

DataOut

N

CLK

DataOut

DataOut

N

CLK

DataOut

N

DataOut

DataOut

DataOut

DataOut

DataOut

D

# **Memory Characteristics**

- Memory units are specified as depth × width.

- \* For the following memory units, answer:

1) Memory capacity (in bits and bytes using IEC prefixes)

- 2) Width of address bus (a)  $\log_2(\operatorname{depth})^7$

- 3) Width of data output bus (n) width

- (1) 2 18 bits = 256 Kibits = 32 Ki-bytes

- (3) 32 bits

- (1) 234 bits = 16 Gibits = 2 Gibytes

# Technology

# Break

## Memory Type #1: ROM

## Read-Only Memory

- A purely combinational circuit (no internal state)

- Output is determined solely by address input

#### In an FPGA:

- No actual embedded ROM, but can be emulated by a combinational circuit or a RAM with the write operation disabled

- Only practical for small tables

### In SystemVerilog:

- Define the ROM content as a 2-dimensional constant

- Oftentimes a selected assignment or case statement

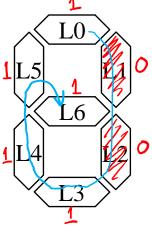

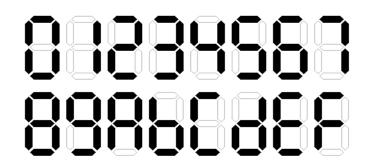

# **Example ROM**

Hex-to-7seg LED decoder:

Segments:

Active low

\* ROM size?

B3 B2 B1 B0 L0

## **Example ROM (SystemVerilog)**

```

module ROM case(addr, data);

input logic [3:0] addr;

output logic [6:0] data;

always_comb

case (addr)

16543210

4'h0: data = 7'b1000000;

4'h1: data = 7'b1111001;

4'h2: data = 7'b0100100;

// ...

4'hD: data = 7'b0100001;

4'hE: data = 7'b0000110;

4'hF: data = 7'b0001110;

endcase

endmodule

```

## Reading Data from a File

- Hard-coded values in your SV files can be tedious to format, debug, and swap out!

- Verilog provides system tasks to read data from a text file into an array: \$readmemb() and \$readmemh()

- Basic usage: \$readmemb("file.txt", my\_array);

- Reads in numerals (in binary or hex) from file separated by whitespace (i.e., spaces, tabs, newlines)

- Can avoid some recompilation

- File can have any extension (.txt, .mem, .bit, .hex)

- Re very careful with dimensions of array and ordering of data in file!

# **Example ROM (SystemVerilog)**

```

module ROM file(addr, data);

input logic [3:0] addr;

output logic [6:0] data;

logic [6:0] ROM [0:15]; // (!) unpacked dimension

initial

// reads binary values from file into array

$readmemb("seg7decode.txt", ROM);

assign data \(\delta\) ROM[addr\];

dimensions

match

endmodule

white space

need as ROMIO]

1000000 1111001 0100100 0110000

seg7decode.txt:

read left to right, then top-to-bottom.

0011001 0010010 0000010

1111000

0000000 0010000 0001000 0000011

1000110 0100001 0000110 0001110

```

## **Dynamic Array Indexing Operation**

A signal can be used as an index to access an element in the array:

```

assign data = ROM[addr];

equivalent to

```

```

always_comb

case (addr)

4'h0: data = ROM[0];

4'h1: data = ROM[1];

// ...

4'hE: data = ROM[14];

4'hF: data = ROM[15];

endcase

```

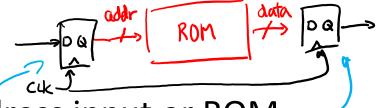

# **Synchronicity Revisited**

- To synchronize either the address input or ROM output, we can add a register as appropriate

- Sometimes called "registering" the input or output to make your module "synchronous"

- In SystemVerilog, can be done inside or outside of the module:

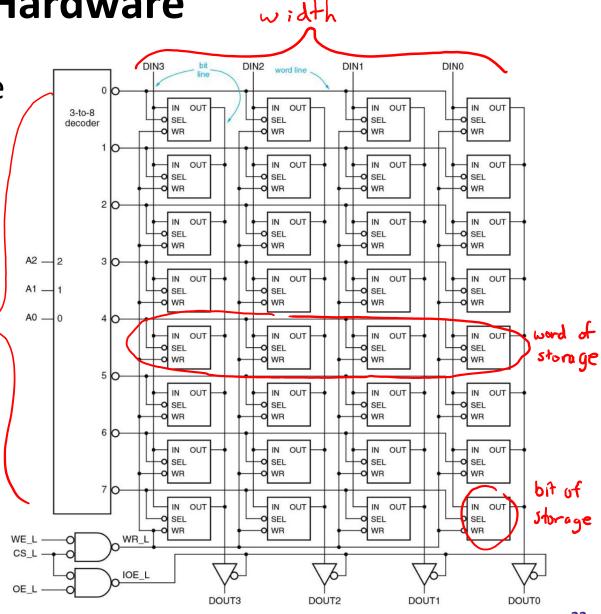

## Memory Type #2: RAM

- Random-Access Memory

- Can read and write to any address instead of having to read in sequence (e.g., a magnetic disk)

- Can be implemented using different semiconductor technologies:

- Static RAM (SRAM): uses flip-flops to store data

- Dynamic RAM (DRAM): uses capacitors and transistors to store data that need to be periodically refreshed

- SRAM is faster but more expensive than DRAM

- In a typical home computer:

- CPU registers and caches are SRAM

- "Memory" is synchronous DRAM (SDRAM)

Internal structure of an 8 × 4 static RAM:

> Figure 15.18 from Wakerly

## **RAM Variants**

- Note that not all of the terminology used here is standardized:

- 1) Synchronicity

- Are the operations controlled by the clock?

- Can be applied to reading and writing independently

- 2) Number of ports

- Not in the same sense as number of SV module ports

- Can roughly think of as "channels" (set of addr in, data in, write enable, and data out ports) – how many reads and writes can occur simultaneously?

- 3) Address independence

- Are the port's read and write operation based on the same or independent addr in buses?

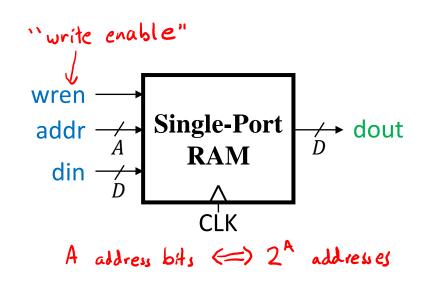

## **Synchronous Single-Port RAM**

## Synchronous Inputs:

- wren (1 = write, 0 = read)

- addr (A-bit address)

- din (D-bit data)

### Synchronous Output:

dout (D-bit data)

## Implementation hints:

- Will need an internal RAM array of what size? 2<sup>A</sup> × D

- To synchronize, should update on clock triggers always ff@ (psolge clk)

- What should dout do when wren = 1? also set to din

# Synchronous Single-Port RAM (SV)

```

module RAM single #(parameter A, D)

(clk, wren, addr, din, dout);

input logic clk, wren;

input logic [A-1:0] addr;

input logic [D-1:0] din;

— could be either ordering since we aren't loading from a file

output logic [D-1:0] dout;

logic [D-1:0] RAM [0:2**A-1];

always_ff @(posedge clk) begin

if (wren) begin //wrte.

RAM[addr] <= din;</pre>

Can't be RAM[addr] become non-blocking assignment

dout <= din;</pre>

end

11 read

else

dout <= RAM[addr];</pre>

end // always ff

endmodule

```