| ADC Multiplexer Selection<br>Register – ADMUX | These bits<br>are chang<br>complete<br>used if an | s select th<br>jed during<br>(ADIF in<br>external | 0 5 4 3 2 1 0   REFS0 ADLAR MUX1 MUX2 MUX2 MUX1 MUX0   RW RW RW RW RW RW RW MUX1 MUX2   0 0 0 0 0 0 0 0 0   0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                             |  |  |  |  |  |

|-----------------------------------------------|---------------------------------------------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                                               | REF\$1                                            | REF S0                                            | Voltage Reference Selection                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|                                               | 0                                                 | 0                                                 | AREF, Internal Vref turned off                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|                                               | 0                                                 | 0 1 AVCC with external capacitor at AREF pin      |                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|                                               | 1                                                 | 0                                                 | Reserved                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|                                               | 1                                                 | 1                                                 | 1 Internal 2.56V Voltage Reference with external capacitor at AREF pin                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|                                               | The ADL/<br>Register.<br>adiusted.<br>regardles   | AR bit aff<br>Write on<br>Changir<br>s of any o   | ADC Left Adjust Result<br>acts the presentation of the ADC conversion result in the ADC Data<br>e to ADLAR to left adjust the result. Otherwise, the result is right<br>to the ADLAR bit will affect the ADC Data Register immediately,<br>ongoing conversions. For a complete description of this bit, see "The<br>- ADCL and ADCH" on page 218. |  |  |  |  |  |

| Special FunctionIO Register | -                                                                                |                                                                                                                         |                                                                                       |                                                                            |                                       |                                      |                                     |                                        |

|-----------------------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------------|--------------------------------------|-------------------------------------|----------------------------------------|

| SFIOR                       | Bit                                                                              | 7 6                                                                                                                     | 5                                                                                     | 4 3                                                                        | 2                                     | 1                                    | 0                                   |                                        |

|                             | Read/Write                                                                       | ADTS2 ADTS1<br>R/W R/W                                                                                                  | 1 ADTS0<br>R/W                                                                        | - ACME                                                                     | R/W                                   | PSR2<br>R/W                          | PSR10<br>R/W                        | SFIOR                                  |

|                             | Initial Value                                                                    | 0 0                                                                                                                     | 0                                                                                     | 0 0                                                                        | 0                                     | 0                                    | 0                                   |                                        |

|                             | • Bit 7:5 – A                                                                    | DTS2:0: ADO                                                                                                             | C Auto Trigg                                                                          | er Source                                                                  |                                       |                                      |                                     |                                        |

|                             | effect. A con<br>Note that sw<br>will generate<br>start a conve<br>ger event, ev | DC conversio<br>version will be<br>itching from a<br>a positive ed<br>rsion. Switchir<br>en if the ADC<br>DC Auto Trigg | e triggered b<br>a trigger sourn<br>lge on the trig<br>ng to Free Ru<br>Interrupt Fla | y the rising<br>ce that is cle<br>gger signal.<br>unning mode<br>g is set. | edge of ti<br>eared to a<br>If ADEN i | he select<br>a trigger s<br>in ADCSI | ed Interr<br>source th<br>RA is set | upt Flag.<br>at is set,<br>, this will |

|                             | ADTS2                                                                            | ADTS1                                                                                                                   | ADTS0                                                                                 | Trigger So                                                                 | urce                                  |                                      |                                     |                                        |

|                             | 0                                                                                | 0                                                                                                                       | 0                                                                                     | Free Runn                                                                  | ing mode                              |                                      |                                     |                                        |

|                             | 0                                                                                | 0                                                                                                                       | 1                                                                                     | Analog Co                                                                  | mparator                              |                                      |                                     |                                        |

|                             | 0                                                                                | 1                                                                                                                       | 0                                                                                     | External In                                                                | terrupt Re                            | quest O                              |                                     |                                        |

|                             | 0                                                                                | 1                                                                                                                       | 1                                                                                     | Timer/Cou                                                                  | nter0 Com                             | pare Mato                            | sh                                  |                                        |

|                             | 1                                                                                | 0                                                                                                                       | 0                                                                                     | Timer/Cou                                                                  | nter0 Over                            | flow                                 |                                     |                                        |

|                             | 1                                                                                | 0                                                                                                                       | 1                                                                                     | Timer/Cou                                                                  | nter Comp                             | are Match                            | ιВ                                  |                                        |

|                             | 1                                                                                | 1                                                                                                                       | 0                                                                                     | Timer/Cou                                                                  | nter1 Over                            | flow                                 |                                     |                                        |

|                             | 1                                                                                | 1                                                                                                                       | 1                                                                                     | Timer/Cou                                                                  | nter1 Capt                            | ture Event                           |                                     |                                        |

|                             | • Bit 4 – Re:                                                                    | s: Reserved I                                                                                                           | Bit                                                                                   |                                                                            |                                       |                                      |                                     |                                        |

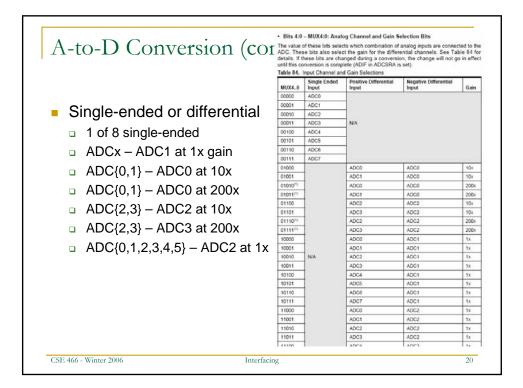

| A-to-D Conve          | rsion (cont'd) |    |

|-----------------------|----------------|----|

|                       |                |    |

|                       |                |    |

|                       |                |    |

|                       |                |    |

|                       |                |    |

| CSE 466 - Winter 2006 | Interfacing    | 24 |

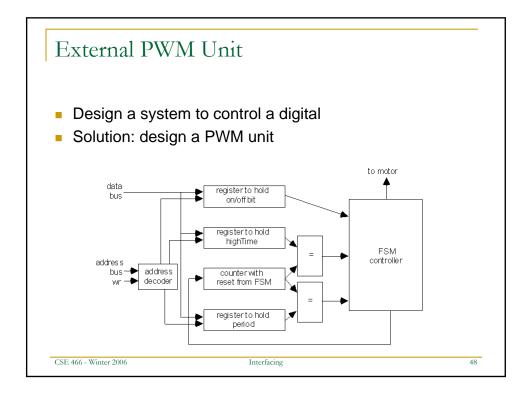

| External I            | PWM software                                                                |    |

|-----------------------|-----------------------------------------------------------------------------|----|

|                       | / in initialization code<br>cite off to onOff register                      |    |

| //                    | / do some stuff                                                             |    |

|                       | / set up PWM<br>epeat for each motor<br>Write highTime and period registers |    |

| , ,                   | / turn motors on<br>epeat for each motor<br>Write on to the onOFF register  |    |

| //                    | / more stuff                                                                |    |

| CSE 466 - Winter 2006 | Interfacing                                                                 | 50 |