# **OPB External Memory Controller** (EMC)

DS421 March 11, 2004

**Product Specification**

## Introduction

This specification defines the architecture and interface requirements for the EMC. This module supports data transfers between the On-Chip Peripheral Bus (OPB) and external synchronous and asynchronous memory devices.

Example synchronous devices for use with this controller are the synchronous Integrated Device Technology, Inc. IDT71V546 SRAM with ZBT<sup>™</sup> Feature. Example asynchronous devices include the IDT71V416S SRAM and Intel 28F128J3A StrataFlash Memory.

The Xilinx EMC design allows the customer to tailor the EMC to suit their application by setting certain parameters to enable/disable features.

## **Features**

The EMC is a soft IP core designed for Xilinx FPGAs and has the following features:

- Parameterized for up to a total of eight memory (Synchronous/Asynchronous) banks

- Separate base addresses and address range for each bank of memory

- Separate Control Register for each bank of memory to control memory mode

- OPB V2.0 bus interface with byte-enable support

- Memory width is independent of OPB bus width (memory width must be less than or equal to OPB bus width)

- Supports memory widths of 32 bits, 16 bits, or 8 bits

- Memory width can vary by bank

- Parameterizable memory data-width/bus data-width matching

- Multiple memory cycles will be performed when the memory width is less than the OPB bus width to provide full utilization of the OPB bus

| C                                                    | iCORE <sup>™</sup> Facts<br>ore Specifics |                                                                                      |  |  |  |

|------------------------------------------------------|-------------------------------------------|--------------------------------------------------------------------------------------|--|--|--|

| Supported Device<br>Family                           | -                                         | <sup>™</sup> , Virtex-II <sup>™</sup> ,<br>E <sup>™</sup> , Spartan <sup>™</sup> -II |  |  |  |

| Version of Core                                      | opb_emc                                   | v1.10b                                                                               |  |  |  |

| Re                                                   | Resources Used                            |                                                                                      |  |  |  |

|                                                      | Min Max                                   |                                                                                      |  |  |  |

| Slices                                               | 168                                       | 310                                                                                  |  |  |  |

| LUTs                                                 | 157                                       | 254                                                                                  |  |  |  |

| FFs                                                  | 215                                       | 445                                                                                  |  |  |  |

| Block RAMs                                           | 0                                         | 0                                                                                    |  |  |  |

| Pro                                                  | vided with Core                           |                                                                                      |  |  |  |

| Documentation                                        | Product Specification                     |                                                                                      |  |  |  |

| Design File Formats                                  | VHDL                                      |                                                                                      |  |  |  |

| Constraints File                                     | N/A                                       |                                                                                      |  |  |  |

| Verification                                         | N                                         | I/A                                                                                  |  |  |  |

| Instantiation<br>Template                            | N                                         | I/A                                                                                  |  |  |  |

| Template                                             | Reference Designs None                    |                                                                                      |  |  |  |

| -                                                    | No                                        | one                                                                                  |  |  |  |

| Reference Designs                                    | No<br>Tool Requiremen                     |                                                                                      |  |  |  |

| Reference Designs                                    | Tool Requiremen                           |                                                                                      |  |  |  |

| Reference Designs Design Xilinx Implementation       | Tool Requiremen<br>5.1i c                 | ts                                                                                   |  |  |  |

| Reference Designs Design Xilinx Implementation Tools | Tool Requiremen<br>5.1i c<br>N            | n <b>ts</b><br>or later                                                              |  |  |  |

Support provided by Xilinx, Inc.

- Data-width matching can be enabled separately for each memory bank

- Configurable wait states for read, write, read in page, read recovery before write, and write recovery before read

© 2004 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and further disclaimers are as listed at <a href="http://www.xilinx.com/legal.htm">http://www.xilinx.com/legal.htm</a>. All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.

NOTICE OF DISCLAIMER: Xilinx is providing this design, code, or information "as is." By providing the design, code, or information as one possible implementation of this feature, application, or standard, Xilinx makes no representation that this implementation is free from any claims of infringement. You are responsible for obtaining any rights you may require for your implementation. Xilinx expressly disclaims any warranty whatsoever with respect to the adequacy of the implementation, including but not limited to any warranties or representations that this implementation is free from claims of infringement and any implied warranties of merchantability or fitness for a particular purpose.

- Optional faster access for in-page read accesses (page size 8 bytes)

- Optional faster access for in-page read accesses (page size 8 bytes)

### EMC Background

The EMC module receives instructions from the OPB to read and write to external memory devices.

The OPB Memory Controller provides an interface between the OPBand one to eight external banks of memory components. The controller supports OPB data bus widths of 8 to 32 bits, and memory subsystem widths of 8 to 32 bits. This controller supports the OPB V2.0 byte enable architecture. Any access size up to the width of the OPB data bus is permitted. When the width of the memory is less than the width of the OPB, multiple memory cycles are performed to transfer the data width of the bus if data-width matching has been enabled for that memory bank.

The controller provides basic read/write control signals and the ability to configure the access times for read, read-in-page, write, and recovery times when switching from read to write or write to read. The controller can be configured to support page-mode reads which can be up to six times faster than non-page reads. The in-page detection logic is automatically configured out of the controller if page mode is not required.

When the OPB Memory Controller is set for flash memory control it is organized much like an SRAM interface. This controller assumes that the Flash programming circuitry is built into the Flash components and that the command interface to the Flash is handled in software. Note that the Flash algorithm for programming Flash locations requires that a write command is written to the location before the actual data is written to the location, therefore, data-width matching should not be enabled for banks of Flash memory.

The ZBT control does not support sleep mode, burst mode, parity checking, or parity generating.

## **EMC** Parameters

To allow you to obtain an EMC that is uniquely tailored for your system, certain features can be parameterized in the EMC design. This allows you to configure a design that only utilizes the resources required by your system, and operates with the best possible performance.

The following characteristics of the External Memory Controller are parameterizable and are described in Table 1:

- Number of separate memory banks

- Memory type, synchronous or asynchronous, per memory bank

- Data width of each memory bank

- Pipeline delay of each memory bank (synchronous memories)

- Read and write access times for each memory bank (asynchronous memories)

- Enabling of data-width matching per memory bank

- Base address for the External Memory Controller registers

### Table 1: EMC Parameters

| Feature /<br>Description                                                                                     | Parameter Name                                  | Allowable Values                                                                                                                        | Default<br>Value    | VHDL<br>Type         |

|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------------|

| Number of Memory<br>Banks                                                                                    | C_NUM_BANKS_MEM                                 | 1 - 8                                                                                                                                   | 2                   | integer              |

| Output/Input data<br>and control signals<br>using the falling edge<br>of the clock <sup>(11)</sup>           | C_INCLUDE_NEGEDGE_IOREGS                        | 0 = don't include<br>negative edge IO<br>registers (data and<br>control signals are<br>input/output on the<br>rising edge of the clock) | 0                   | integer              |

|                                                                                                              |                                                 | 1 = include negative<br>edge IO registers (data<br>and control signals are<br>input/output on the<br>falling edge of the clock)         |                     |                      |

| OPB Clock Period                                                                                             | C_OPB_CLK_PERIOD_PS                             | Integer number of picoseconds                                                                                                           | 10000               | integer              |

| Control Register<br>Bank Base Address                                                                        | C_BASEADDR                                      | Valid Address Range <sup>(3)</sup>                                                                                                      | None <sup>(4)</sup> | std_logic<br>_vector |

| Control Register<br>Bank High Address                                                                        | C_HIGHADDR                                      | Address range must be<br>a power of 2 and ><br>$0x01F^{(3)}$                                                                            | None <sup>(4)</sup> | std_logic<br>_vector |

| Memory Bank x<br>Base Address $(x = 0$<br>to 7)                                                              | C_MEMx <sup>(1,2)</sup> _BASEADDR               | Valid Address Range <sup>(3)</sup>                                                                                                      | None <sup>(4)</sup> | std_logic<br>_vector |

| Memory Bank x High<br>Address (x = 0 to 7)                                                                   | C_MEMx <sup>(1,2)</sup> _HIGHADDR               | Address range must be<br>a power of 2 and $\leq$ OPB<br>Address Space <sup>(3)</sup>                                                    | None <sup>(4)</sup> | std_logic<br>_vector |

| OPB Data Bus Width                                                                                           | C_OPB_DWIDTH                                    | 32                                                                                                                                      | 32                  | integer              |

| OPB Address Bus<br>Width                                                                                     | C_OPB_AWIDTH                                    | 8 - 32                                                                                                                                  | 32                  | integer              |

| Width of Memory<br>Bank x Data Bus                                                                           | C_MEMx_WIDTH <sup>(1)</sup>                     | ≤ C_OPB_DWIDTH                                                                                                                          | 32                  | integer              |

| Execute multiple<br>memory access<br>cycles to match<br>width of Memory<br>Bank x data bus to<br>OPBdata bus | C_INCLUDE_DATAWIDTH_MATCHING_x <sup>(1,9)</sup> | 0 = don't include<br>data-width matching<br>1 = include data-width<br>matching                                                          | 1                   | integer              |

| Device ID number<br>(unique for each<br>device)                                                              | C_DEV_BLK_ID                                    | 0 to 255                                                                                                                                | 1                   | integer              |

| Enable/Disable<br>Module ID Register                                                                         | C_DEV_MIR_ENABLE                                | 0 = don't include Module<br>ID Register<br>1 = include Module ID<br>Register                                                            | 1                   | integer              |

| Feature /<br>Description                                                                                                           | Parameter Name                                                  | Allowable Values                   | Default<br>Value | VHDL<br>Type |

|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|------------------------------------|------------------|--------------|

| Memory type                                                                                                                        | C_SYNCH_MEM_x <sup>(1)</sup>                                    | 0 = memory type is<br>asynchronous | 0                | integer      |

|                                                                                                                                    |                                                                 | 1 = memory type is<br>synchronous  |                  |              |

| Pipeline delay (only<br>used if<br>C_SYNCH_MEM_x<br>= 1)                                                                           | C_SYNCH_PIPE_DELAY_x <sup>(1)</sup>                             | 1 to 2 clocks                      | 2                | integer      |

| Address access time<br>for reads when<br>EMCCRx[0] = 0 or<br>EMCCRx[1] = 1 and<br>access is out of<br>$page^{(6)}$                 | C_READ_ADDR_TO_OUT_SLOW_PS_x <sup>(1)</sup>                     | Integer number of picoseconds      | 0(7)             | integer      |

| Address valid to end<br>of write when<br>EMCCRx[0] = $0^{(5,6)}$                                                                   | C_WRITE_ADDR_TO_OUT_SLOW_PS_x <sup>(1)</sup>                    | Integer number of picoseconds      | 0(7)             | integer      |

| Minimum time that<br>write enable goes<br>low (follows address<br>being driven out).<br>Applies to all<br>writes. <sup>(5,6)</sup> | C_WRITE_MIN_PULSE_WIDTH_PS_ x <sup>(1)</sup>                    | Integer number of picoseconds      | 0(7)             | integer      |

| Address access time<br>for reads when<br>EMCCRx[0] = 1 or<br>EMCCRx[1] = 1 and<br>access is in page <sup>(6)</sup>                 | C_READ_ADDR_TO_OUT_FAST_PS_x <sup>(1)</sup>                     | Integer number of picoseconds      | 0(7)             | integer      |

| Address valid to end<br>of write when<br>EMCCRx[0] = $1^{(5,6)}$                                                                   | C_WRITE_ADDR_TO_OUT_FAST_PS_x <sup>(1)</sup>                    | Integer number of picoseconds      | 0(7)             | integer      |

| Delay inserted<br>before Write Enable<br>goes low if previous<br>access was Read. <sup>(6)</sup>                                   | C_READ_RECOVERY_BEFORE_WR_PS_x <sup>(1,1</sup><br><sup>0)</sup> | Integer number of picoseconds      | 0(7)             | integer      |

#### Table 1: EMC Parameters (Continued)

| Feature /<br>Description                                                                                                                     | Parameter Name                                                   | Allowable Values              | Default<br>Value | VHDL<br>Type |

|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-------------------------------|------------------|--------------|

| Delay inserted<br>before Output<br>Enable goes low if<br>previous access was<br>Write. <sup>(6)</sup>                                        | C_WRITE_RECOVERY_BEFORE_RD_PS_x <sup>(1,1</sup><br><sup>0)</sup> | Integer number of picoseconds | 0(7)             | integer      |

| Maximum width of<br>the memory devices<br>in all of the banks -<br>width of memory bus<br>out to the devices<br><u>AUTOCALCULATED</u><br>(8) | C_MAX_MEM_WIDTH                                                  | 8,16,32                       | 32               |              |

Notes:

- 1. x = values for memory banks 0 to 7

- 2. This design can accommodate up to 8 banks of memory. The address range generics are designated as C\_MEM0\_BASEADDR, C\_MEM1\_BASEADDR, C\_MEM0\_HIGHADDR, C\_MEM1\_HIGHADDR, etc.

- 3. Address range specified by C\_BASEADDR and C\_HIGHADDR must be a power of 2 and >=0x0144 when C\_DEV\_MIR\_ENABLE=1 or >= 0x01F when C\_DEV\_MIR\_ENABLE=0. C\_MEMx\_BASEADDR and C\_MEMx\_HIGHADDR must be a power of 2 and less than or equal to the OPB address space.

- 4. No default value will be specified for C\_BASEADDR and C\_HIGHADDR AND C\_MEMx\_BASEADDR, C\_MEMx\_HIGHADDR to insure that the actual value is set, i.e. if the value is not set, a compiler error will be generated. These generics must be a power of 2 and encompass the memory size for C\_MEMx\_BASEADDR, C\_MEMx\_HIGHADDR.

- 5. Write enable low time is the maximum of C\_WR\_ADDR\_TO\_OUT\_FAST/SLOW\_PS and C\_WR\_MIN\_PULSE\_WIDTH.

- 6. As specified by the memory device data sheet.

- 7. A value must be set for this parameter if the memory type in this bank is asynchronous refer to the memory device data sheet for the correct value.

- 8. This parameter is automatically calculated when using CoreGen, otherwise the user must set this parameter to the maximum value of the C\_MEMx\_WIDTH generics.

- 9. Data-width matching should be set to 0 for memory banks containing Flash memory devices due to the algorithm required for writing Flash memory.

- 10. These parameters only have meaning for Flash memory devices and should be set to 0 for all other memory types.

- 11. This parameter should only be set to 1 under the following conditions:

- Tfpga\_outdelay + Tsetup\_memory + Tboard\_route\_delay < Clock\_period/2</p>

and

Tmemory\_outdelay + Tfpga\_setup + Tboard\_route\_delay < Clock\_period/2

See section "IO Registers" on page 18 for more information on using this parameter.

## **Allowable Parameter Combinations**

The EMC supports up to 8 banks of Synchronous and/or Asynchronous memory. Each bank of memory has it's own independent base address and address range. The address range of a bank of memory is restricted to be a power of 2.

If the desired address range is represented by  $2^n$ , then the *n* least significant bits of the base address must be 0. For example, a memory bank with an addressable range of 16M ( $2^{24}$ ) bytes could have a base address of 0xFF000000 and a high address of 0xFFFFFFF.

A memory bank with an addressable range of 64K (2<sup>16</sup>) bytes could have a base address of 0xABCD0000 and a high address of 0xABCDFFFF.

If C\_DEV\_MIR\_ENABLE = 1, then the minimum address range specified by C\_BASEADDR and C\_HIGHADDR = 0x144. If C\_DEV\_MIR\_ENABLE = 0, then the minimum address range specified by C\_BASEADDR and C\_HIGHADDR=0x01F.

If C\_SYNCH\_MEMORY=1, then C\_SYNCH\_PIPE\_DELAY specifies the pipeline delay of that synchronous memory type. All other timing parameters for that memory bank can remain at the default value of 0. If C\_SYNCH\_MEMORY=0, C\_SYNCH\_PIPE\_DELAY is unused. All other timing parameters for that memory bank must be set to the value specified in the memory device data sheet.

C\_INCLUDE\_DATAWIDTH\_MATCHING must be set to 0 for memory banks containing Flash devices. Each data write to a particular Flash memory location must be preceded by a write command and is therefore not compatible with the implementation of data-width matching in this controller.

C\_INCLUDE\_NEGEDGE\_IOREGS provides no benefit when interfacing to asynchronous memories. Therefore, if there are no synchronous memories in the system, this parameter should be set to 0.

## **EMC I/O Signals**

The I/O signals for the EMC are listed in Table 2.

| Signal Name                    | Interface | I/O | Description                                      |

|--------------------------------|-----------|-----|--------------------------------------------------|

| OPB_Clk                        | OPB       | Ι   | OPB Clock                                        |

| OPB_Rst                        | OPB       | Ι   | OPB Reset                                        |

| OPB_ABus(0:C_OPB_AWIDTH-1)     | OPB       | Ι   | OPB Address Bus                                  |

| OPB_BE(0:C_OPB_DWIDTH/8-1)     | OPB       |     | OPB Byte Enables                                 |

| OPB_DBus(0:C_OPB_DWIDTH-1)     | OPB       | Ι   | OPB Data Bus                                     |

| OPB_RNW                        | OPB       | Ι   | OPB Read, Not Write                              |

| OPB_select                     | OPB       | -   | OPB Select                                       |

| OPB_seqAddr                    | OPB       | Ι   | OPB Sequential Address                           |

| SIn_DBus(0:C_OPB_DWIDTH-1)     | OPB       | 0   | Memory Controller Data Bus                       |

| SIn_errAck                     | OPB       | 0   | Memory Controller Error Acknowledge              |

| SIn_retry                      | OPB       | 0   | Memory Controller Retry                          |

| SIn_toutSup                    | OPB       | 0   | Memory Controller Timeout Suppress               |

| Sln_xferAck                    | OPB       | 0   | Memory Controller Transfer Acknowledge           |

| Mem_DQ_I(0:C_MAX_MEM_WIDTH-1)  | IP Core   | Ι   | Memory Input Data Bus                            |

| Mem_DQ_O(0:C_MAX_MEM_WIDTH-1)  | IP Core   | 0   | Memory Output Data Bus                           |

| Mem_DQ_T(0:C_MAX_MEM_WIDTH-1   | IP Core   | 0   | Memory Output 3-state Signal                     |

| Mem_A(0:C_OPB_AWDITH-1)        | IP Core   | 0   | Memory Address Bus                               |

| Mem_RPN                        | IP Core   | 0   | Memory Reset/Power Down                          |

| Mem_CEN(0:C_NUM_BANKS_MEM-1)   | IP Core   | 0   | Memory Chip Enables (Active Low) <sup>(1)</sup>  |

| Mem_OEN(0:C_NUM_BANKS_MEM-1)   | IP Core   | 0   | Memory Output Enable                             |

| Mem_WEN                        | IP Core   | 0   | Memory Write Enable                              |

| Mem_QWEN(0:(C_MEM_WIDTH/8) -1) | IP Core   | 0   | Memory Qualified Write Enables                   |

| Mem_BEN(0:(C_MEM_WIDTH/8) -1)  | IP Core   | 0   | Memory Byte Enables                              |

| Mem_CE(0:C_NUM_BANKS_MEM-1)    | IP core   | 0   | Memory Chip Enables (Active High) <sup>(1)</sup> |

| Mem_ADV_LDN                    | IP core   | 0   | Memory Advance Burst Address/Load New Address    |

Table 2: EMC I/O Signals

#### Table 2: EMC I/O Signals (Continued)

| Signal Name | Interface | I/O | Description                           |

|-------------|-----------|-----|---------------------------------------|

| Mem_LBON    | IP core   | 0   | Memory Linear/Interleaved Burst Order |

| Mem_CKEN    | IP core   | 0   | Memory Clock Enable                   |

| Mem_RNW     | IP core   | 0   | Memory Read/Write Signal              |

Notes:

1. Most asynchronous memory devices will only use Mem\_CEN. Most synchronous memory devices will use both Mem\_CEN and Mem\_CE. Refer to the device data sheet for correct connection of these signals.

## **Parameter-Port Dependencies**

The width of many of the EMC signals depends on the number of memories in the system and the width of the various data and address busses. In addition, when certain features are parameterized away, the related input signals are unconnected and the related output signals are set to a constant values. The dependencies between the EMC design parameters and I/O signals are shown in Table 3.

#### Table 3: Parameter-Port Dependencies

| Name            | Affects  | Depends         | Relationship Description                                                |

|-----------------|----------|-----------------|-------------------------------------------------------------------------|

| C_OPB_DWIDTH    | OPB_BE   |                 | Number of Byte Enables, width of the                                    |

|                 | OPB_DBus |                 | OPB Data Bus, and the width of the Slave Data Bus all vary based on the |

|                 | SIn_DBus |                 | PLB data width                                                          |

| C_OPB_AWDITH    | OPB_ABUS |                 | Width of the OPB Address Bus and the                                    |

|                 | Mem_A    |                 | width of the Memory Address Bus all vary based on the OPBaddress width  |

| C_MAX_MEM_WIDTH | Mem_DQ_I |                 | Width of the memory interface and                                       |

|                 | Mem_DQ_O |                 | control busses vary based on the maximum data width of the memory       |

|                 | Mem_BEN  |                 | banks                                                                   |

|                 | Mem_QWEN |                 |                                                                         |

| C_NUM_BANKS_MEM | Mem_CEN  |                 | Status signal per Memory Bank                                           |

|                 | Mem_CE   |                 | Chip Enable (low) per Memory Bank                                       |

|                 | Mem_OEN  |                 | Chip Enable (high) per Memory Bank                                      |

|                 |          |                 | Output Enable per Memory Bank                                           |

| I/O Signals     |          |                 |                                                                         |

| OPB_ABus        |          | C_OPB_AWIDTH    | Width varies with the width of the OPB Address Bus                      |

| OPB_BE          |          | C_OPBDWIDTH     | Width varies with the width of the OPB Data Bus                         |

| Mem_DQ_I        |          | C_MEM_WIDTH     | Width varies with the width of the memory specified                     |

| Mem_DQ_O        |          | C_MEM_WIDTH     | Width varies with the width of the memory specified                     |

| Mem_A           |          | C_OPB_AWDITH    | Width varies with the width of the OPB Address Bus                      |

| Mem_CEN         |          | C_NUM_BANKS_MEM | Width varies with the width of the number of memory banks specified     |

| Mem_OEN         |          | C_NUM_BANKS_MEM | Width varies with the width of the number of memory banks specified     |

#### Table 3: Parameter-Port Dependencies (Continued)

| Name     | Affects | Depends         | Relationship Description                                            |

|----------|---------|-----------------|---------------------------------------------------------------------|

| Mem_QWEN |         | C_MEM_WIDTH     | Width varies with the width of the<br>memory specified              |

| Mem_BEN  |         | C_MEM_WIDTH     | Width varies with the width of the memory specified                 |

| Mem_CE   |         | C_NUM_BANKS_MEM | Width varies with the width of the number of memory banks specified |

## **EMC Address Map and Register Descriptions**

### **EMC Address Map**

The EMC contains addressable control registers for each memory bank which sets timing for write operations. The base address for these registers is set in the parameter C\_BASEADDR. Table 4 shows all of the EMC control registers and their addresses when the EMC has been parameterized to support all 8 memory banks. Control registers are only present in the design for memory banks that are used.

#### Table 4: EMC Control Registers

| Register Name                  | OPB Address       | Access     |

|--------------------------------|-------------------|------------|

| MEM0 Control Register (EMCCR0) | C_BASEADDR + 0x00 | Read/Write |

| MEM1 Control Register (EMCCR1) | C_BASEADDR + 0x04 | Read/Write |

| MEM2 Control Register (EMCCR2) | C_BASEADDR + 0x08 | Read/Write |

| MEM3 Control Register (EMCCR3) | C_BASEADDR + 0x0C | Read/Write |

| MEM4 Control Register (EMCCR4) | C_BASEADDR + 0x10 | Read/Write |

| MEM5 Control Register (EMCCR5) | C_BASEADDR + 0x14 | Read/Write |

| MEM6 Control Register (EMCCR6) | C_BASEADDR + 0x18 | Read/Write |

| MEM7 Control Register (EMCCR7) | C_BASEADDR + 0x1C | Read/Write |

The EMC can be parameterized to contain a Module Identification Register (MIR). This register has an independent address located at a calculated offset of 0x140. Therefore, if C\_DEV\_MIR\_ENABLE is set equal to "1" then the MIR is located atC\_BASEADDR + 0x00000140.

#### Table 5: EMC Module Identification Register

| Register Name                            | OPB Address        | Access |

|------------------------------------------|--------------------|--------|

| EMC Module Identification Register (MIR) | C_BASEADDR + 0x140 | Read   |

The EMC supports up to 8 banks memory. Each bank of memory has it's own independent base address and address range. The address range of a bank of memory is restricted to be a power of 2. If the desired address range is represented by  $2^n$ , then the *n* least significant bits of the base address must be 0. For example, a memory bank with an addressable range of 16M ( $2^{24}$ ) bytes could have a base address of 0xFF000000 and a high address of 0xFFFFFFF. A memory bank with an addressable range of 64K ( $2^{16}$ ) bytes could have a base address of 0xABCD0000 and a high address of 0xABCDFFFF.

The addresses for each bank of memory are shown in Table 6.

| Memory | Base Address    | High Address    | Access     |

|--------|-----------------|-----------------|------------|

| Bank 0 | C_MEM0_BASEADDR | C_MEM0_HIGHADDR | Read/Write |

| Bank 1 | C_MEM1_BASEADDR | C_MEM1_HIGHADDR | Read/Write |

| Bank 2 | C_MEM2_BASEADDR | C_MEM2_HIGHADDR | Read/Write |

| Bank 3 | C_MEM3_BASEADDR | C_MEM3_HIGHADDR | Read/Write |

| Bank 4 | C_MEM4_BASEADDR | C_MEM4_HIGHADDR | Read/Write |

| Bank 5 | C_MEM5_BASEADDR | C_MEM5_HIGHADDR | Read/Write |

| Bank 6 | C_MEM6_BASEADDR | C_MEM6_HIGHADDR | Read/Write |

| Bank 7 | C_MEM7_BASEADDR | C_MEM7_HIGHADDR | Read/Write |

#### Table 6: EMC Memory Banks

## **EMC** Control Register (EMCCR)

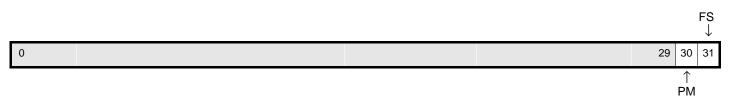

The EMC Control Register is shown in Figure 1. Table 7 shows the Control Register bit definitions.

Figure 1: EMC Control Register

#### Table 7: EMC Control Register Bit Definitions

| Bit(s) | Name | Core Access | Reset Value         | Description                                                                                                                                                                                                                                      |

|--------|------|-------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 - 29 |      |             | Reserve             | ed                                                                                                                                                                                                                                               |

| 30     | РМ   | Read/Write  | ·0 <sup>,</sup> (1) | <ul> <li>Page Mode Enable. Determines whether or not in-page detection logic is created with a corresponding decrease in read access time for in-page reads.</li> <li>'0' - Page Mode is Disabled</li> <li>'1' - Page Mode is Enabled</li> </ul> |

| 31     | FS   | Read/Write  | , <sup>0</sup> ,(1) | <ul> <li>Fast/Slow Mode Enable. Determines the number of Wait States required based on the input timing parameters.</li> <li>'0' - Slow Access Time</li> <li>'1' - Fast Access Time</li> </ul>                                                   |

The functionality of the EMC Control Register bits is described in Table 8. Note that the bits in this register really only have meaning for FLASH memory devices.

| Read/Write | PM Enable | FS Enable | Function                       |

|------------|-----------|-----------|--------------------------------|

| Read       | 0         | 0         | Slow access                    |

|            | 0         | 1         | Fast access                    |

|            | 1         | Х         | Fast in page, slow not in page |

| Write      | Х         | 0         | Slow access                    |

|            | Х         | 1         | Fast access                    |

Table 8: EMC Control Register Bit Functionality

## Module Identification Register (MIR)

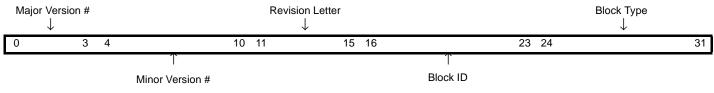

The MIR is actually located within the OPB IPIF. This register is read-only and reflects the current IPIF version as well as the Block ID specified by the C\_DEV\_BLK\_ID parameter. Figure 2 shows the MIR and Table 9 details the MIR bit definitions. Note that the only field that is variable is the Block ID field.

Figure 2: Module Identification Register

Table 9: Module Identification Register (MIR) Bit Definitions

| Bit(s)  | Name            | Core Access | Reset Value  | Description                                                                                      |

|---------|-----------------|-------------|--------------|--------------------------------------------------------------------------------------------------|

| 0 - 3   | Major Version # | Read        | 0010         | OPBIPIF Major Version Number = 2                                                                 |

| 4 - 10  | Minor Version # | Read        | 000000000    | OPBIPIF Minor Version Number = 0                                                                 |

| 11-15   | Revision Letter | Read        | 00000        | OPBIPIF Revision Letter = 00000(a)                                                               |

| 16 - 23 | Block ID        | Read        | C_DEV_BLK_ID | Block Identification Number. The value<br>read is an echo of the input parameter<br>C_DEV_BLK_ID |

| 24 - 31 | Block Type      | Read        | 0000001      | OPBIPIF Block Type = 1                                                                           |

## **Memory Data Types and Organization**

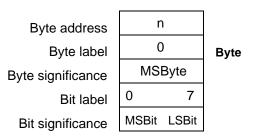

Memory can be accessed through the EMC as one of three types: byte (8 bits), halfword (2 bytes), or word (4 bytes). From the point of view of the OPB, data is organized as big-endian. The bit and byte labeling for the big-endian data types is shown below in Figure 3.

| Byte address      | n     | n+1 | n+2 | n+3 | n+4 | n+5 | n+6 | n+7   | Double |

|-------------------|-------|-----|-----|-----|-----|-----|-----|-------|--------|

| Byte label        | 0     | 1   | 2   | 3   | 4   | 5   | 6   | 7     | Word   |

| Byte significance | MSB   |     |     |     |     |     |     | LSB   |        |

| Bit label         | 0     |     |     |     |     |     |     | 63    |        |

| Bit significance  | MSBit |     |     |     |     |     |     | LSBit |        |

|                   |       |     |     |     |     |     |     |       |        |

| Byte address      | n      | n+1 | n+2 | n+3    |      |

|-------------------|--------|-----|-----|--------|------|

| Byte label        | 0      | 1   | 2   | 3      | Word |

| Byte significance | MSByte |     |     | LSByte |      |

| Bit label         | 0      |     |     | 31     |      |

| Bit significance  | MSBit  |     |     | LSBit  |      |

| 0                 |        |     |     |        |      |

| Byte address      | n      | n+1    |          |

|-------------------|--------|--------|----------|

| Byte label        | 0      | 1      | Halfword |

| Byte significance | MSByte | LSByte |          |

| Bit label         | 0      | 15     |          |

| Bit significance  | MSBit  | LSBit  |          |

Figure 3: Big-Endian Data Types

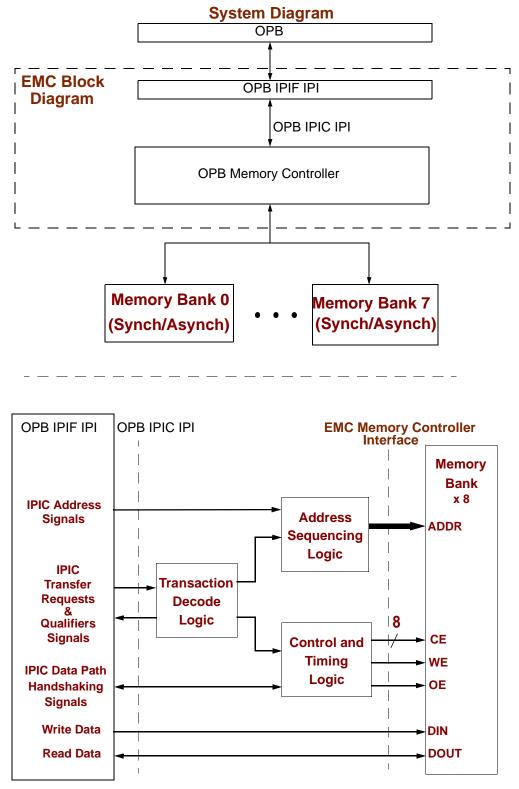

## **EMC Block Diagram**

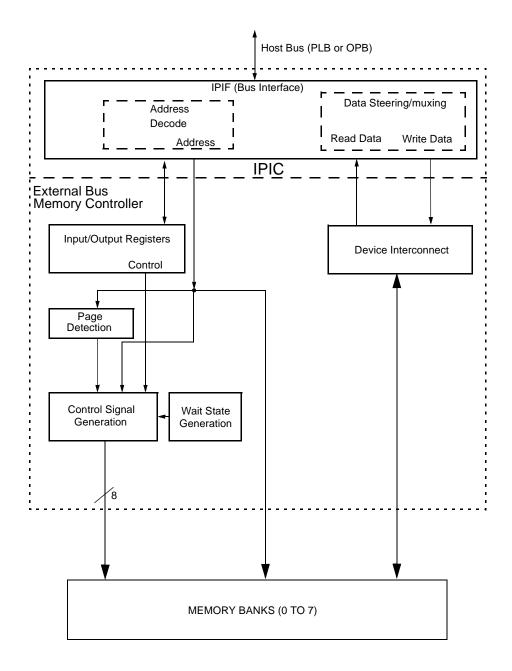

The top-level block diagram for the EMC is shown in Figure 4. The detailed block diagram of the EMC is found in Figure 5.

Figure 4: EMC Top-level Block Diagram

Figure 5 depicts the Memory Control Block Diagram implemented in the EMC.

Figure 5: EMC Memory Control Block Diagram

# **Memory Controller Operation**

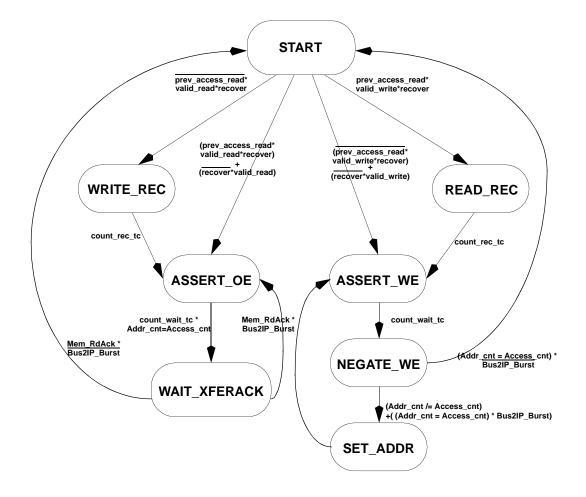

## Memory Controller State Machine

The memory controller state machine is a single state machine but is depicted in two separate diagrams, one for asynchronous memories and one for synchronous memories, to improve readability. Figure 6 depicts the memory controller state machine when the addressed memory bank is an asynchronous memory type.

Figure 6: EMC Memory Control State Machine for Asynchronous Memories

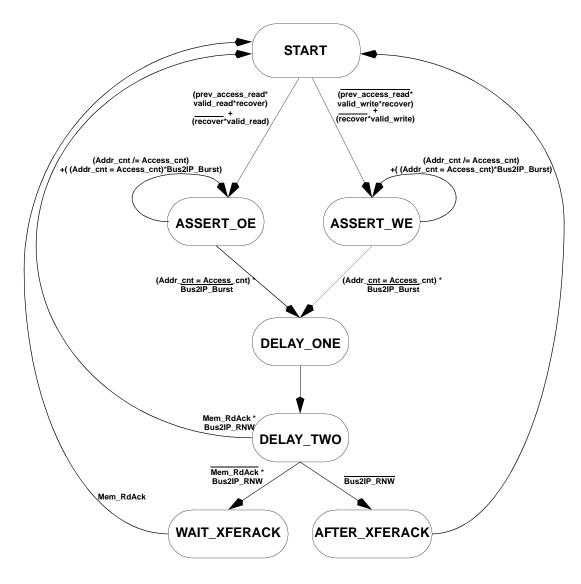

#### Figure 7: EMC Memory Control State Machine for Synchronous Memories with 2 clock Pipeline Delay

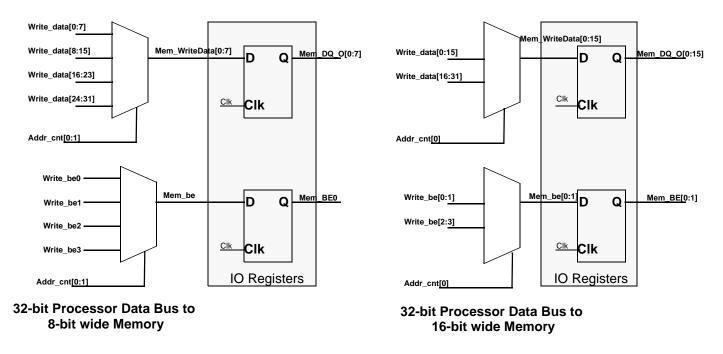

#### Data-Width Matching

Data-width matching is the term used to describe the EMC operation of performing multiple memory accesses to match the width of the memory bank's data bus to the width of the **OPBPLB** data bus. When C INCLUDE DATAWIDTH MATCHING=1 for a particular memory bank and the width of the memory bank is less than the width of the OPB data bus, multiple accesses are made to the memory bank so that the OPB data bus is fully utilized. An address counter within the EMC is used to provide the correct memory addresses. The address counter is controlled by the state machine and is incremented as each transaction completes.

For example, if the memory bank being addressed is 8 bits wide, then 4 writes to or reads from that memory will be performed in order that the full 32 bits of the OPB data bus are used. For a write cycle, the first byte of the OPBdata bus (bits 0 -7) is written to the memory on bits 0-7 of the memory data bus, then the second byte (bits 8-15) on bits 0-7 of the memory bus, and so on. The write data multiplexing is shown in Figure 8 for a 32-bit processor data bus to illustrate the basic concept. This can easily be extended for a 64-bit processor data bus, but is not shown in this document.

#### Figure 8: Data-width matching for Write operations (32-bit Processor Data bus)

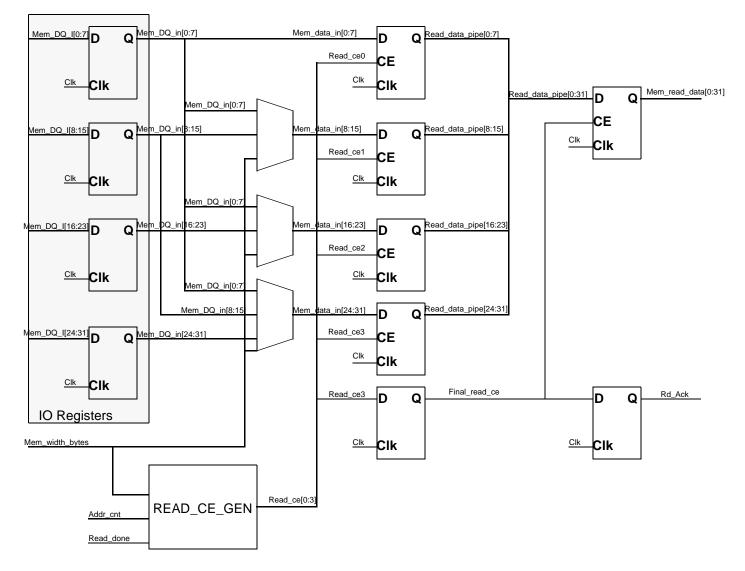

For a read cycle, the data read on bits 0-7 of the memory bus is stored as bits 0-7 of the OPBdata bus for the first byte, then the data read on bits 0-7 of the memory bus is stored as bits 8-15 OPBdata bus for the second byte and so on until all bytes have been read. Then all bytes are presented to the OPBdata bus and the read acknowledge is generated. This is shown in Figure 9 for a 32-bit wide processor data bus to illustrate the basic concept. This can easily be extended for a 64-bit processor data bus, but is not shown in this document. The signal Mem\_width\_bytes specifies the data-width of the memory bank currently being accessed.

Figure 9: Data-width matching for Read operations (32-bit data bus)

The READ\_CE signals are generated according to Table 10 for a 32-bit processor data bus to illustrate the basic logic. This can easily be extended for a 64-bit processor data bus, but is not shown in this document. :

|                 | · · · · · · · · · · · · · · · · · · · |            | ······     |            |            |

|-----------------|---------------------------------------|------------|------------|------------|------------|

| Mem_width_bytes | Addr_cnt                              | Read_ce(0) | Read_ce(1) | Read_ce(2) | Read_ce(3) |

| 8               | 00                                    | Read_done  | 0          | 0          | 0          |

|                 | 01                                    | 0          | Read_done  | 0          | 0          |

|                 | 10                                    | 0          | 0          | Read_done  | 0          |

|                 | 11                                    | 0          | 0          | 0          | Read_done  |

| 16              | 0                                     | Read_done  | Read_done  | 0          | 0          |

|                 | 1                                     | 0          | 0          | Read_done  | Read_done  |

| 32              | 0                                     | Read_done  | Read_done  | Read_done  | Read_done  |

| Table 10: READ_CE Generation (32-bit processor data bus) |

|----------------------------------------------------------|

|----------------------------------------------------------|

#### **OPB External Memory Controller (EMC)**

Since data-width matching writes to memories by performing multiple write cycles to the memory, each time writing a portion of the OPBdata, data-width matching does not work properly when writing to FLASH memories of widths smaller than the OPBdata bus. This is due to the fact that a write to memory location must be preceded by a write of the WRITE command to that address. In the case of data-width matching, multiple WRITE commands would be written to multiple addresses, followed by the writing of the actual data which violates the algorithm of writing to FLASH memory locations. Therefore, C\_INCLUDE\_DATAWIDTH\_MATCHING should be set to 0 for memory banks containing FLASH devices.

The data bus to/from the memory banks uses big-endian bit labeling (i.e. bit 0 is MSB) and is sized according to the C\_MAX\_MEM\_WIDTH parameter. Memories that have smaller widths should connect to this bus starting at bit 0 (MSB - big endian bit labeling). For example, if 3 memory banks are present of sizes 8, 16, and 32 bits, the 8 bit wide memory bank should connect to bits 0-7 of the memory data bus, the 16 bit wide memory bank should connect to bits 0 - 15 of the memory data bus, and the 32 bit wide memory should connect to bits 0 - 31 of the memory data bus.

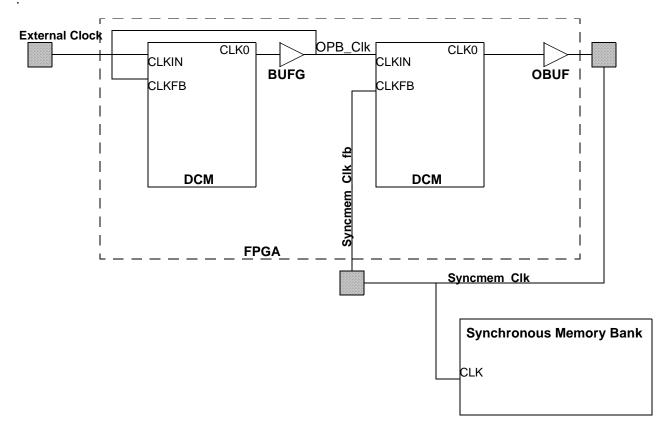

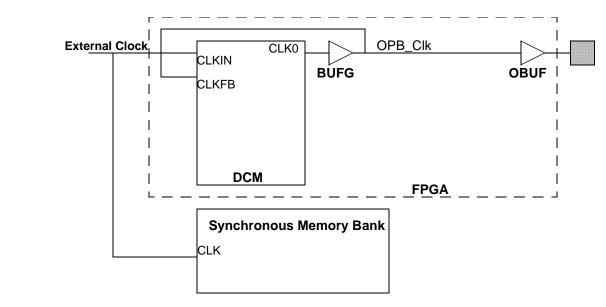

## **IO Registers**

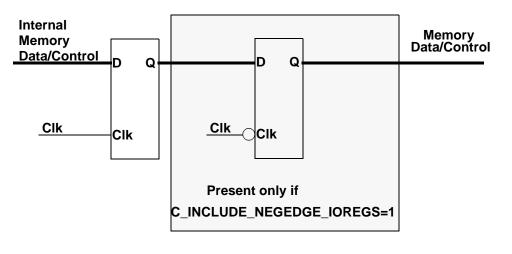

Registers are used on all signals to and from the memory banks to provide consistent timing on the memory interface. The IO registers present in the design depend upon the setting of the C\_INCLUDE\_NEGEDGE\_IOREGS. All signals output to the memory banks are registered on the rising edge of the system clock. If C\_INCLUDE\_NEGEDGE\_IOREGS = 1, the signals are registered again on the falling edge of the system clock as shown in Figure 10 and can be used at lower clock frequencies to provide setup and hold to synchronous memories. This parameter can be used for asynchronous memories as well or if there is a mixture of synchronous and asynchronous memories in the system. However, if there are only asynchronous memories in the system, setting this parameter to 1 provides no value, and is therefore recommended to be set to 0.

Figure 10: EMC Output Registers

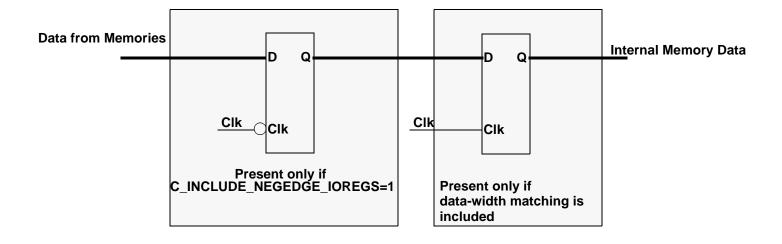

If C\_INCLUDE\_NEGEDGE\_IOREGS = 1, the data input from the memories is clocked into the FPGA on the falling edge of the clock. This can be used at lower clock frequencies to obtain setup and hold from synchronous memories in the system. If data width matching is included for any of the memory banks, the data is again registered on the rising edge of the clock before going into the data width matching multiplexors. These registers are not included if data-width matching is not needed for any of the memory banks. This is shown in Figure 11 and can be used at lower clock frequencies to provide setup and hold from synchronous memories. This parameter can be used for asynchronous memories as well or if there is a mixture of synchronous and asynchronous memories in the system. However, if there are only asynchronous memories in the system, setting this parameter to 1 provides no value, and is therefore recommended to be set to 0.

Figure 11: EMC Input Registers

NOTE: C\_INCLUDE\_NEGEDGE\_IOREGS should only be set to 1 if the output delay from the FPGA plus the setup requirement of the synchronous memories in the system plus the board route delay is less than half the clock period AND the output delay from the synchronous memories in the system plus the FPGA setup requirement plus the board route delay is less than half the clock period.

- Tfpga\_outdelay + Tsetup\_memory + Tboard\_route\_delay < Clock\_period/2</li>

- · AND

- Tmemory\_outdelay + Tfpga\_setup + Tboard\_route\_delay < Clock\_period/2</li>

## **OPB Timing Diagrams**

The following timing diagrams show various OPB bus transactions and the resulting memory accesses. Timing diagrams are not shown for all memory widths, but just a sampling to provide an example of how various memory widths are supported.

#### **OPB Accesses to 8-bit SRAM**

### OPB Single Write followed by Single Read to 8-bit SRAM

|                | 1.0us                                         | 1.1us            | 1.2us                                          | 1.3us                                   | 1.4us                     | 1.5us                      | 1.6us                     |

|----------------|-----------------------------------------------|------------------|------------------------------------------------|-----------------------------------------|---------------------------|----------------------------|---------------------------|

| Cycles         | 123456791011121                               | 3141516171819202 | 12223 2425262728293                            | 031323334353637                         | 38 39 40 41 42 43 44 4546 | 47 48 49 50 51 52 53 54 55 | 5657 58 59 60 61 62 63 64 |

| Opb_rst        |                                               |                  |                                                |                                         |                           |                            |                           |

| Opb_clk        |                                               |                  |                                                |                                         |                           |                            |                           |

| Opb_select     |                                               |                  |                                                |                                         |                           |                            |                           |

| Opb_seqaddr    |                                               |                  |                                                |                                         |                           |                            |                           |

| Opb_rnw        |                                               |                  |                                                |                                         |                           |                            |                           |

| Opb_abus[0:31] | $\chi$                                        |                  |                                                | 30000008                                | ····                      |                            |                           |

| Opb_be[0:3]    |                                               |                  | <u>-                                      </u> | + + + + + + + + + + + + + + + + + + + + | · · · · · · · · · ·       |                            |                           |

| Opb_dbus[0:31] |                                               | <b>9ABCDEFA</b>  |                                                | X                                       | 00                        | 000000                     |                           |

| Sln_xferack    |                                               |                  |                                                |                                         |                           |                            | /                         |

|                |                                               |                  |                                                |                                         |                           |                            |                           |

| Mem_a[0:31]    | I X 3000008 X3                                | 300000930        | 00000AX30000                                   | 000B(1 3000                             | 00008 1 30000             |                            | 3000000B(13000            |

| Mem_ben        |                                               |                  |                                                |                                         |                           |                            |                           |

| Mem_cken       |                                               | 1 1 1 1 1 1 1 1  | 1 1 1 1 1 1 1 1 1                              | 1 1 1 1 1 1 1 1                         |                           |                            |                           |

| Mem_ce         |                                               |                  |                                                |                                         |                           |                            |                           |

| Mem_cen        |                                               |                  |                                                |                                         |                           |                            |                           |

| Mem_wen        |                                               |                  |                                                |                                         |                           |                            |                           |

| Mem_oen        |                                               |                  |                                                |                                         |                           |                            |                           |

| Mem_dq[0:7]    | <u>, , , , , , , , , , , , , , , , , , , </u> | BGX              |                                                | λ                                       | X9AX B                    |                            |                           |

Figure 12: OPB Single Write/Single Read to 8-bit SRAM

#### **OPB Accesses to 16-bit SRAM**

### OPB Single Write followed by Single Read to 16-bit SRAM

|                | 1.0us  1.1us  1.2us  1.3us                                                                    |

|----------------|-----------------------------------------------------------------------------------------------|

| Cycles         | 1 2 3 4 5 6 7 9 101112131415161718192021222324252627282930313233343556573839                  |

| Opb_rst        |                                                                                               |

| Opb_clk        |                                                                                               |

| Opb_select     |                                                                                               |

| Opb_seqaddr    |                                                                                               |

| Opb_rnw        |                                                                                               |

| Opb_abus[0:31] | $\chi$                                                                                        |

| Opb_be[0:3]    |                                                                                               |

| Opb_dbus[0:31] |                                                                                               |

| Sln_xferack    |                                                                                               |

|                |                                                                                               |

| Mem_a[0:31]    | <u>        X     3000008     X   300000A   X       3000008       X   300000A   X   300000</u> |

| Mem_ben[0:1]   |                                                                                               |

| Mem_cken       |                                                                                               |

| Mem_ce         |                                                                                               |

| Mem_cen        |                                                                                               |

| Mem_wen        |                                                                                               |

| Mem_oen        |                                                                                               |

| Mem_dq[0:15]   |                                                                                               |

Figure 13: OPB Single Write/Single Read to 16-bit SRAM

## **OPB Accesses to 32-bit SRAM**

### OPB Single Write followed by Single Read to 32-bit SRAM

|                | ,  s     | 950r     | ns <sub>i</sub>     |        |          | 1.00     | us     |        |        | 1.Oʻ   | 5us      |        |        | 1.1    | 0us      |        |        | 1.1    | 1 <mark>5</mark> us | ì i      |                 | 1.     | 20u        | s,        |

|----------------|----------|----------|---------------------|--------|----------|----------|--------|--------|--------|--------|----------|--------|--------|--------|----------|--------|--------|--------|---------------------|----------|-----------------|--------|------------|-----------|

| Cycles         | 1        | 2        | 3                   | 4      | 5        | 6        | 7      | 9      | 10     | 11     | 12       | 13     | 14     | 15     | 16       | 17     | 18     | 19     | 20                  | 21       | 22              | 23     | 24         | 25        |

| Opb_rst        | 1        | 1        | 1                   |        |          | 1        | 1      | 1      | 1      |        | I<br>I   |        |        |        | 1        |        |        |        |                     | 1        | 1               |        |            |           |

| Opb_clk        | /        |          | $\overline{\frown}$ | $\sim$ | $\frown$ | $\sim$   | $\sim$ | $\sim$ | $\sim$ | $\sim$ | $\sim$   | $\sim$ | $\sim$ | $\sim$ | $\sim$   | $\sim$ | $\sim$ | $\sim$ | $\sim$              | $\frown$ | $\sim$          | $\sim$ | $\sim$     | $\sim$    |

| Opb_select     | 1        | Ì        | 1                   |        |          | i i      | 1      | 1      | 1      |        | 1        |        |        |        | 1        |        |        |        |                     | 1        | 1               |        |            | <u>`\</u> |

| Opb_seqaddr    | i        |          | 1                   |        |          |          |        | 1      | 1      |        |          |        |        |        |          |        |        |        |                     | i        |                 |        |            | 1         |

| Opb_rnw        | ÷۸       | <br>     | 1                   |        |          | 1        | 1      | 1      | 1      |        |          |        |        |        | 1        |        |        |        |                     | 1        | 1               |        |            | ίλ        |

| Opb_abus[0:31] | ĽΧ       | 1        | 1                   |        |          | 1        | <br>   | <br>   | <br>   |        | 30       | 000    | 008    |        | <br>     |        |        |        |                     | <br>     | 1               |        |            | ΪX        |

| Opb_be[0:3]    | 1        | -        | -                   |        |          | -        | <br>   | <br>   | <br>   |        |          |        |        |        | <br>     |        |        |        |                     | 1        |                 |        |            | X         |

| Opb_dbus[0:31] |          | 1        | 1                   |        | 1234     | 4567     | 78     | -      | -      |        | X        |        |        |        | ¦ (      | 2000   | 0000   | 0      |                     | 1        | 1               |        | $\bigcirc$ | $\square$ |

| Sln_xferack    | <u>\</u> | i        | i                   |        |          |          |        |        |        | $\sum$ | <u> </u> |        |        |        | 1        |        |        |        |                     | 1        | i               |        | $\frown$   |           |

|                | i.       | i        |                     |        |          | 1        | 1      | 1      | 1      |        |          |        |        |        |          |        |        |        |                     |          | i               |        |            | (         |

| Mem_a[0:31]    | 1        | 1        | ÷χ                  |        |          | 1        | 1      | 1      | 1      |        | <br>     |        | 3      | 8000   | 000      | 8      |        |        |                     | <br>     | 1               |        |            |           |

| Mem_ben[0:3]   | -        | <br>     | 1                   |        |          | +        | . (    | þ      | I      |        |          | L F    | r i    |        | I        |        |        |        | 0                   | I        | 1               |        |            |           |

| Mem_cken       | 1        | 1        | 1                   |        |          | 1        | 1      | 1      | 1      |        | I<br>I   |        |        |        | 1        |        |        |        |                     | 1        | 1               |        |            |           |

| Mem_ce         | 1        | 1        | 1                   |        |          |          | 1      |        |        |        |          |        |        |        | 1        |        |        |        |                     | 1        | 1               |        |            |           |

| Mem_cen        | 1        | 1        | 1                   |        |          | i        |        |        |        |        |          |        |        |        | 1        |        |        |        |                     | 1        | i               |        |            |           |

| Mem_wen        | 1        | 1        | 1                   |        |          |          | 1      | 1      | 1      |        | 1        |        |        |        |          |        |        |        |                     |          | 1               |        |            | 1         |

| Mem_oen        | 1        | 1        | 1                   |        |          | 1        | 1      | 1      | 1      |        | 1        |        |        |        | <u>-</u> |        |        |        |                     | 1        |                 |        |            |           |

| Mem_dq[0:31]   |          | <u> </u> | <u> </u>            | X      |          | <u> </u> | 1234   | 1567   | 8      |        |          |        |        | zzz    | ZZZ      | zz     |        |        | 123                 | 4567     | <del>/</del> 8χ |        |            |           |

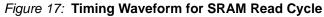

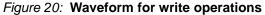

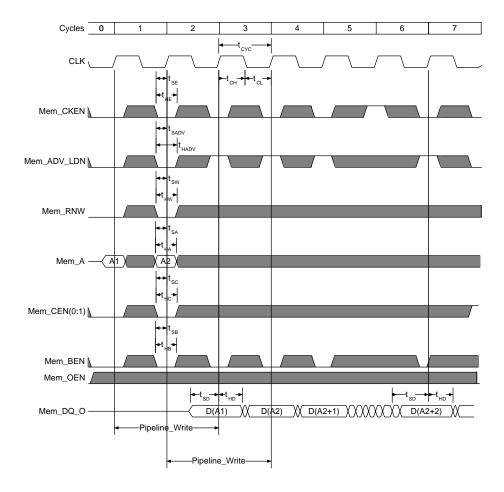

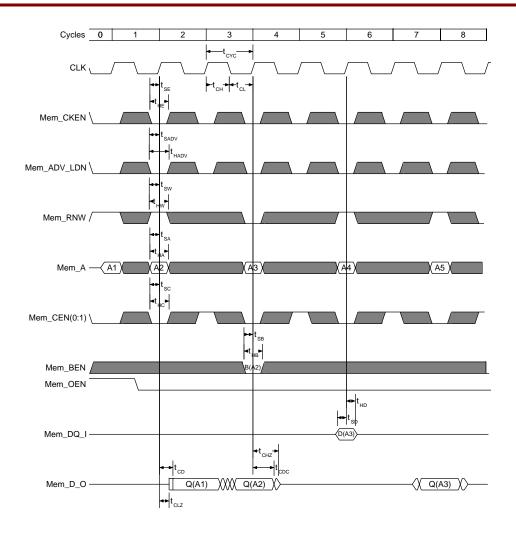

### **OPB Accesses to 32-bit Pipeline ZBT**

#### OPB Single Write followed by Single Read to 32-bit Pipeline ZBT

|                | 940ns      | s  9     | 60ns | 980ı     | ns       | 1,004    | s  1,0   | )2us     | 1,0      | 4us      | 1 <sub>1</sub> 064 | s,  1;   | 08ys  | 1,10     | )us                       | 1,12y      | s  1,14      |

|----------------|------------|----------|------|----------|----------|----------|----------|----------|----------|----------|--------------------|----------|-------|----------|---------------------------|------------|--------------|

| Cycles         | 1          | 2        | 3    | 4        | 5        | 6        | 7        | 9        | 10       | 11       | 12                 | 13       | 14    | 15       | 16                        | 17         | 18           |

| Opb_rst        | 1          | 1        | 1    | 1        | 1        | 1        | 1 1      |          | 1        | 1        | 1                  |          | 1     | 1        | 1                         | 1          |              |

| Opb_clk        |            |          |      |          | $\frown$ |          |          | $\frown$ | $\frown$ |          |                    | $\frown$ |       | $\frown$ |                           | $\square$  |              |

| Opb_select     | 1          | i<br>i   | 1    | 1        | 1        | 1        | 1 1      |          | 1        | 1        | 1                  | 1        | 1     | 1        | 1                         | 1          | <u> </u> /   |

| Opb_seqaddr    | i -        | <u>i</u> | i    | <u>i</u> |          | <u>i</u> | i i      |          |          | <u>i</u> | i                  |          | i     |          | <u>i</u>                  | <u>i</u>   | i i          |

| Opb_abus[0:31] | ÷χ         | 1        | 1    | 1        | 1        | 1        | · · ·    | 3        | 0000     | 800      | 1                  |          | 1     | 1        | 1                         | 1          | <u>΄</u> χ   |

| Opb_rnw        | <u>+</u> \ | 1        | 1    | 1        | I<br>I   | 1        |          |          |          | 1        | <br>               | 1        | <br>  | 1        | 1                         | 1          | <u> </u>     |

| Opb_be[0:3]    | +          | -        |      | +        | <br>     | +        | + +      |          | <br>     | -        | 1                  |          | +     |          | 1                         | -          | : Х          |

| Opb_dbus[0:31] | XX         | 1        |      | 9AB      | ¢DEF     | A        | , ,      |          | X        | 1        | 1                  | 000      | 0000c | )        | 1                         | 1          | X X          |

| Sln_xferack    | 1          | i        | 1    | 1        | 1        | 1        | <u> </u> |          | <u> </u> | 1        | 1                  | 1        | 1     | 1        | 1                         | 1          |              |

|                | i.         | į        | 1    | 1        |          |          |          |          |          | 1        | i                  | i        | 1     | 1        | i                         | i          | i i          |

| Mem_a[0:31]    | <u> </u>   | 1        | X    | 1        | <br>     | 1        |          |          | <br>     | 3        | 20000              | 08       | 1     | 1        | 1                         | 1          | 1 1          |

| Mem_ben[0:3]   |            |          | 1    | 1        | I        | 1        | · · ·    |          | I        | 1        | 1                  | 1        | 1     |          | <br>                      | !          |              |

| Mem_cken       | 1          |          | 1    | 1        | I<br>I   | 1        | · ·      |          | I<br>I   | 1        | 1                  |          | 1     | I<br>    | <br>                      | <br>       |              |

| Mem_ce         | 1          | 1        | 1    |          | /        | 1        |          | <u> </u> | 1        | 1        | 1                  | 1        | /     | 1        | 1                         | 1          | 1 İ          |

| Mem_cen        | 1          |          | 1    | 1        |          | i        | i i      |          |          |          |                    |          | i     | i        | 1                         | i i        |              |

| Mem_wen        | 1          | 1        | 1    | 1        |          | ;        |          |          | 1        | 1        | 1                  | 1        | 1     | 1        | 1                         | 1          |              |

| Mem_oen        | 1          | 1        | 1    | 1        | 1        | 1        | 1 1      |          | 1        | 1        | 1                  | 1        | I     | \        | 1                         | 1          | <u>ا ا ا</u> |

| Mem_dq[0:31]   |            | 1        |      | 000000   | 1        | 9AB      | ¢DEF;    | A        | X        | 1        | ZZ                 | ZZZZ     | zz    | 1        | <u>΄</u> χ <sub>9</sub> , | +<br>\BCDE | FAX          |

#### Figure 15: OPB Single Write/Single Read to 32-bit Pipeline ZBT

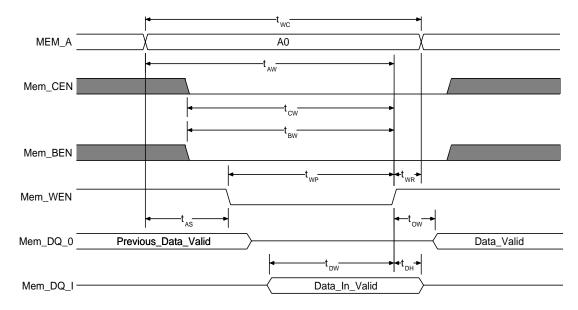

#### **OPB Accesses to 32-bit Flowthrough ZBT**

#### OPB Single Write followed by Single Read to 32-bit Flowthrough ZBT

|                | 940ns        | s  96     | 60ns      | 980     | ns               | 1,00u     | s  1,0   | )2us | 1.04     | lus      | 1,064s   | s,  1,(  | 08us     | 1,10     | )us              | 1,12u      | s  1,14       |

|----------------|--------------|-----------|-----------|---------|------------------|-----------|----------|------|----------|----------|----------|----------|----------|----------|------------------|------------|---------------|

| Cycles         | 1            | 2         | 3         | 4       | 5                | 6         | 7        | 9    | 10       | 11       | 12       | 13       | 14       | 15       | 16               | 17         | 18            |

| Opb_rst        | 1            | 1         | 1         | 1       | I<br>I           | 1         | I<br>I   |      | I<br>I   | I<br>I   | I<br>I   |          | I<br>I   |          | <br>             | <br>       |               |

| Opb_clk        | /            | $\square$ | $\square$ |         | $\frown$         | $\square$ | $\frown$ |      | $\frown$ | $\frown$ | $\frown$ | $\frown$ | $\frown$ | $\frown$ | $\square$        | $\square$  | /             |

| Opb_select     | 1            | 1         | 1         | 1       | 1                | 1         |          |      | 1        | 1        | 1        |          | 1        | 1        | 1                | 1          | $    \rangle$ |

| Opb_seqaddr    |              | 1         | 1         | 1       |                  |           |          |      |          | 1        | 1        |          | 1        |          |                  |            | i i           |

| Opb_rnw        | , <u>†</u> \ | 1         | 1         | 1       | 1                | 1         | 1        |      |          | 1        | 1        |          | 1        | 1        | 1                | 1          | <u> </u>      |

| Opb_abus[0:31] | ЦХ           | 1         |           | 1       | I                | 1         |          | 3    | 0000     | 008      | 1        |          | I        |          | !                |            | X X           |

| Opb_be[0:3]    | +            | 1         | -         | -       | <br>             | 1         |          |      | I<br>I   | 1        | 1        |          | I        |          | 1                | -          | X             |

| Opb_dbus[0:31] | XX           | 1         | -         | 9AB     | ¢DEF             | A         | 1        |      | X        | 1        | 1        | 0000     | 20000    |          | 1                | 1          |               |

| Sln_xferack    | 1            | 1         | i         | 1       |                  | i         |          |      | <u>i</u> |          | 1        |          | 1        | 1        | i                | i          |               |

|                | i.           | i         | 1         | 1       |                  | i         | i        |      | i        | 1        | I        |          | i        |          | i                | i          | i i           |

| Mem_a[0:31]    |              | 1         | χ         | 1       | <br>             | 1         | r        |      | <br>     | 30       | 00000    | 08       | <br>     |          | 1                | 1          | 1 1           |

| Mem_ben[0:3]   | 1            | 1         |           | 1       | I                | 1         |          |      | <br>     | 1        | 1        |          | I        |          |                  |            |               |

| Mem_cken       | 1            | 1         | 1         | 1       | I<br>I           | 1         | 1        |      | I<br>I   | 1        | 1        |          | I<br>I   |          | 1                | 1          | 1 1           |

| Mem_ce         | 1            | i         | 1         | i .     | ζ                | 1         |          |      | 1        | 1        | 1        |          | /        |          | 1                | <u>x</u>   | 1             |

| Mem_cen        | !            | 1         |           | 1       |                  |           |          |      |          |          | <br>;    |          | I        |          | i<br>I           | i          |               |

| Mem_wen        | 1            | 1         | 1         | 1       | <u> </u>         | /         | 1        |      | 1        | 1        | 1        |          | 1        | 1        | 1                | 1          | 1 1           |

| Mem_oen        | 1            | 1         | 1         | 1       | 1                | 1         |          |      | 1        | 1        | I        |          | I        | \        | 1                | 1          |               |

| Mem_dq[0:31]   |              | 1         | 1         | 1000000 | λ <sup>1</sup> χ | 9AB       | DEF.     | A    | X        | <br>     | ZZ       | ZZZZ     | zz       |          | ¦ χ <sub>a</sub> | +<br>ABCDE | FAX           |

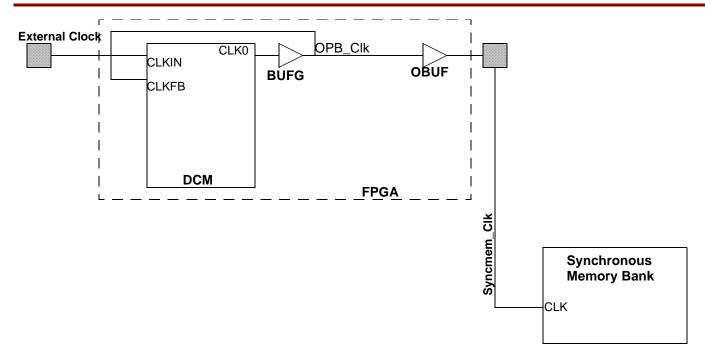

#### **Basic Timing for Memory**

The Memory Controller is designed to connect to a variety of memory subsystem configurations. For detailed descriptions regarding the timing and protocol of the IDT 71V416S SRAM, IDT 71V546 SRAM with ZBT<sup>™</sup> Features and the Intel 28F128J3 StrataFlash please refer to their respective data sheets.

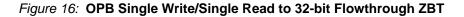

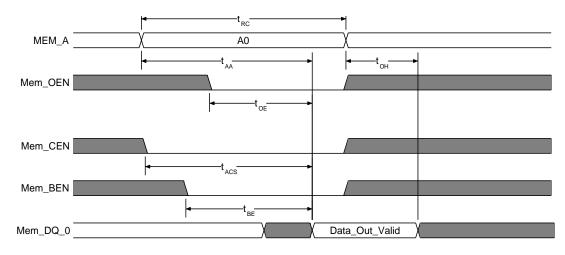

However, basic read and write timing diagrams are listed below. Figure 17 and Figure 18 illustrate the basic read and write functions for the SRAM. Table 11 defines the symbols used in the figures for the SRAM.

| Symbol           | Parameter <sup>(1)</sup>          |  |

|------------------|-----------------------------------|--|

| READ CYCLE       |                                   |  |

| t <sub>RC</sub>  | Read Cycle Time                   |  |

| t <sub>AA</sub>  | Address Access Time               |  |

| t <sub>ACS</sub> | Chip Select Access Time           |  |

| t <sub>OE</sub>  | Output Enable Low to Output Valid |  |

| t <sub>OH</sub>  | Output Hold from Address Change   |  |

| t <sub>BE</sub>  | Byte Enable Low to Output Valid   |  |

| WRITE CYCLE      |                                   |  |

| t <sub>WC</sub>  | Write Cycle Time                  |  |

| t <sub>AW</sub>  | Address Valid to End of Write     |  |

| t <sub>CW</sub>  | Chip Select Low to End of Write   |  |

| t <sub>BW</sub>  | Byte Enable Low to End of Write   |  |

| t <sub>AS</sub>  | Address Set-up Time               |  |

| t <sub>WR</sub>  | Address Hold from End of Write    |  |

| t <sub>WP</sub>  | Write Pulse Width                 |  |

| t <sub>DW</sub>  | Data Valid to End of Write        |  |

| t <sub>DH</sub>  | Data Hold Time                    |  |

| t <sub>OW</sub>  | Write Enable High to Output Low-Z |  |

#### Table 11: SRAM Parameter Description

#### Notes:

1. Refer to IDT71V416S Data Sheet for specific timing parameters.

- 2. WEN is HIGH for Read Cycle

- 3. Address must be valid prior to or coincident with the later CEN, BEN transition LOW; otherwise  $t_{AA}$  is the limiting parameter

- 4. Write Cycle Timing is WEN controlled.

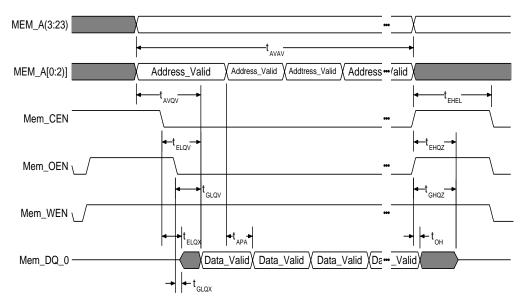

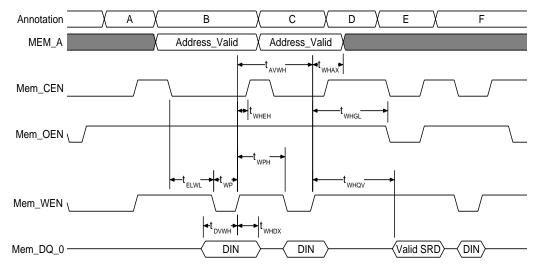

Figure 19 and Figure 20 illustrate the basic read and write functions for the Flash. Table 12 defines the symbols used in the figures for the Flash.

Figure 19: Waveform for both page-mode and standard word/byte read operation

| Symbol            | Parameter <sup>(1)</sup> |   |  |

|-------------------|--------------------------|---|--|

| READ ONLY         |                          |   |  |

| t <sub>AVAV</sub> | Read/Write Cycle Time    | - |  |

| t <sub>AVQV</sub> | Address to Output Delay  |   |  |

| t <sub>ELQV</sub> | CEN to Output Delay      |   |  |

#### Table 12: StrataFlash Parameter Description

| Symbol            | Parameter <sup>(1)</sup>                                             |  |  |

|-------------------|----------------------------------------------------------------------|--|--|

| t <sub>GLQV</sub> | OEN to Non-Array Output Delay                                        |  |  |

| t <sub>ELQX</sub> | CEN to Output Low-Z                                                  |  |  |

| t <sub>GLQX</sub> | OEN to Output Low-Z                                                  |  |  |

| t <sub>EHQZ</sub> | CEN High to Output in High-Z                                         |  |  |

| t <sub>GHQZ</sub> | OEN High to Output in High-Z                                         |  |  |

| t <sub>OH</sub>   | Output Hold from Address, CEN, or OEN Change, Whichever occurs first |  |  |

| t <sub>EHEL</sub> | CEN High to CEN Low                                                  |  |  |

| t <sub>APA</sub>  | Page Address Access Time                                             |  |  |

| Write Operations  |                                                                      |  |  |

| A                 | Power-up and standby                                                 |  |  |

| В                 | Write block erase, write buffer, or program set-up                   |  |  |

| С                 | Write block erase or write buffer confirm, or valid address and data |  |  |

| D                 | Automated erase delay                                                |  |  |

| E                 | Read status register or query data                                   |  |  |

| F                 | Write read array command                                             |  |  |

| t <sub>ELWL</sub> | CEN(WEN) Low to WEN(CEN) Going Low                                   |  |  |

| t <sub>WP</sub>   | Write Pulse Width                                                    |  |  |

| t <sub>DVWH</sub> | Data Setup to WEN(CEN) Going High                                    |  |  |

| t <sub>AVWH</sub> | Address Setup to WEN(CEN) Going High                                 |  |  |

| t <sub>WHEH</sub> | CEN(WEN) Hold from WEN(CEN) High                                     |  |  |

| t <sub>WHDX</sub> | Data Hold from WEN(CEN) High                                         |  |  |

| t <sub>WHAX</sub> | Address Hold from WEN(CEN) High                                      |  |  |