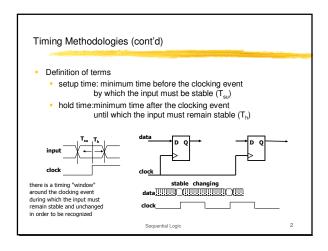

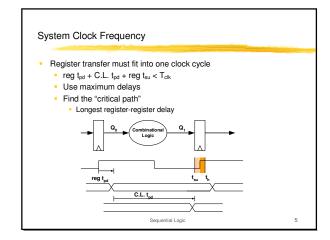

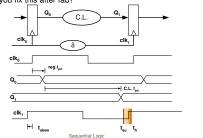

# Typical timing specifications Positive edge-triggered D flip-flop setup and hold times minimum clock width propagation delays (low to high, high to low, max and typical) CLK Tw 7ns all measurements are made from the clocking event that is, the rising edge of the clock Sequential Logic 3

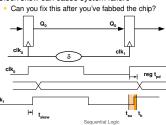

# Clock Skew

- Cannot make clock arrive at registers at the same time

- If skew > 0:

- $t_{pd} > t_{h+} t_{skew}$

- Clock skew can cause system failure

# Clock Skew Cannot make clock arrive at registers at the same time If skew > 0: t<sub>pd</sub> > t<sub>h +</sub> t<sub>skew</sub> Clock skew can cause system failure Can you fix this after you've fabbed the chip?

### Clock Skew

- If skew < 0:

- $t_{clk} > reg t_{pd+} CL t_{pd+} reg t_{SU+} |t_{skew}|$

- · Can you fix this after fab?

# Clock Skew

- If skew < 0:</p>

- t<sub>clk</sub> > reg t<sub>pd+</sub> CL t<sub>pd+</sub> reg t<sub>SU+</sub> |t<sub>skew</sub>|

- Can you fix this after fab?

### Clock Skew

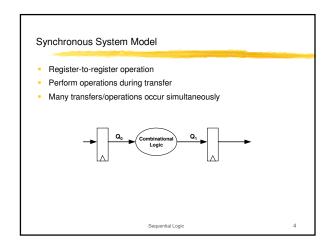

- Correct behavior assumes that all storage elements sample at exactly the same time

- Not possible in real systems:

- clock driven from some central location

- different wire delay to different points in the circuit

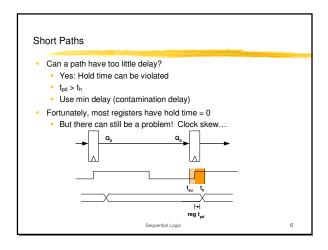

- Problems arise if skew is of the same order as FF contamination

- Gets worse as systems get faster (wires don't improve as fast)

- 1) distribute clock signals against the data flow

- 2) wire carrying the clock between two communicating components should be as short as possible

- 3) try to make all wires from the clock generator be the same length => clock tree

Sequential Logic

# Nasty Example

- · What can go wrong?

- How can you fix it?

Sequential Logic

12

10

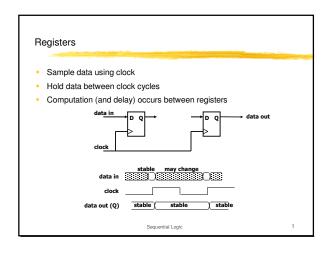

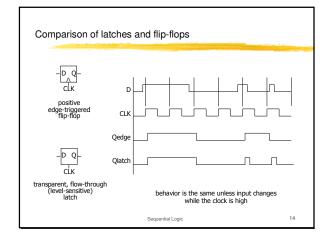

### Other Types of Latches and Flip-Flops

- D-FF is ubiquitous

- simplest design technique, minimizes number of wires preferred in PLDs and FPGAs good choice for data storage register edge-triggered has most straightforward timing constraints

- Historically J-K FF was popular versatile building block, often requires less total logic two inputs require more wiring and logic can always be implemented using D-FF

- Level-sensitive latches in special circumstances popular in VLSI because they can be made very small (4 T) fundamental building block of all other flip-flop types two latches make a D-FF

- Preset and clear inputs are highly desirable

- System reset

Sequential Logic

13

15

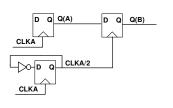

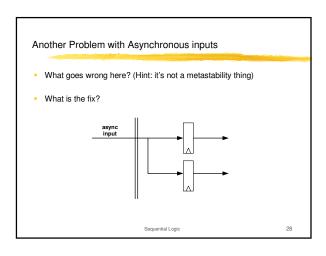

### What About External Inputs?

- Internal signals are OK

- Can only change when clock changes

- External signals can change at any time

- Asynchronous inputs

- Truly asynchronous

- Produced by a different clock

clkA

- This means register may sample a signal that is changing

- Violates setup/hold time

What happens?

Sequential Logic

# Sampling external inputs CLKA Q(A) CLKB Q(B) Sequential Logic 16

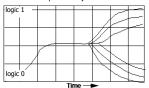

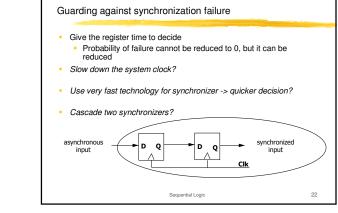

# Synchronization failure

- Occurs when FF input changes close to clock edge

- the FF may enter a metastable state neither a logic 0 nor 1 –

- it may stay in this state an indefinite amount of time

- this is not likely in practice but has some probability

small, but non-zero probability that the FF output will get stuck in an in-between state

oscilloscope traces demonstrating synchronizer failure and eventual decay to steady state Sequential Logic

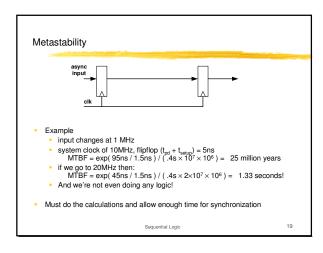

# Calculating probability of failure

For a single synchronizer

Mean-Time Between Failure (MTBF) = exp ( tr /  $\tau$  ) / ( T0 × f × a )

where a failure occurs if metastability persists beyond time tr

- tr is the resolution time extra time in clock period for settling

- $\qquad \qquad \text{Tclk } (t_{\text{pd}} + T_{\text{CL}} + t_{\text{setup}}) \\$

- f is the frequency of the FF clock

- a is the number of asynchronous input changes per second applied to the FF

- T0 and  $\boldsymbol{\tau}$  are constaints that depend on the  $\,$  FF's electrical characteristics (e.g., gain or steepness of curve)

example values are T0 = .4s and τ = 1.5ns

- (sensitive to temperature, voltage, cosmic rays, etc.).

- Must add probabilities from all synchronizers in system 1/MTBFsystem =  $\Sigma$  1/MTBFsynch

Sequential Logic

18

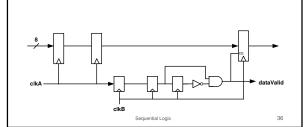

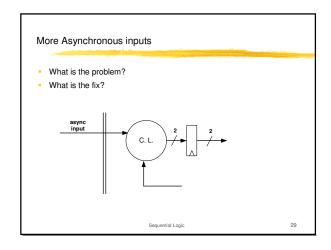

# More Asynchronous inputs

Can we input asynchronous data values with several bits?

ntial Logic

#

32

# What Went Wrong?

- Each bit has a different delay

- · Wire lengths differ

- Gate thresholds differ

- Driver speeds are different

- Register delays are different

- Rise vs. Fall times

- Clock skews to register bits

- Bottom line "data skew" is inevitable

- aka Bus Skew

- Longer wires => More skew

- What is the solution??

Sequential Logic

33

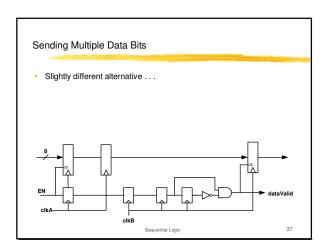

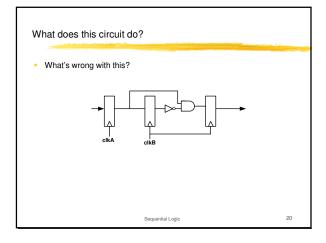

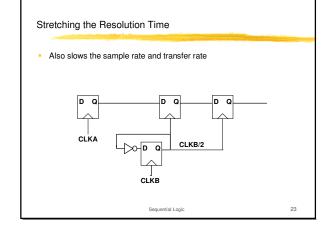

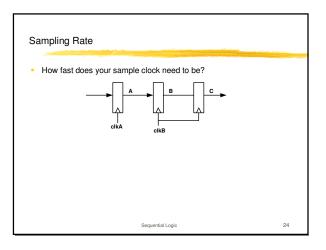

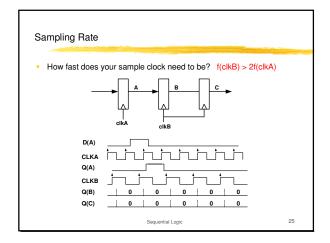

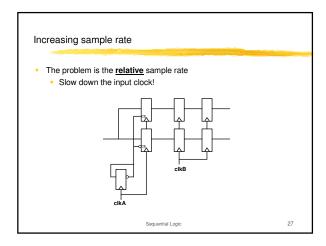

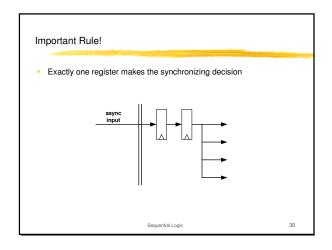

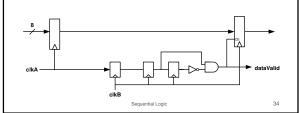

# Sending Multiple Data Bits

- Must send a "clock" with the data

- · Waits until data is stable

- De-skewing delay

- f(clkB) > 2 f(clkA)

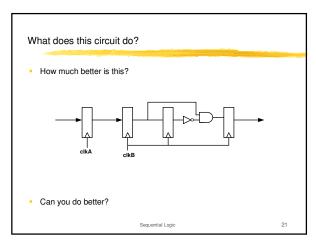

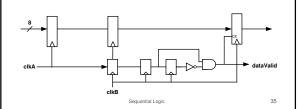

# Sending Multiple Data Bits

- Balancing path delays . . .

- What's wrong with this solution?

- What's the right way to do it?

# Sending Multiple Data Bits

The right way to do it . . .