# MicroBlaze Processor Reference Guide

Embedded Development Kit

EDK (v6.2) June 14, 2004

"Xilinx" and the Xilinx logo shown above are registered trademarks of Xilinx, Inc. Any rights not expressly granted herein are reserved. CoolRunner, RocketChips, Rocket IP, Spartan, StateBENCH, StateCAD, Virtex, XACT, XC2064, XC3090, XC4005, and XC5210 are registered trademarks of Xilinx, Inc.

The shadow X shown above is a trademark of Xilinx, Inc.

ACE Controller, ACE Flash, A.K.A. Speed, Alliance Series, AllianceCORE, Bencher, ChipScope, Configurable Logic Cell, CORE Generator, CoreLINX, Dual Block, EZTag, Fast CLK, Fast CONNECT, Fast FLASH, FastMap, Fast Zero Power, Foundation, Gigabit Speeds...and Beyond!, HardWire, HDL Bencher, IRL, J Drive, JBits, LCA, LogiBLOX, Logic Cell, LogiCORE, LogicProfessor, MicroVia, MultiLINX, NanoBlaze, PicoBlaze, PLUSASM, PowerGuide, PowerMaze, QPro, Real-PCI, Rocket I/O, SelectI/O, SelectRAM, SelectRAM+, Silicon Xpresso, Smartguide, Smart-IP, SmartSearch, SMARTswitch, System ACE, Testbench In A Minute, TrueMap, UIM, VectorMaze, VersaBlock, VersaRing, Virtex-II Pro, Virtex-II EasyPath, Wave Table, WebFITTER, WebPACK, WebPOWERED, XABEL, XACT-Floorplanner, XACT-Performance, XACTstep Advanced, XACTstep Foundry, XAM, XAPP, X-BLOX +, XC designated products, XChecker, XDM, XEPLD, Xilinx Foundation Series, Xilinx XDTV, Xinfo, XSI, XtremeDSP and ZERO+ are trademarks of Xilinx, Inc.

The Programmable Logic Company is a service mark of Xilinx, Inc.

All other trademarks are the property of their respective owners.

Xilinx, Inc. does not assume any liability arising out of the application or use of any product described or shown herein; nor does it convey any license under its patents, copyrights, or maskwork rights or any rights of others. Xilinx, Inc. reserves the right to make changes, at any time, in order to improve reliability, function or design and to supply the best product possible. Xilinx, Inc. will not assume responsibility for the use of any circuitry described herein other than circuitry entirely embodied in its products. Xilinx provides any design, code, or information shown or described herein "as is." By providing the design, code, or information as one possible implementation of a feature, application, or standard, Xilinx makes no representation that such implementation is free from any claims of infringement. You are responsible for obtaining any rights you may require for your implementation. Xilinx expressly disclaims any warranty whatsoever with respect to the adequacy of any such implementation, including but not limited to any warranties or representations that the implementation is free from claims of infringement, as well as any implied warranties of merchantability or fitness for a particular purpose. Xilinx, Inc. devices and products are protected under U.S. Patents. Other U.S. and foreign patents pending. Xilinx, Inc. does not represent that devices shown or products described herein are free from patent infringement or from any other third party right. Xilinx, Inc. assumes no obligation to correct any errors contained herein or to advise any user of this text of any correction if such be made. Xilinx, Inc. will not assume any liability for the accuracy or correctness of any engineering or software support or assistance provided to a user.

Xilinx products are not intended for use in life support appliances, devices, or systems. Use of a Xilinx product in such applications without the written consent of the appropriate Xilinx officer is prohibited.

The contents of this manual are owned and copyrighted by Xilinx. Copyright 1994-2002 Xilinx, Inc. All Rights Reserved. Except as stated herein, none of the material may be copied, reproduced, distributed, republished, downloaded, displayed, posted, or transmitted in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Xilinx. Any unauthorized use of any material contained in this manual may violate copyright laws, trademark laws, the laws of privacy and publicity, and communications regulations and statutes.

# MicroBlaze Processor Reference Guide EDK (v6.2) June 14, 2004

The following table shows the revision history for this document.

|          | Version | Revision                                                 |  |  |  |  |

|----------|---------|----------------------------------------------------------|--|--|--|--|

| 08/07/00 | 1.0     | Xilinx EDK (Embedded Processor Development Kit) release. |  |  |  |  |

# **Table of Contents**

| Preface: About This Guide            |          |

|--------------------------------------|----------|

| Manual Contents                      | 7        |

| Additional Resources                 | 7        |

| Conventions                          | 8        |

| Typographical                        |          |

| Online Document                      | Ć        |

|                                      |          |

| Chapter 1: MicroBlaze Architecture   |          |

| Summary                              | 11       |

| Overview                             | 11       |

| Features                             | 11       |

| Instructions                         | 12       |

| Registers                            | 16       |

| General Purpose Registers            |          |

| Special Purpose Registers            |          |

| Pipeline                             |          |

| Pipeline Architecture                |          |

| Branches                             |          |

| Load/Store Architecture              |          |

| Interrupts, Exceptions and Breaks    |          |

| Interrupts                           |          |

| Exceptions                           |          |

| Instruction Cache                    |          |

| Overview                             |          |

| Cache Organization                   |          |

| Cache Operation                      |          |

| Software                             |          |

| LMB Memory                           | 26       |

| Data Cache                           |          |

| Overview                             |          |

| Cache Organization                   |          |

| *                                    | 21<br>28 |

| LMB Memory                           |          |

| Fast Simplex Link Interface          |          |

| FSL Read Instructions                |          |

| FSL Write Instructions               |          |

| Debug Interface                      | 30       |

| Debugging Features                   | 31       |

|                                      |          |

| Chapter 2: MicroBlaze Bus Interfaces |          |

| Summary                              | 33       |

|            | <b>Overview</b>                                              |            |

|------------|--------------------------------------------------------------|------------|

|            | Features                                                     |            |

|            | Bus Configurations 3                                         |            |

|            | Typical Peripheral Placement                                 |            |

|            | Bit and Byte Labeling 4                                      |            |

|            | Core I/O 4                                                   |            |

|            | Bus Organization 4                                           | 15         |

|            | OPB Bus Configuration                                        |            |

|            | LMB Bus Definition                                           |            |

|            | LMB Bus Operations                                           |            |

|            | FSL Bus Operation                                            |            |

|            | Debug Interface                                              |            |

|            | Implementation 5                                             |            |

|            | Parameterization                                             |            |

|            | T di dinoconzacion                                           | •          |

| Ch.        | apter 3: MicroBlaze Endianness                               |            |

| •          | •                                                            |            |

|            | Definitions                                                  |            |

|            | Bit Naming Conventions                                       |            |

|            | Data Types and Endianness 5                                  |            |

|            | VHDL Example 6                                               |            |

|            | BRAM – LMB Example                                           |            |

|            | BRAM – OPB Example 6                                         | 13         |

| <b>∩</b> L | antar A. Migra Plana Application Dinamy Interface            |            |

| CII        | apter 4: MicroBlaze Application Binary Interface             |            |

|            | Scope                                                        |            |

|            | Data Types 6                                                 | 57         |

|            | Register Usage Conventions 6                                 | 37         |

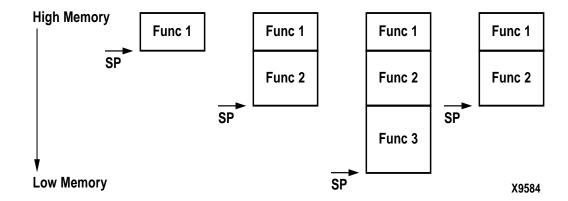

|            | Stack Convention 6                                           | 39         |

|            | Calling Convention                                           | ′0         |

|            | <b>Memory Model</b>                                          | <b>′</b> 0 |

|            | Small data area                                              |            |

|            | Data area                                                    |            |

|            | Common un-initialized area                                   |            |

|            |                                                              |            |

|            | Interrupt and Exception Handling                             | I          |

| <b>~</b> ! | and a F. Miller Diagram to the ordinary Oct. Applifered to a |            |

| Ch         | apter 5: MicroBlaze Instruction Set Architecture             |            |

|            | <b>Summary</b> 7                                             | ′3         |

|            | Notation                                                     | 13         |

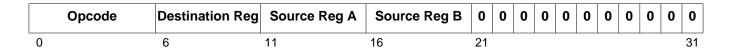

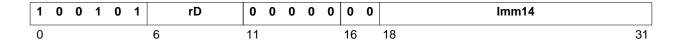

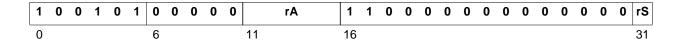

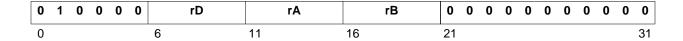

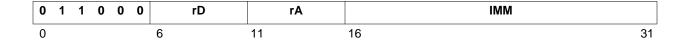

|            | Formats                                                      | ′4         |

|            |                                                              | 7.1        |

# **About This Guide**

Welcome to the MicroBlaze Processor Reference Guide. This document provides information about the 32-bit soft processor, MicroBlaze, included in the Embedded Processor Development Kit (EDK). The document is meant as a guide to the MicroBlaze hardware and software architecture.

#### **Manual Contents**

This manual discusses the following topics specific to MicroBlaze soft processor:

- Core Architecture

- Bus Interfaces and Endieness

- Application Binary Interface

- Instruction Set Architecture

# **Additional Resources**

For additional information, go to  $\underline{\text{http://support.xilinx.com}}$ . The following table lists some of the resources you can access from this website. You can also directly access these resources using the provided URLs.

| Resource          | Description/URL                                                                                                                                                                                                 |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tutorials         | Tutorials covering Xilinx design flows, from design entry to verification and debugging                                                                                                                         |

|                   | http://support.xilinx.com/support/techsup/tutorials/index.htm                                                                                                                                                   |

| Answer Browser    | Database of Xilinx solution records                                                                                                                                                                             |

|                   | http://support.xilinx.com/xlnx/xil_ans_browser.jsp                                                                                                                                                              |

| Application Notes | Descriptions of device-specific design techniques and approaches                                                                                                                                                |

|                   | http://support.xilinx.com/apps/appsweb.htm                                                                                                                                                                      |

| Data Book         | Pages from <i>The Programmable Logic Data Book</i> , which contains device-specific information on Xilinx device characteristics, including readback, boundary scan, configuration, length count, and debugging |

|                   | http://support.xilinx.com/partinfo/databook.htm                                                                                                                                                                 |

| Problem Solvers   | Interactive tools that allow you to troubleshoot your design issues<br>http://support.xilinx.com/support/troubleshoot/psolvers.htm                                                                              |

| Resource    | Description/URL                                                                   |  |  |  |  |  |  |

|-------------|-----------------------------------------------------------------------------------|--|--|--|--|--|--|

| Tech Tips   | Latest news, design tips, and patch information for the Xilinx design environment |  |  |  |  |  |  |

|             | http://www.support.xilinx.com/xlnx/xil_tt_home.jsp                                |  |  |  |  |  |  |

| GNU Manuals | The entire set of GNU manuals                                                     |  |  |  |  |  |  |

|             | http://www.gnu.org/manual                                                         |  |  |  |  |  |  |

# **Conventions**

This document uses the following conventions. An example illustrates each convention.

# Typographical

The following typographical conventions are used in this document:

| Convention          | Meaning or Use                                                                                       | Example                                                                                            |

|---------------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| Courier font        | Messages, prompts, and program files that the system displays                                        | speed grade: - 100                                                                                 |

| Courier bold        | Literal commands that you enter in a syntactical statement                                           | ngdbuild design_name                                                                               |

| Helvetica bold      | Commands that you select from a menu                                                                 | File → Open                                                                                        |

|                     | Keyboard shortcuts                                                                                   | Ctrl+C                                                                                             |

|                     | Variables in a syntax<br>statement for which you must<br>supply values                               | ngdbuild design_name                                                                               |

| Italic font         | References to other manuals                                                                          | See the <i>Development System Reference Guide</i> for more information.                            |

|                     | Emphasis in text                                                                                     | If a wire is drawn so that it overlaps the pin of a symbol, the two nets are <i>not</i> connected. |

| Square brackets [ ] | An optional entry or parameter. However, in bus specifications, such as bus[7:0], they are required. | ngdbuild [option_name] design_name                                                                 |

| Braces { }          | A list of items from which you must choose one or more                                               | lowpwr ={on off}                                                                                   |

| Vertical bar        | Separates items in a list of choices                                                                 | lowpwr ={on off}                                                                                   |

| Convention          | Meaning or Use                            | Example                                    |  |  |

|---------------------|-------------------------------------------|--------------------------------------------|--|--|

| Vertical ellipsis   | Repetitive material that has been omitted | IOB #1: Name = QOUT' IOB #2: Name = CLKIN' |  |  |

| Horizontal ellipsis | Repetitive material that has been omitted | allow block block_name loc1 loc2 locn;     |  |  |

# **Online Document**

The following conventions are used in this document:

| Convention            | Meaning or Use                                                                                    | Example                                                                                                 |

|-----------------------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| Blue text             | Cross-reference link to a location in the current file or in another file in the current document | See the section "Additional Resources" for details.  Refer to "Title Formats" in Chapter 1 for details. |

| Red text              | Cross-reference link to a location in another document                                            | See Figure 2-5 in the <i>Virtex-II Handbook.</i>                                                        |

| Blue, underlined text | Hyperlink to a website (URL)                                                                      | Go to <a href="http://www.xilinx.com">http://www.xilinx.com</a> for the latest speed files.             |

# MicroBlaze Architecture

# **Summary**

This document describes the architecture for the MicroBlaze™ 32-bit soft processor core.

#### **Overview**

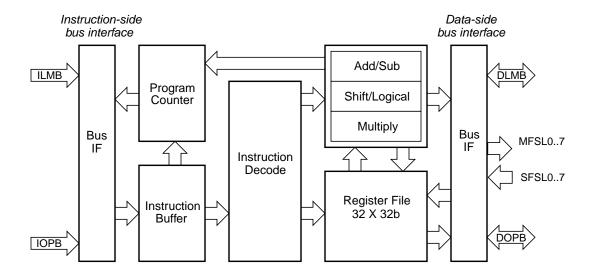

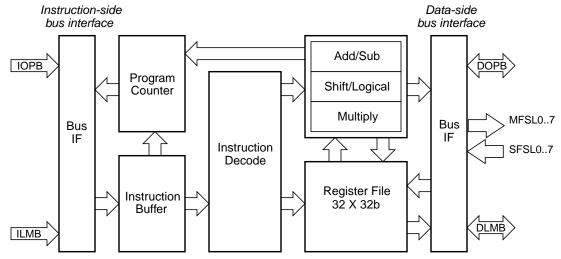

The MicroBlaze embedded soft core is a reduced instruction set computer (RISC) optimized for implementation in Xilinx field programmable gate arrays (FPGAs). See Figure 1-1 for a block diagram depicting the MicroBlaze core.

#### **Features**

The MicroBlaze embedded soft core includes the following features:

- Thirty-two 32-bit general purpose registers

- 32-bit instruction word with three operands and two addressing modes

- Separate 32-bit instruction and data buses that conform to IBM's OPB (On-chip Peripheral Bus) specification

- Separate 32-bit instruction and data buses with direct connection to on-chip block RAM through a LMB (Local Memory Bus)

- 32-bit address bus

- Single issue pipeline

- Instruction and data cache

- Hardware debug logic

- FSL (Fast Simplex Link) support

- Hardware multiplier (in Virtex-II and subsequent devices

Figure 1-1: MicroBlaze Core Block Diagram

## Instructions

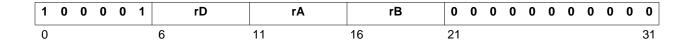

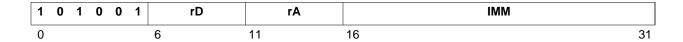

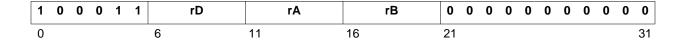

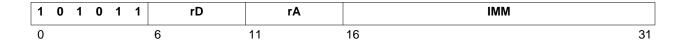

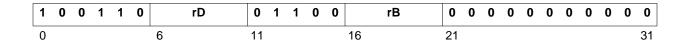

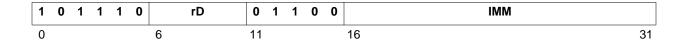

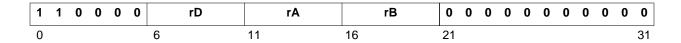

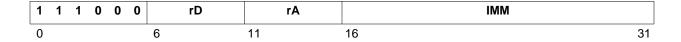

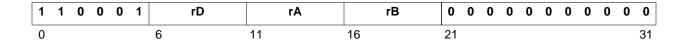

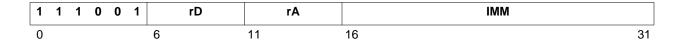

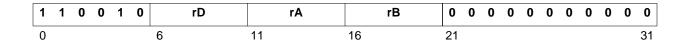

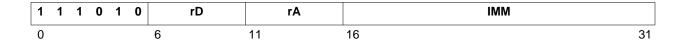

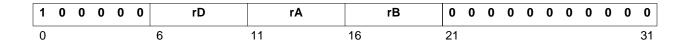

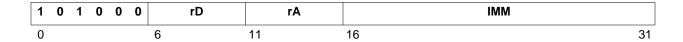

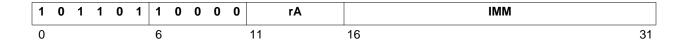

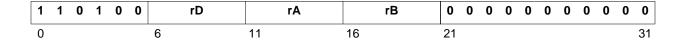

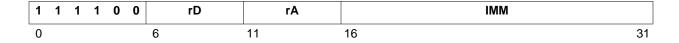

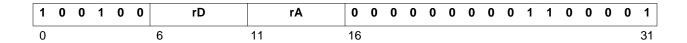

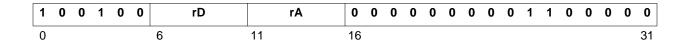

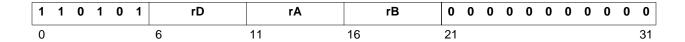

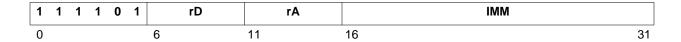

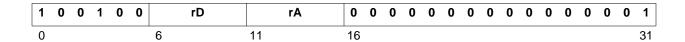

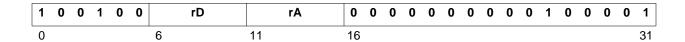

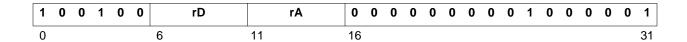

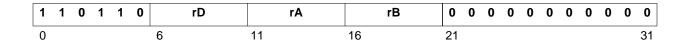

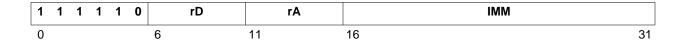

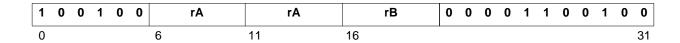

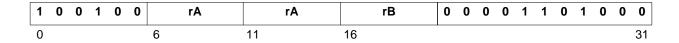

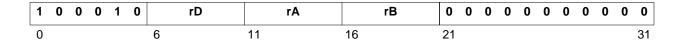

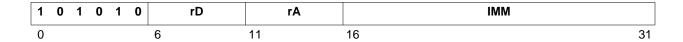

All MicroBlaze instructions are 32 bits and are defined as either Type A or Type B. Type A instructions have up to two source register operands and one destination register operand. Type B instructions have one source register and a 16-bit immediate operand (which can be extended to 32 bits by preceding the Type B instruction with an IMM instruction). Type B instructions have a single destination register operand. Instructions are provided in the following functional categories: arithmetic, logical, branch, load/store, and special. Table 1-2 lists the MicroBlaze instruction set. Refer to the MicroBlaze Instruction Set Architecture document for more information on these instructions. Table 1-1 describes the instruction set nomenclature used in the semantics of each instruction.

Table 1-1: Instruction Set Nomenclature

| Symbol | Description                                              |  |  |  |  |  |  |

|--------|----------------------------------------------------------|--|--|--|--|--|--|

| Ra     | R0 - R31, General Purpose Register, source operand a     |  |  |  |  |  |  |

| Rb     | R0 - R31, General Purpose Register, source operand b     |  |  |  |  |  |  |

| Rd     | R0 - R31, General Purpose Register, destination operand, |  |  |  |  |  |  |

| С      | Carry flag, MSR[29]                                      |  |  |  |  |  |  |

| Sa     | Special Purpose Register, source operand                 |  |  |  |  |  |  |

| Sd     | Special Purpose Register, destination operand            |  |  |  |  |  |  |

| s(x)   | Sign extend argument x to 32-bit value                   |  |  |  |  |  |  |

| *Addr  | Memory contents at location Addr (data-size aligned)     |  |  |  |  |  |  |

Table 1-2: MicroBlaze Instruction Set Summary

| Type A            | 0-5    | 6-10  | 11-15 | 16-20 | 21-31       | Semantics                            |

|-------------------|--------|-------|-------|-------|-------------|--------------------------------------|

| Type B            | 0-5    | 6-10  | 11-15 | 16-31 |             | Semantics                            |

| ADD Rd,Ra,Rb      | 000000 | Rd    | Ra    | Rb    | 00000000000 | Rd := Rb + Ra                        |

| RSUB Rd,Ra,Rb     | 000001 | Rd    | Ra    | Rb    | 00000000000 | $Rd := Rb + \overline{Ra} + 1$       |

| ADDC Rd,Ra,Rb     | 000010 | Rd    | Ra    | Rb    | 00000000000 | Rd := Rb + Ra + C                    |

| RSUBC Rd,Ra,Rb    | 000011 | Rd    | Ra    | Rb    | 00000000000 | $Rd := Rb + \overline{Ra} + C$       |

| ADDK Rd,Ra,Rb     | 000100 | Rd    | Ra    | Rb    | 00000000000 | Rd := Rb + Ra                        |

| RSUBK Rd,Ra,Rb    | 000101 | Rd    | Ra    | Rb    | 00000000000 | $Rd := Rb + \overline{Ra} + 1$       |

| ADDKC Rd,Ra,Rb    | 000110 | Rd    | Ra    | Rb    | 00000000000 | Rd := Rb + Ra + C                    |

| RSUBKC Rd,Ra,Rb   | 000111 | Rd    | Ra    | Rb    | 00000000000 | $Rd := Rb + \overline{Ra} + C$       |

| CMP Rd,Ra,Rb      | 000101 | Rd    | Ra    | Rb    | 0000000001  | Rd := Rb cmp Ra (signed)             |

| CMPU Rd,Ra,Rb     | 000101 | Rd    | Ra    | Rb    | 0000000011  | Rd := Rb cmp Ra (unsigned)           |

| ADDI Rd,Ra,Imm    | 001000 | Rd    | Ra    |       | Imm         | Rd := s(Imm) + Ra                    |

| RSUBI Rd,Ra,Imm   | 001001 | Rd    | Ra    |       | Imm         | $Rd := s(Imm) + \overline{Ra} + 1$   |

| ADDIC Rd,Ra,Imm   | 001010 | Rd    | Ra    |       | Imm         | Rd := s(Imm) + Ra + C                |

| RSUBIC Rd,Ra,Imm  | 001011 | Rd    | Ra    |       | Imm         | $Rd := s(Imm) + \overline{Ra} + C$   |

| ADDIK Rd,Ra,Imm   | 001100 | Rd    | Ra    |       | Imm         | Rd := s(Imm) + Ra                    |

| RSUBIK Rd,Ra,Imm  | 001101 | Rd    | Ra    |       | Imm         | $Rd := s(Imm) + \overline{Ra} + 1$   |

| ADDIKC Rd,Ra,Imm  | 001110 | Rd    | Ra    |       | Imm         | Rd := s(Imm) + Ra + C                |

| RSUBIKC Rd,Ra,Imm | 001111 | Rd    | Ra    |       | Imm         | $Rd := s(Imm) + \overline{Ra} + C$   |

| MUL Rd,Ra,Rb      | 010000 | Rd    | Ra    | Rb    | 00000000000 | Rd := Ra * Rb                        |

| BSRL Rd,Ra,Rb     | 010001 | Rd    | Ra    | Rb    | 00000000000 | Rd := Ra >> Rb                       |

| BSRA Rd,Ra,Rb     | 010001 | Rd    | Ra    | Rb    | 01000000000 | $Rd := Ra[0], (Ra \gg Rb)$           |

| BSLL Rd,Ra,Rb     | 010001 | Rd    | Ra    | Rb    | 10000000000 | $Rd := Ra \ll Rb$                    |

| MULI Rd,Ra,Imm    | 011000 | Rd    | Ra    |       | Imm         | Rd := Ra * s(Imm)                    |

| BSRLI Rd,Ra,Imm   | 011001 | Rd    | Ra    | 0000  | 0000 Imm    | Rd := Ra >> Imm                      |

| BSRAI Rd,Ra,Imm   | 011001 | Rd    | Ra    | 0000  | 0100 Imm    | Rd := Ra[0], (Ra >> Imm)             |

| BSLLI Rd,Ra,Imm   | 011001 | Rd    | Ra    | 0000  | 1000 Imm    | Rd := Ra << Imm                      |

| IDIV Rd,Ra,Rb     | 010010 | Rd    | Ra    | Rb    | 00000000000 | Rd := Rb/Ra, signed                  |

| IDIVU Rd,Ra,Rb    | 010010 | Rd    | Ra    | Rb    | 00000000001 | Rd := Rb/Ra, unsigned                |

| GET Rd,FSLx       | 011011 | Rd    | 00000 | 0000  | FSLx        | Rd := FSLx (blocking data read)      |

| PUT Ra,FSLx       | 011011 | 00000 | Ra    | 1000  | FSLx        | FSLx := Ra (blocking data write)     |

| nGET Rd,FSLx      | 011011 | Rd    | 00000 | 0100  | FSLx        | Rd := FSLx (non-blocking data read)  |

| nPUT Ra,FSLx      | 011011 | 00000 | Ra    | 1100  | FSLx        | FSLx := Ra (non-blocking data write) |

Table 1-2: MicroBlaze Instruction Set Summary (Continued)

| Type A        | 0-5    | 6-10  | 11-15 | 16-20           | 21-31         |                                         |

|---------------|--------|-------|-------|-----------------|---------------|-----------------------------------------|

| Type B        | 0-5    | 6-10  | 11-15 | 16-31           |               | Semantics                               |

| cGET Rd,FSLx  | 011011 | Rd    | 00000 | 0010            | FSLx          | Rd := FSLx (blocking control read)      |

| cPUT Ra,FSLx  | 011011 | 00000 | Ra    | 1010            | FSLx          | FSLx := Ra (blocking control write)     |

| ncGET Rd,FSLx | 011011 | Rd    | 00000 | 0110            | FSLx          | Rd := FSLx (non-blocking control read)  |

| ncPUT Ra,FSLx | 011011 | 00000 | Ra    | 1110            | FSLx          | FSLx := Ra (non-blocking control write) |

| OR Rd,Ra,Rb   | 100000 | Rd    | Ra    | Rb              | 00000000000   | Rd := Ra or Rb                          |

| AND Rd,Ra,Rb  | 100001 | Rd    | Ra    | Rb              | 00000000000   | Rd := Ra and Rb                         |

| XOR Rd,Ra,Rb  | 100010 | Rd    | Ra    | Rb              | 00000000000   | Rd := Ra xor Rb                         |

| ANDN Rd,Ra,Rb | 100011 | Rd    | Ra    | Rb              | 00000000000   | $Rd := Ra \text{ and } \overline{Rb}$   |

| SRA Rd,Ra     | 100100 | Rd    | Ra    | 00000           | 000000000001  | Rd := Ra[0], (Ra >> 1); C := Ra[31]     |

| SRC Rd,Ra     | 100100 | Rd    | Ra    | 00000           | 00000100001   | Rd := C, (Ra >> 1); C := Ra[31]         |

| SRL Rd,Ra     | 100100 | Rd    | Ra    | 00000           | 000001000001  | Rd := 0, (Ra >> 1); C := Ra[31]         |

| SEXT8 Rd,Ra   | 100100 | Rd    | Ra    | 00000           | 000001100000  | Rd[0:23] := Ra[24];                     |

|               |        |       |       |                 |               | Rd[24:31] := Ra[24:31]                  |

| SEXT16 Rd,Ra  | 100100 | Rd    | Ra    | 000000001100001 |               | Rd[0:15] := Ra[16];                     |

|               |        |       |       |                 |               | Rd[16:31] := Ra[16:31]                  |

| WIC Ra,Rb     | 100100 | Ra    | Ra    | Rb              | 01101000      | ICache_Tag := Ra, ICache_Data := Rb     |

| WDC Ra,Rb     | 100100 | Ra    | Ra    | Rb              | 01100100      | DCache_Tag := Ra, DCache_Data := Rb     |

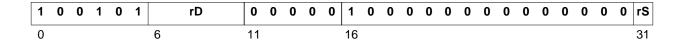

| MTS Sd,Ra     | 100101 | 00000 | Ra    | 11000           | 000000000d    | Sd := Ra , where S1 is MSR              |

| MFS Rd,Sa     | 100101 | Rd    | 00000 | 10000           | 000000000000a | Rd := Sa , where S0 is PC and S1 is MSR |

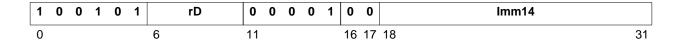

| MSRCLR Rd,Imm | 100101 | Rd    | 00001 | 00              | Imm14         | Rd := MSR; MSR := MSR ^ Imm14           |

| MSRSET Rd,Imm | 100101 | Rd    | 00000 | 00              | Imm14         | Rd := MSR; MSR := MSR ^ Imm14           |

| BR Rb         | 100110 | 00000 | 00000 | Rb              | 00000000000   | PC := PC + Rb                           |

| BRD Rb        | 100110 | 00000 | 10000 | Rb              | 00000000000   | PC := PC + Rb                           |

| BRLD Rd,Rb    | 100110 | Rd    | 10100 | Rb              | 00000000000   | PC := PC + Rb; Rd := PC                 |

| BRA Rb        | 100110 | 00000 | 01000 | Rb              | 00000000000   | PC := Rb                                |

| BRAD Rb       | 100110 | 00000 | 11000 | Rb              | 00000000000   | PC := Rb                                |

| BRALD Rd,Rb   | 100110 | Rd    | 11100 | Rb              | 00000000000   | PC := Rb; Rd := PC                      |

| BRK Rd,Rb     | 100110 | Rd    | 01100 | Rb              | 00000000000   | PC := Rb; Rd := PC; MSR[BIP] := 1       |

| BEQ Ra,Rb     | 100111 | 00000 | Ra    | Rb              | 00000000000   | if $Ra = 0$ : $PC := PC + Rb$           |

| BNE Ra,Rb     | 100111 | 00001 | Ra    | Rb              | 00000000000   | if Ra /= 0: PC := PC + Rb               |

| BLT Ra,Rb     | 100111 | 00010 | Ra    | Rb              | 00000000000   | if Ra < 0: PC := PC + Rb                |

| BLE Ra,Rb     | 100111 | 00011 | Ra    | Rb              | 00000000000   | if Ra <= 0: PC := PC + Rb               |

| BGT Ra,Rb     | 100111 | 00100 | Ra    | Rb              | 00000000000   | if Ra > 0: PC := PC + Rb                |

Table 1-2: MicroBlaze Instruction Set Summary (Continued)

| Type A          | 0-5    | 6-10  | 11-15 | 16-20 21-31 |             | Computing                                 |

|-----------------|--------|-------|-------|-------------|-------------|-------------------------------------------|

| Type B          | 0-5    | 6-10  | 11-15 | 16-31       |             | Semantics                                 |

| BGE Ra,Rb       | 100111 | 00101 | Ra    | Rb          | 00000000000 | if Ra >= 0: PC := PC + Rb                 |

| BEQD Ra,Rb      | 100111 | 10000 | Ra    | Rb          | 00000000000 | if Ra = 0: PC := PC + Rb                  |

| BNED Ra,Rb      | 100111 | 10001 | Ra    | Rb          | 00000000000 | if Ra /= 0: PC := PC + Rb                 |

| BLTD Ra,Rb      | 100111 | 10010 | Ra    | Rb          | 00000000000 | if Ra < 0: PC := PC + Rb                  |

| BLED Ra,Rb      | 100111 | 10011 | Ra    | Rb          | 00000000000 | if Ra <= 0: PC := PC + Rb                 |

| BGTD Ra,Rb      | 100111 | 10100 | Ra    | Rb          | 00000000000 | if Ra > 0: PC := PC + Rb                  |

| BGED Ra,Rb      | 100111 | 10101 | Ra    | Rb          | 00000000000 | if Ra >= 0: PC := PC + Rb                 |

| ORI Rd,Ra,Imm   | 101000 | Rd    | Ra    |             | Imm         | Rd := Ra or s(Imm)                        |

| ANDI Rd,Ra,Imm  | 101001 | Rd    | Ra    |             | Imm         | Rd := Ra and s(Imm)                       |

| XORI Rd,Ra,Imm  | 101010 | Rd    | Ra    |             | Imm         | Rd := Ra xor s(Imm)                       |

| ANDNI Rd,Ra,Imm | 101011 | Rd    | Ra    |             | Imm         | $Rd := Ra \text{ and } \overline{s(Imm)}$ |

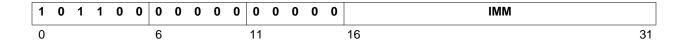

| IMM Imm         | 101100 | 00000 | 00000 |             | Imm         | Imm[0:15] := Imm                          |

| RTSD Ra,Imm     | 101101 | 10000 | Ra    |             | Imm         | PC := Ra + s(Imm)                         |

| RTID Ra,Imm     | 101101 | 10001 | Ra    |             | Imm         | PC := Ra + s(Imm); MSR[IE] := 1           |

| RTBD Ra,Imm     | 101101 | 10010 | Ra    |             | Imm         | PC := Ra + s(Imm); MSR[BIP] := 0          |

| BRID Imm        | 101110 | 00000 | 10000 |             | Imm         | PC := PC + s(Imm)                         |

| BRLID Rd,Imm    | 101110 | Rd    | 10100 |             | Imm         | PC := PC + s(Imm); Rd := PC               |

| BRAI Imm        | 101110 | 00000 | 01000 |             | Imm         | PC := s(Imm)                              |

| BRAID Imm       | 101110 | 00000 | 11000 |             | Imm         | PC := s(Imm)                              |

| BRALID Rd,Imm   | 101110 | Rd    | 11100 |             | Imm         | PC := s(Imm); Rd := PC                    |

| BRKI Rd,Imm     | 101110 | Rd    | 01100 |             | Imm         | PC := s(Imm); Rd := PC; MSR[BIP] := 1     |

| BEQI Ra,Imm     | 101111 | 00000 | Ra    |             | Imm         | if $Ra = 0$ : $PC := PC + s(Imm)$         |

| BNEI Ra,Imm     | 101111 | 00001 | Ra    |             | Imm         | if Ra /= 0: PC := PC + s(Imm)             |

| BLTI Ra,Imm     | 101111 | 00010 | Ra    |             | Imm         | if Ra < 0: PC := PC + s(Imm)              |

| BLEI Ra,Imm     | 101111 | 00011 | Ra    |             | Imm         | if Ra <= 0: PC := PC + s(Imm)             |

| BGTI Ra,Imm     | 101111 | 00100 | Ra    |             | Imm         | if Ra > 0: PC := PC + s(Imm)              |

| BGEI Ra,Imm     | 101111 | 00101 | Ra    |             | Imm         | if $Ra \ge 0$ : $PC := PC + s(Imm)$       |

| BEQID Ra,Imm    | 101111 | 10000 | Ra    |             | Imm         | if $Ra = 0$ : $PC := PC + s(Imm)$         |

| BNEID Ra,Imm    | 101111 | 10001 | Ra    |             | Imm         | if Ra /= 0: PC := PC + s(Imm)             |

| BLTID Ra,Imm    | 101111 | 10010 | Ra    |             | Imm         | if $Ra < 0$ : $PC := PC + s(Imm)$         |

| BLEID Ra,Imm    | 101111 | 10011 | Ra    |             | Imm         | if Ra <= 0: PC := PC + s(Imm)             |

| BGTID Ra,Imm    | 101111 | 10100 | Ra    |             | Imm         | if $Ra > 0$ : $PC := PC + s(Imm)$         |

| BGEID Ra,Imm    | 101111 | 10101 | Ra    |             | Imm         | if $Ra \ge 0$ : $PC := PC + s(Imm)$       |

Table 1-2: MicroBlaze Instruction Set Summary (Continued)

| Type A         | 0-5    | 6-10 | 11-15 | 16-20 | 21-31       | Semantics                         |

|----------------|--------|------|-------|-------|-------------|-----------------------------------|

| Type B         | 0-5    | 6-10 | 11-15 |       | 16-31       | Semantics                         |

| LBU Rd,Ra,Rb   | 110000 | Rd   | Ra    | Rb    | 00000000000 | Addr := Ra + Rb;                  |

|                |        |      |       |       |             | Rd[0:23] := 0, Rd[24:31] := *Addr |

| LHU Rd,Ra,Rb   | 110001 | Rd   | Ra    | Rb    | 00000000000 | Addr := Ra + Rb;                  |

|                |        |      |       |       |             | Rd[0:15] := 0, Rd[16:31] := *Addr |

| LW Rd,Ra,Rb    | 110010 | Rd   | Ra    | Rb    | 00000000000 | Addr := Ra + Rb;                  |

|                |        |      |       |       |             | Rd := *Addr                       |

| SB Rd,Ra,Rb    | 110100 | Rd   | Ra    | Rb    | 00000000000 | Addr := Ra + Rb;                  |

|                |        |      |       |       |             | *Addr := Rd[24:31]                |

| SH Rd,Ra,Rb    | 110101 | Rd   | Ra    | Rb    | 00000000000 | Addr := Ra + Rb;                  |

|                |        |      |       |       |             | *Addr := Rd[16:31]                |

| SW Rd,Ra,Rb    | 110110 | Rd   | Ra    | Rb    | 00000000000 | Addr := Ra + Rb;                  |

|                |        |      |       |       |             | *Addr := Rd                       |

| LBUI Rd,Ra,Imm | 111000 | Rd   | Ra    |       | Imm         | Addr := Ra + s(Imm);              |

|                |        |      |       |       |             | Rd[0:23] := 0, Rd[24:31] := *Addr |

| LHUI Rd,Ra,Imm | 111001 | Rd   | Ra    |       | Imm         | Addr := Ra + s(Imm);              |

|                |        |      |       |       |             | Rd[0:15] := 0, Rd[16:31] := *Addr |

| LWI Rd,Ra,Imm  | 111010 | Rd   | Ra    |       | Imm         | Addr := Ra + s(Imm);              |

|                |        |      |       |       |             | Rd := *Addr                       |

| SBI Rd,Ra,Imm  | 111100 | Rd   | Ra    |       | Imm         | Addr := Ra + s(Imm);              |

|                |        |      |       |       |             | *Addr := Rd[24:31]                |

| SHI Rd,Ra,Imm  | 111101 | Rd   | Ra    |       | Imm         | Addr := Ra + s(Imm);              |

|                |        |      |       |       |             | *Addr := Rd[16:31]                |

| SWI Rd,Ra,Imm  | 111110 | Rd   | Ra    |       | Imm         | Addr := Ra + s(Imm);              |

|                |        |      |       |       |             | *Addr := Rd                       |

# **Registers**

MicroBlaze is a fully orthogonal architecture. It has thirty-two 32-bit general purpose registers and two 32-bit special purpose registers.

# General Purpose Registers

The thirty-two 32-bit General Purpose Registers are numbered R0 through R31. R0 is defined to always have the value of zero. Anything written to R0 is discarded, and zero is always read.

Figure 1-2: R0-R31

Table 1-3: General Purpose Registers (R0-R31)

| Bits | Name       | Description                                                             | Reset Value |

|------|------------|-------------------------------------------------------------------------|-------------|

| 0:31 | R0 through | General Purpose Register                                                | 0x00000000  |

|      | R31        | R0 through R31 are 32-bit general purpose registers. R0 is always zero. |             |

# **Special Purpose Registers**

## Program Counter (PC)

The Program Counter is the 32-bit address of the next instruction word to be fetched. It can be read by accessing RPC with an MFS instruction. It cannot be written to using an MTS instruction.

Figure 1-3: PC

Table 1-4: Program Counter (PC)

| Bits | Name | Description                          | Reset Value |

|------|------|--------------------------------------|-------------|

| 0:31 | PC   | Program Counter                      | 0x00000000  |

|      |      | Address of next instruction to fetch |             |

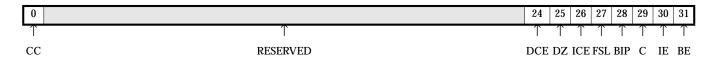

#### Machine Status Register (MSR)

The Machine Status Register contains the carry flag and enables for interrupts, buslock, cache and FSL error. It can be read by accessing RMSR with an MFS instruction. When reading the MSR, bit 29 is replicated in bit 0 as the carry copy. MSR can be written to with an MTS instruction. Writes to MSR are delayed one clock cycle. When writing to MSR using MTS, the value written takes effect one clock cycle after executing the MTS instruction. Any value written to bit 0 is discarded.

Figure 1-4: MSR

Table 1-5: Machine Status Register (MSR)

| Bits | Name     | Description                                                                                         | Reset Value |

|------|----------|-----------------------------------------------------------------------------------------------------|-------------|

| 0 CC |          | Arithmetic Carry Copy                                                                               | 0           |

|      |          | Copy of the Arithmetic Carry (bit 29).<br>Read only.                                                |             |

| 1:23 | Reserved |                                                                                                     |             |

| 24   | DCE      | Data Cache Enable                                                                                   | 0           |

|      |          | 0 Data Cache is Disabled                                                                            |             |

|      |          | 1 Data Cache is Enabled                                                                             |             |

| 25   | DZ       | Dvision by Zero                                                                                     | 0           |

|      |          | 0 No divison by zero has occured                                                                    |             |

|      |          | 1 Division by zero has occured                                                                      |             |

| 26   | ICE      | Instruction Cache Enable                                                                            | 0           |

|      |          | 0 Instruction Cache is Disabled                                                                     |             |

|      |          | 1 Instruction Cache is Enabled                                                                      |             |

| 27   | FSL      | FSL Error                                                                                           | 0           |

|      |          | 0 FSL get/put had no error                                                                          |             |

|      |          | 1 FSL get/put had mismatch in instruction type and value type                                       |             |

| 28   | BIP      | Break in Progress                                                                                   | 0           |

|      |          | 0 No Break in Progress<br>1 Break in Progress                                                       |             |

|      |          | Source of break can be software break instruction or hardware break from Ext_Brk or Ext_NM_Brk pin. |             |

Table 1-5: Machine Status Register (MSR) (Continued)

| Bits | Name | Description                                                               | Reset Value |

|------|------|---------------------------------------------------------------------------|-------------|

| 29   | С    | Arithmetic Carry                                                          | 0           |

|      |      | 0 No Carry (Borrow)<br>1 Carry (No Borrow)                                |             |

| 30   | IE   | Interrupt Enable                                                          | 0           |

|      |      | 0 Interrupts disabled<br>1 Interrupts enabled                             |             |

| 31   | BE   | Buslock Enable                                                            | 0           |

|      |      | 0 Buslock disabled on data-side OPB<br>1 Buslock enabled on data-side OPB |             |

|      |      | Buslock Enable does not affect operation of ILMB, DLMB, or IOPB.          |             |

# **Pipeline**

This section describes the MicroBlaze pipeline architecture.

# Pipeline Architecture

The MicroBlaze pipeline is a parallel pipeline, divided into three stages:

- Fetch

- Decode

- Execute

In general, each stage takes one clock cycle to complete. Consequently, it takes three clock cycles (ignoring any delays or stalls) for the instruction to complete.

| cycle 1 | cycle 2 | cycle 3 |

|---------|---------|---------|

| Fetch   | Decode  | Execute |

In the MicroBlaze parallel pipeline, each stage is active on each clock cycle. Three instructions can be executed simultaneously, one at each of the three pipeline stages. Even though it takes three clock cycles for each instruction to complete, each pipeline stage can work on other instructions in parallel with and in advance of the instruction that is completing. Within one clock cycle, one new instruction is fetched, another is decoded, and a third is completed. The pipeline effectively completes one instruction per clock cycle.

|               | cycle 1 | cycle 2 | cycle 3 | cycle4  | cycle5  |

|---------------|---------|---------|---------|---------|---------|

| instruction 1 | Fetch   | Decode  | Execute |         |         |

| instruction 2 |         | Fetch   | Decode  | Execute |         |

| instruction 3 | ·       |         | Fetch   | Decode  | Execute |

#### **Branches**

Similar to other processor pipelines, the MicroBlaze pipeline can originate control hazards that affect the pipeline execution rate. When an instruction that changes the control flow of a program (branches) is executed and completed, and eventually changes the program flow (taken branches), the previous pipeline work becomes useless. When the processor executes a taken branch, the instructions in the fetch and decode stages are not the correct ones, and must be discarded or flushed from the pipeline. The processor must refill the pipeline with the correct instructions, taking three clock cycles for a taken branch, adding a latency of two cycles for refilling the pipeline.

MicroBlaze uses two techniques to reduce the penalty of taken branches. One technique is to use delay slots and another is use of a history buffer.

#### **Delay Slots**

When the processor executes a taken branch and flushes the pipeline, it takes three clock cycles to refill the pipeline. By allowing the instruction following a branch to complete, this penalty is reduced. Instead of flushing the instructions in both the fetch and decode stages, only the fetch stage is discarded and the instruction in the decode stage is allowed to complete. This effectively produces a delayed branch or delay slot. Since the work done on the delay slot instruction is not discarded, this technique effectively reduces the branch penalty from two clock cycles to one. Branch instructions that allow execution of the subsequent instruction in the delay slot are denoted by a D in the instruction mnemonic. For example, the BNE instruction does not execute the subsequent instruction in the delay slot, whereas BNED does execute the next instruction in the delay slot before control is transferred to the branch location.

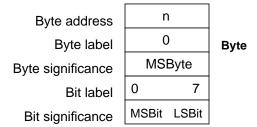

# **Load/Store Architecture**

MicroBlaze can access memory in the following three data sizes:

- Byte (8 bits)

- Halfword (16 bits)

- Word (32 bits)

Memory accesses are always data-size aligned. For halfword accesses, the least significant address bit is forced to 0. Similarly, for word accesses, the two least significant address bits are forced to 0.

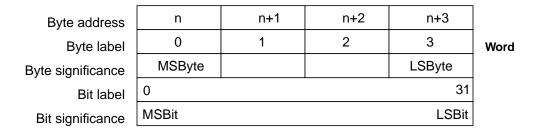

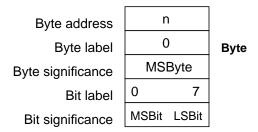

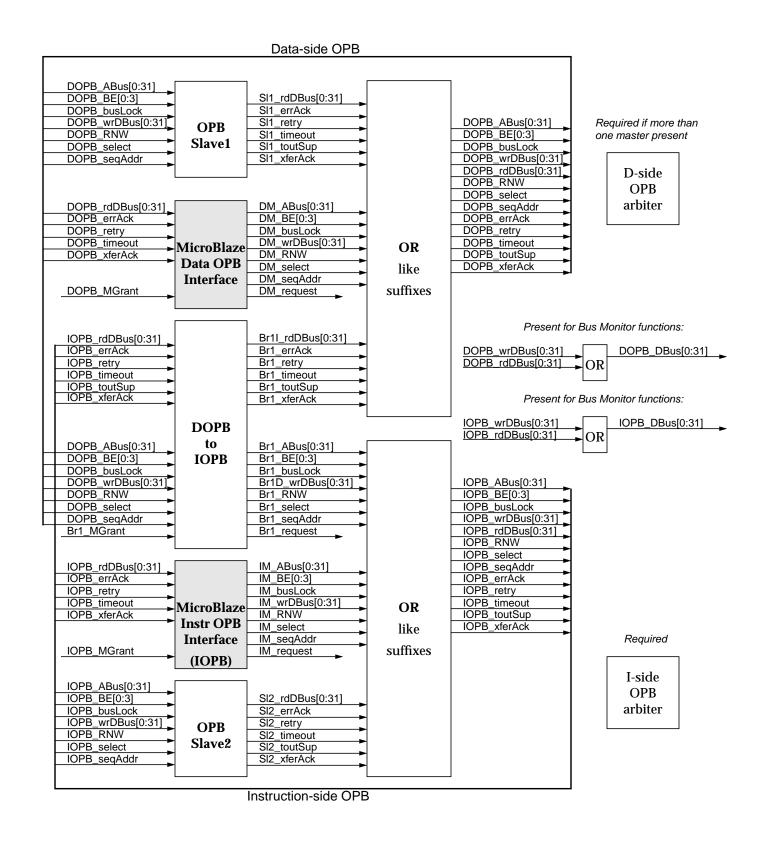

MicroBlaze is a Big-Endian processor and uses the Big-Endian address and labeling conventions shown in Figure 1-5 when accessing memory. The following abbreviations are used:

MSByte: Most Significant Byte

LSByte: Least Significant Byte

MSBit: Most Significant Bit

LSBit: Least Significant Bit

| Byte address      | n      | n+1 | n+2 | n+3    | l    |

|-------------------|--------|-----|-----|--------|------|

| Byte label        | 0      | 1   | 2   | 3      | Word |

| Byte significance | MSByte |     |     | LSByte | İ    |

| Bit label         | 0      |     |     | 31     |      |

| Bit significance  | MSBit  |     |     | LSBit  | l    |

| Byte address      | n      | n+1    |          |

|-------------------|--------|--------|----------|

| Byte label        | 0      | 1      | Halfword |

| Byte significance | MSByte | LSByte |          |

| Bit label         | 0      | 15     |          |

| Bit significance  | MSBit  | LSBit  |          |

Figure 1-5: Big-Endian Data Type

# Interrupts, Exceptions and Breaks

When a Reset or a Debug\_Rst occurs, MicroBlaze starts executing from address 0. PC and MSR are reset to the default values. When an Ext\_Brk occurs, MicroBlaze starts executing from address 0x18 and stores the return address in register 16. An Ext\_Brk is not executed if the BIP bit in MSR is active (equal to 1). When an Ext\_NM\_Brk occurs, MicroBlaze starts executing from address 0x18 and stores the return address in register 16. This occurs independent of the BIP bit value in MSR.

# Interrupts

When an interrupt occurs, MicroBlaze stops the current execution to handle the interrupt request. MicroBlaze branches to address 0x00000010 and uses the General Purpose Register 14 to store the address of the instruction that was to be executed when the interrupt occurred. It also disables future interrupts by clearing the Interrupt Enable flag in the Machine Status Register (setting bit 30 to 0 in MSR). The instruction located at the address where the current PC points to is not executed. Interrupts do not occur if the BIP bit in the MSR register is active (equal to 1).

#### Latency

The time it will take MicroBlaze to enter an Interrupt Service Routine (ISR) from the time an interrupt occurs, depends on the configuration of the processor. If MicroBlaze is configured to have a hardware divider, the largest latency will happen when an interrupt occurs during the execuion of a division instruction.

Table 1-6 shows the different scenarios for interrupts. The cycle count includes the cycles for completing the current instruction, the cycles for to branch and the cycles to access the first instruction in the ISR.

Table 1-6: Interrupt latencies

| Scenario                            | ISR in LMB | ISR in OPB |

|-------------------------------------|------------|------------|

| Normally                            | 4 cycles   | 6 cycles   |

| Worst case without hardware divider | 6 cycles   | 8 cycles   |

| Worst case with hardware divider    | 38 cycles  | 40 cycles  |

#### Equivalent Pseudocode

```

r14 \leftarrow PC

PC \leftarrow 0x00000010

MSR[IE] \leftarrow 0

```

# **Exceptions**

When an exception occurs, MicroBlaze stops the current execution to handle the exception. MicroBlaze branches to address 0x00000008 and uses the General Purpose Register 17 to store the address of the instruction that was to be executed when the exception occurred. The instruction located at the address where the current PC points to is not executed.

#### Equivalent Pseudocode

$$r17 \leftarrow PC$$

$PC \leftarrow 0x00000008$

#### **Breaks**

There are two kinds of breaks:

- Software (internal) breaks

- Hardware (external) breaks

#### Software Breaks

To perform a software break, use the brk and brki instructions. Refer to the Instruction Set Architecture documentation for more information on software breaks.

#### Hardware Breaks

Hardware breaks are performed by asserting the external break signal. When a hardware break occurs, MicroBlaze stops the current execution to handle the break. MicroBlaze branches to address 0x00000018 and uses the General Purpose Register 16 to store the

address of the instruction that was to be executed when the break occurred. MicroBlaze also disables future breaks by setting the Break In Progress (BIP) flag in the Machine Status Register (setting bit 28 to 1 in MSR). The instruction located at the address where the current PC points to is not executed.

Hardware breaks are only handled when there is no break in progress (the Break In Progress flag is set to 0). The Break In Progress flag has higher precedence than the Interrupt Enabled flag. While no interrupts are handled when the Break In Progress flag is set, breaks that occur when interrupts are disabled are handled immediately. However, it is important to note that non-maskable hardware breaks are always handled immediately.

#### Equivalent Pseudocode

```

r16 \leftarrow PC

PC \leftarrow 0x00000018

MSR[BIP] \leftarrow 1

```

### **Instruction Cache**

#### Overview

MicroBlaze may be used with an optional instruction cache for improved performance when executing code that resides outside the LMB address range.

The instruction cache has the following features

- User selectable cacheable memory area

- Configurable cache size and tag size

- Individual cache line lock capability

- Cache on and off controlled using a new bit in the MSR register

- Instructions to write to the instruction cache

- Does not require special memory controllers. Will work with existing OPB peripherals

- Memory is organized into a cacheable and a non-cacheable segment

- Very little area or frequency impact ( < 20 LUTs)</li>

- Can be used in conjunction with Instruction side LMB

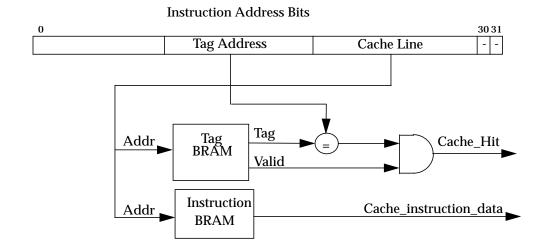

# Cache Organization

When the instruction cache is used, the memory address space in split into two segments - a cacheable segment and a non-cacheable segment. The cacheable segment is determined by two parameters, C\_ICACHE\_BASEADDR and C\_ICACHE\_HIGHADDR. All addresses within this range correspond to the cacheable address space segment. All other addresses are non-cacheable.

Figure 1-6: Cache Organization

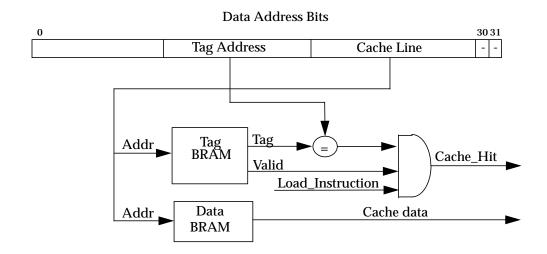

All cacheable instruction addresses are further split into two segments - a cache line segment and a tag address segment. The size of the two segments can be configured by the user. The address bits between bit 0 and the first tag address bit are ignored in the cache. The size of the cache line can be between 9 to 14 bits. This results in a cache sizes ranging from 4 Kbytes to 64 Kbytes. There is no limit on the tag address size.

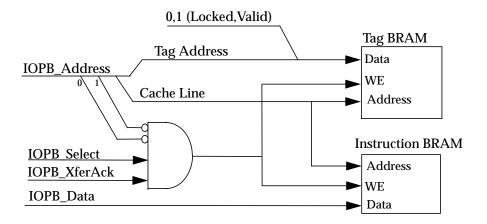

## **Cache Operation**

In the instruction fetch stage, MicroBlaze writes the instruction address to the instruction address bus and waits for a ready signal. To reduce wait states, a request is done simultaneously on the instruction OPB and the instruction LMB. If an acknowledge signal is received from the LMB in the next cycle, the instruction access from OPB is aborted. For every instruction fetched, the instruction cache detects if the instruction address belongs to the cacheable segment. If the address is non-cacheable, the cache ignores the instruction and allows the LMB or the OPB to fulfill the request. If the address is cacheable, a lookup is performed on the tag memory to check if the requested instruction is in the cache. The lookup is successful when both the valid bit is set and the tag address is the same as the tag address segment of the instruction address.

Figure 1-7: Cache Operation

If the instruction is in the cache, the cache will drive the ready signal (Cache\_Hit) for MicroBlaze and the instruction data for the address. If the instruction is not in the cache, the cache will not drive the ready signal but will wait until the OPB fulfills the request and updates the cache with the new information.

#### Software

#### MSR Bit

Bit 26 in the MSR indicates whether or not the cache is enabled. The MFS and MTS instructions are used to read and write to the MSR respectively.

The contents of the cache are preserved by default when the cache is disabled. The user may overwrite the contents of the cache using the WIC instruction or using the hardware debug logic of MicroBlaze.

#### **WIC Instruction**

The WIC instruction may be used to update the instruction cache from a software program. The assembly instruction is

WIC Ra, Rb

Where Ra contains cache line, tag address, valid and lock bit, Rb contains the instruction data.

Ra(31) is the lock bit, Ra(30) is the valid bit (valid when bit is set to '1'), the rest of the Ra contains the instruction address.

This instruction can only be used when the cache is disabled. The lock bit is described in the Lock Bit section below. The

#### **HW Debug Logic**

The HW debug logic may be used to perform a similar operation as the WIC instruction.

#### Lock Bit

The lock bit can be used to permanently lock a code segment into the cache and therefore guarantee the instruction execution time. Locking of the cacheline however may result in a decrease in the number of cache hits. This is because there could be addresses that were not cached as the cacheline is locked.

The use of instruction LMB in most cases would be a better choice for locking code segments since the wait states for accessing the LMB is the same as for cache hits.

### LMB Memory

Instruction LMB memory can be used even when instruction cache is used. The LMB address in the case has to be in the non-cacheable memory segment.

## **Data Cache**

#### Overview

MicroBlaze may be used with an optional data cache for improved performance when reading data that resides outside the LMB address range.

The data cache has the following features

- Write-through data cache

- User selectable cacheable memory area

- Configurable cache size and tag size

- Individual cache line lock capability

- Cache on and off controlled using a new bit in the MSR register

- Instructions to write to the data cache

- Does not require special memory controllers. Will work with existing OPB peripherals

- Memory is organized into a cacheable and a non-cacheable segments

- Very little area or frequency impact ( < 20 LUTs)

- Can be used in conjunction with Data side LMB

# **Cache Organization**

When the data cache is used, the memory address space in split into two segments - a cacheable segment and a non-cacheable segment. The cacheable area is determined by two parameters, C\_DCACHE\_BASEADDR and C\_DCACHE\_HIGHADDR. All addresses within this range correspond to the cacheable address space segment. All other addresses are non-cacheable.

Figure 1-8: Cache Organization

All cacheable data addresses are further split into two segments - a cache line segment and a tag address segment. The size of the two segments can be configured by the user. The address bits between bit 0 and the first tag address bit are ignored in the cache. The size of the cache line can be between 9 to 14 bits. This results in a cache sizes ranging from 4 Kbytes to 64 Kbytes. There is no limit on the tag address size.

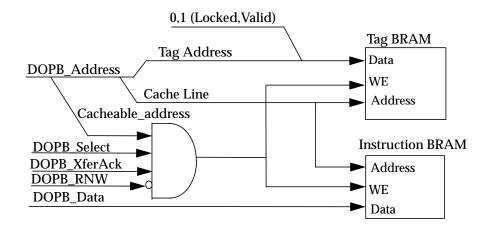

## **Cache Operation**

When MicroBlaze executes a store instruction, the operation is performed as normal but if the address is within the cacheable address segment, the data cache is updated with the new data.

When MicroBlaze executes a load instruction, the address is first checked to see if the address is within the cacheable area and secondly if the address is in the data cache. If that case, the data is fetch from the data cache.

Figure 1-9: Cache Operation

If the read data is in the cache, the cache will drive the ready signal (Cache\_Hit) for MicroBlaze and the data for the address. If the read data is not in the cache, the cache will not drive the ready signal but will wait until the OPB fulfills the request.

#### Software

#### MSR Bit

Bit 24 in the MSR indicates whether or not the cache is enabled. The MFS and MTS instructions are used to read and write to the MSR respectively.

The contents of the cache are preserved by default when the cache is disabled. The user may overwrite the contents of the cache using the WDC instruction or using the hardware debug logic of MicroBlaze.

Note: The cache cannot be turned on/off from an interrupt handler routine as the changes to the MSR is lost once the interrupt is handled (the MSR state is restored after interrupt handling).

#### **WDC** Instruction

The WDC instruction may be used to update the data cache from a software program. The assembly instruction is

```

WDC Ra, Rb

```

Where Ra contains cache line, tag address, valid and lock bit, Rb contains the data.

Ra(31) is the lock bit, Ra(30) is the valid bit (valid when bit is set to '1'), the rest of the Ra contains the instruction address.

This instruction can only be used when the cache is disabled. The lock bit is described in the Lock Bit section below. The

#### **HW Debug Logic**

The HW debug logic may be used to perform a similar operation as the WDC instruction.

#### Lock Bit

The lock bit can be used to permanently lock a code segment into the cache and therefore guarantee that this data is always in the cache. Locking of the cacheline however may result in a decrease in the number of cache hits. This is because there could be addresses that were not cached as the cacheline is locked.

The use of data LMB in most cases would be a better choice for locking data since the wait states for accessing the LMB is the same as for cache hits.

# LMB Memory

Data LMB memory can be used even when data cache is used. The LMB address in the case has to be in the non-cacheable memory segment.

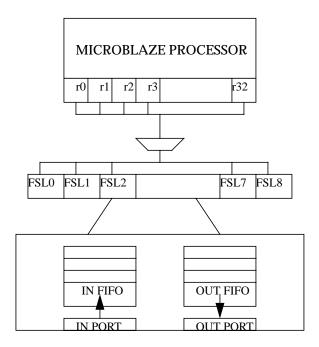

# Fast Simplex Link Interface

MicroBlaze contains eight input and eight output Fast Simplex Link (FSL) interfaces. For detailed information on the FSL interface, please refer to the FSL Bus documentation. The

FSL channels are dedicated uni-directional point-to-point data streaming interfaces. The FSL interfaces on MicroBlaze are 32 bits wide. Further, the same FSL channels can be used to transmit or receive either control or data words. A separate bit indicates whether the trasmitted (received) word is control or data information.

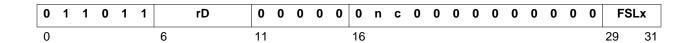

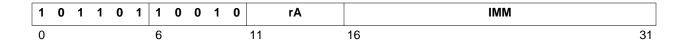

#### **FSL Read Instructions**

The Get instructions are used for reading data or control from an input FSL channel into a MicroBlaze register. There are 4 types of get instructions.

#### **Blocking Data Get Instruction**

The assembly instruction to perform a blocking get is

```

get regM, fslN

```

The blocking get instruction stalls the MicroBlaze pipeline until data becomes available in the input FSL, fslN. Once the data is available, the instruction is completed in two clock cycles. The get instruction is used for getting Data values. If a get instruction is used to read a Control value (the control\_in bit of the fslN is set), a FSL get error bit is set in the MSR (Bit 27).

#### Non-blocking Data Get Instruction

The assembly instruction to perform a non-blocking get is

```

nget regM, fslN

```

The non-blocking get instruction does not stall the MicroBlaze pipeline whether or not data is present on the input FSL, fslN. The instruction is completed in two clock cycles. If the data is available, the carry bit (Bit 29)in the MSR is reset. If the instruction fails the carry bit in the MSR is set. Bit 0 of the MSR has the copy of the carry bit. Hence, a direct branch on carry may be performed following the nget instruction. The nget instruction is also used to read Data values. If a Control value is read, the FSL error bit (Bit 27 of MSR) is set.

### **Blocking Control Get Instruction**

The assembly instruction to perform a blocking control get is

```

cget regM, fslN

```

The blocking control get instruction stalls the MicroBlaze pipeline until data becomes available in the input FSL, fslN. Once the data is available, the instruction is completed in two clock cycles. The cget instruction is used for reading Control values (the control\_in bit of the fslN is set). If the value read is a data value, the FSL error bit (Bit 27 of MSR) is set.

#### Non-blocking Control Get Instruction

The assembly instruction to perform a non-blocking get is

```

ncget regM, fslN

```

The non-blocking control get instruction does not stall the MicroBlaze pipeline whether or not data is present on the input FSL, fslN. The instruction is completed in two clock cycles. If the data is available, the carry bit (Bit 29) in the MSR is reset. If the instruction fails the carry bit in the MSR is set. Bit 0 of the MSR has the copy of the carry bit. Hence, a direct branch on carry may be performed following the neget instruction. The neget instruction is also used to read Control values (the control\_in bit of the fslN is set). If the value read is a data value, the FSL error bit (Bit 27 of the MSR) is set.

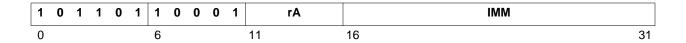

#### **FSL Write Instructions**

The Put instructions are used for writing data or control to an output FSL channel into a MicroBlaze register. There are 4 types of put instructions.

#### **Blocking Data Put Instruction**

The assembly instruction to perform a blocking put is

```

put regM, fslN

```

The blocking put instruction stalls the MicroBlaze pipeline until a data can be written to the output FSL, fslN (data can be written when the full bit is not set). Once the data can be written, the instruction is completed in two clock cycles. The put instruction is used for writing Data values (the control\_out bit of the fslN is reset).

#### Non-blocking Data Put Instruction

The assembly instruction to perform a non-blocking put is

```

nput regM, fslN

```

The non-blocking put instruction does not stall the MicroBlaze pipeline whether or not data can be written to the output FSL, fslN (data can be written when the full bit is not set). The instruction is completed in two clock cycles. If the data write succeeds, the carry bit (Bit 29) in the MSR is reset. If the data write fails, the carry bit in the MSR is set. Bit 0 of the MSR has the copy of the carry bit. Hence, a direct branch on carry may be performed following the nput instruction. The nput instruction is also used to write Data values (the control\_out bit of fslN is reset).

### **Blocking Control Put Instruction**

The assembly instruction to perform a blocking control put is

```

cput regM, fslN

```

The blocking put instruction stalls the MicroBlaze pipeline until a data can be written to the output FSL, fslN (data can be written when the full bit is not set). Once the data can be written, the instruction is completed in two clock cycles. The put instruction is used for writing Control values (the control\_out bit of the fslN is set).

#### Non-blocking Data Put Instruction

The assembly instruction to perform a non-blocking control put is

```

ncput regM, fslN

```

The non-blocking put instruction does not stall the MicroBlaze pipeline whether or not data can be written to the output FSL, fslN (data can be written when the full bit is not set). The instruction is completed in two clock cycles. If the data write succeeds, the carry bit (Bit 29) in the MSR is reset. If the data write fails, the carry bit in the MSR is set. Bit 0 of the MSR has the copy of the carry bit. Hence, a direct branch on carry may be performed following the nput instruction. The nput instruction is also used to write Control values (the control\_out bit of fslN is set).

# **Debug Interface**

MicroBlaze features a debug interface to support JTAG based software debugging tools (commonly known as BDM or Background Debug Mode debuggers) like the Xilinx

Microprocessor Debug (XMD) tool. The debug interface is designed to be connected to the Xilinx Microprocessor Debug Module (MDM) IP core, which interfaces with the JTAG port of Xilinx FPGAs. Multiple MicroBlazes can be interfaced with a single MDM to enable multiprocessor debugging.

# **Debugging Features**

- Configurable number of hardware breakpoints and watchpoints and unlimited software breakpoints

- External processor control enables debug tools to stop, reset and single step MicroBlaze

- Read and write memory and all registers including PC and MSR

- Support for multiple processors

- Write to Instruction and data cache

# MicroBlaze Bus Interfaces

# **Summary**

This document describes the MicroBlaze  $^{\text{\tiny TM}}$  Local Memory Bus (LMB) and On-chip Peripheral Bus (OPB) interfaces.

### **Overview**

The MicroBlaze core is organized as a Harvard architecture with separate bus interface units for data accesses and instruction accesses. Each bus interface unit is further split into a Local Memory Bus (LMB) and IBM's On-chip Peripheral Bus (OPB). The LMB provides single-cycle access to on-chip dual-port block RAM. The OPB interface provides a connection to both on-and off-chip peripherals and memory. Further, the MicroBlaze core provides 8 input and 8 output interfaces to Fast Simplex Link (FSL) buses. The FSL buses are uni-directional non-arbitrated dedicated communication channels.

#### **Features**

The MicroBlaze bus interfaces include the following features:

- OPB V2.0 bus interface with byte-enable support (see IBM's 64-Bit On-Chip Peripheral Bus, Architectural Specifications, Version 2.0)

- LMB provides simple synchronous protocol for efficient block RAM transfers

- LMB provides guaranteed performance of 125 MHz for local memory subsystem

- FSL provides a fast non-arbitrated streaming communication mechanism.

# **Bus Configurations**

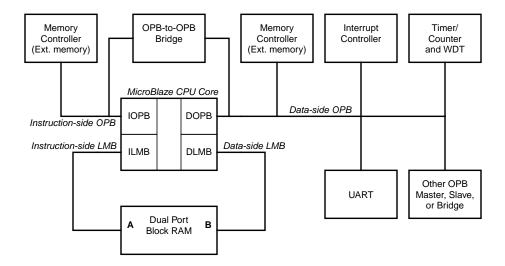

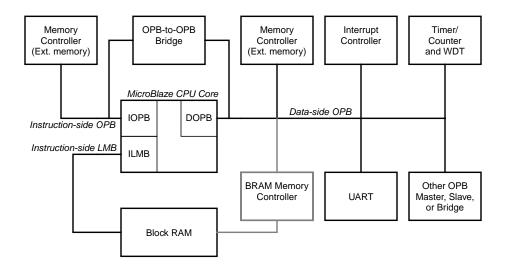

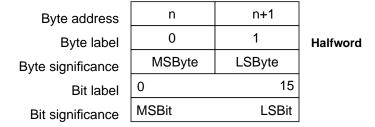

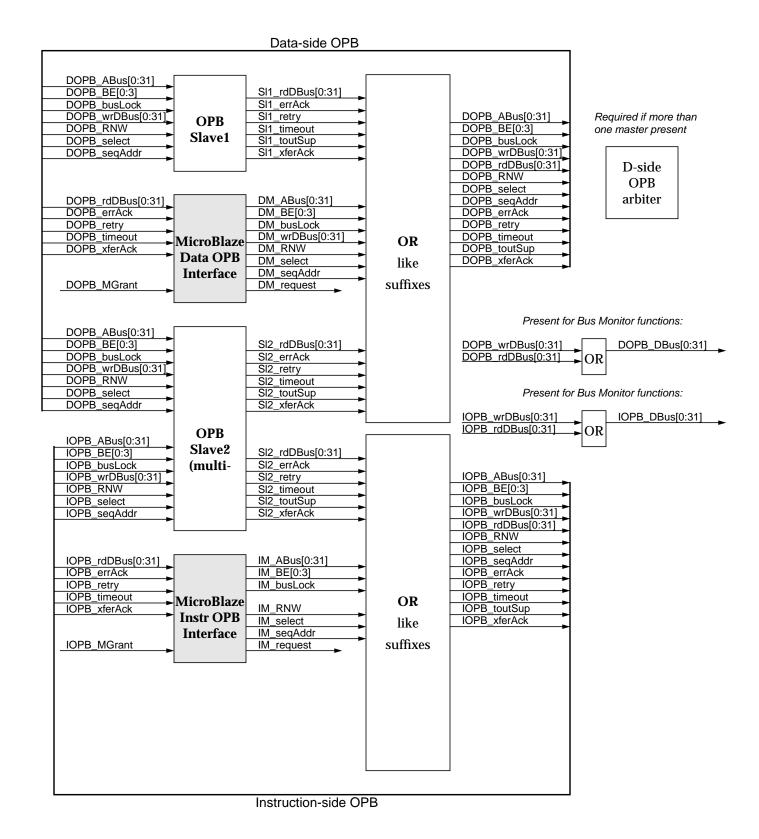

The block diagram in Figure 2-1 depicts the MicroBlaze core with the bus interfaces defined as follows:

DOPB: Data interface, On-chip Peripheral Bus

DLMB: Data interface, Local Memory Bus (BRAM only)

IOPB: Instruction interface, On-chip Peripheral Bus

ILMB: Instruction interface, Local Memory Bus (BRAM only)

MFSL0..MFSL7: Master data interface, Fast Simplex Link

SFSL0..SFSL7: Slave data interface, Fast Simplex Link

Core: Miscellaneous signals (Clock, Reset, Interrupt)

Figure 2-1: MicroBlaze Core Block Diagram

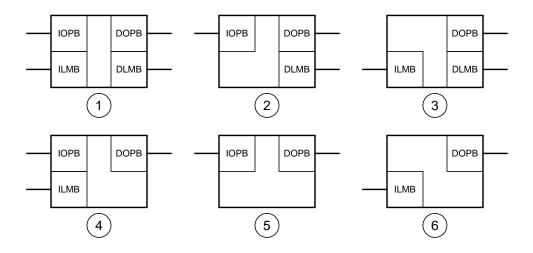

MicroBlaze bus interfaces are available in six configurations, as shown in the following figure.

NOTE: All the 6 configurations can be used along with the FSL bus configuration.

Figure 2-2: MicroBlaze Bus Configurations

The optimal configuration for your application depends on code size and data spaces, and if you require fast access to internal block RAM. The performance implications and supported memory models for each configuration is shown in the following table:

Table 2-1: MicroBlaze Bus Configurations

|   | Configuration       | Core<br>Fmax | Debug<br>available                                               | Memory Models Supported                                                                                                                  |

|---|---------------------|--------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| 1 | IOPB+ILMB+DOPB+DLMB | 110          | SW/JTAG                                                          | Large external instruction memory, Fast internal instruction memory (BRAM), Large external data memory, Fast internal data memory (BRAM) |

| 2 | IOPB+DOPB+DLMB      | 125          | SW/JTAG                                                          | Large external instruction memory,<br>Large external data memory,<br>Fast internal data memory (BRAM)                                    |

| 3 | ILMB+DOPB+DLMB      | 125          | SW/JTAG                                                          | Fast internal instruction memory (BRAM),<br>Large external data memory,<br>Fast internal data memory (BRAM)                              |

| 4 | IOPB+ILMB+DOPB      | 110          | JTAG for<br>ILMB<br>memory <sup>1</sup><br>SW/for IOPB<br>memory | Large external instruction memory, Fast internal instruction memory (BRAM), Large external data memory,                                  |

| 5 | IOPB+DOPB           | 125          | SW/JTAG                                                          | Large external instruction memory,<br>Large external data memory,                                                                        |

| 6 | ILMB+DOPB           | 125          | JTAG <sup>1</sup>                                                | Fast internal instruction memory (BRAM),<br>Large external data memory,                                                                  |

**Note:** ILMB memory can be debugged via a software resident monitor if the second port of the dual-ported ILMB BRAM is connected to an OPB BRAM memory controller. See Figure 2-6 and Figure 2-8. Also, all the above 6 confugrations can be used with a special FSL configuration. See Figure 2-9.

# Typical Peripheral Placement

This section provides typical peripheral placement and usage for each of the six configurations and the FSL configuration. Because there are many options for interconnecting a MicroBlaze system, you should use the following examples as *guidelines* for selecting a configuration closest to your application.

#### Configuration 1

Figure 2-3: Configuration 1: IOPB+ILMB+DOPB+DLMB

#### **Purpose**

Use this configuration when your application requires more instruction and data memory than is available in the on-chip block RAM (BRAM). Critical sections of instruction and data memory can be allocated to the faster ILMB BRAM to improve your application's performance. Depending on how much data memory is required, the data-side memory controller may not be present. The data-side OPB is also used for other peripherals such as UARTs, timers, general purpose I/O, additional BRAM, and custom peripherals. The OPB-to-OPB bridge is only required if the data-side OPB needs access to the instruction-side OPB peripherals, such as for software-based debugging.

#### Typical Applications

- MPEG Decoder

- Communications Controller

- Complex state machine for process control and other embedded applications

- Set top boxes.

#### Characteristics

Because of the extra logic required to implement two buses per side, the maximum clock rate of the CPU may be slightly less than configurations with one bus per side. This configuration allows debugging of application code through either software-based debugging (resident monitor debugging) or hardware-based JTAG debugging.

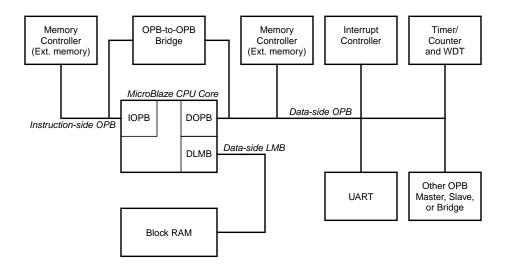

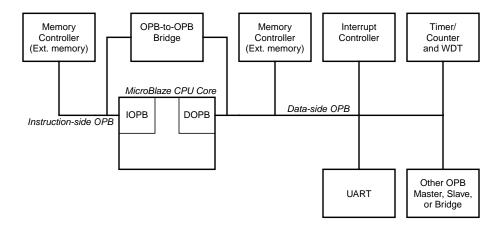

Figure 2-4: Configuration 2: IOPB+DOPB+DLMB

#### **Purpose**

Use this configuration when your application requires more instruction and data memory than is available in the on-chip BRAM. In this configuration, all of the instruction memory is resident in off-chip memory or on-chip memory on the instruction-side OPB. Depending on how much data memory is required, the data-side memory controller may not be present. The data-side OPB is also used for other peripherals such as UARTs, timers, general purpose I/O, additional BRAM, and custom peripherals. The OPB-to-OPB bridge is only required if the data-side OPB needs access to the instruction-side OPB peripherals, such as for software-based debugging.

#### Typical Applications

- MPEG Decoder

- Communications Controller

- Complex state machine for process control and other embedded applications

- Set top boxes.

#### Characteristics

This configuration allows the CPU core to operate at the maximum clock rate because of the simpler instruction-side bus structure. Instruction fetches on the OPB, however, are slower than fetches from BRAM on the LMB. Overall processor performance is lower than implementations using LMB unless a large percentage of code is run from the internal instruction history buffer. This configuration allows debugging of application code through either software-based debugging (resident monitor debugging) or hardware-based JTAG debugging.

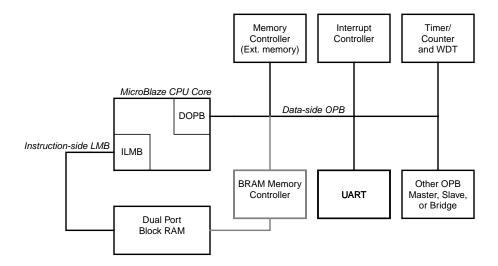

Figure 2-5: Configuration 3: ILMB+DOPB+DLMB

#### **Purpose**

Use this configuration when your application code fits into the on-chip BRAM, but more memory may be required for data memory. Critical sections of data memory can be allocated to the faster DLMB BRAM to improve your application's performance. Depending on how much data memory is required, the data-side memory controller may not be present. The data-side OPB is also used for other peripherals such as UARTs, timers, general purpose I/O, additional BRAM, and custom peripherals.

#### Typical Applications

- Data-intensive controllers

- Small to medium state machines

#### Characteristics

This configuration allows the CPU core to operate at the maximum clock rate because of the simpler instruction-side bus structure. The instruction-side LMB provides two-cycle pipelined read access from the BRAM for an effective access rate of one instruction per clock. This configuration allows debugging of application code through either software-based debugging (resident monitor debugging) or hardware-based JTAG debugging.

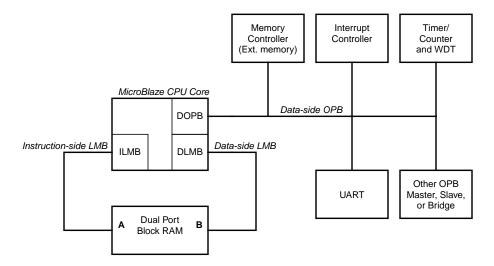

Figure 2-6: Configuration 4: IOPB+ILMB+DOPB

#### **Purpose**

Use this configuration when your application requires more instruction and data memory than is available in the on-chip BRAM. Critical sections of instruction memory can be allocated to the faster ILMB BRAM to improve your application's performance. The data-side OPB is used for one or more external memory controllers and other peripherals such as UARTs, timers, general purpose I/O, additional BRAM, and custom peripherals. The OPB-to-OPB bridge is only required if the data-side OPB needs access to the instruction-side OPB peripherals, such as for software-based debugging.

#### Typical Applications

- MPEG Decoder

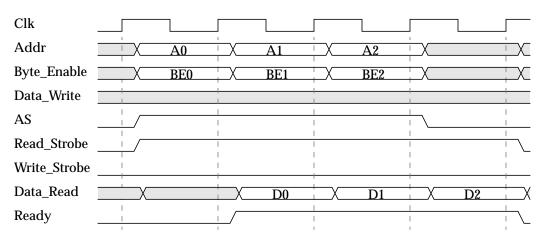

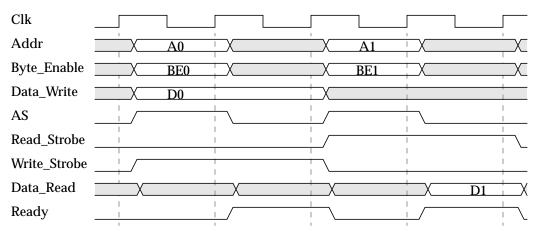

- Communications Controller